- •Этапы развития микропроцессорной техники.

- •Классификация микропроцессоров.

- •Виды обменов в микроЭвм.

- •Обмен по прямому доступу в память.

- •Обмен по прерыванию.

- •Микропроцессор 580вм80.

- •Intr – вход запроса прерывания.

- •Inta – сигнал подтверждения обработки прерывания. Он говорит о том, что микропроцессор начал обрабатывать прерывание. Обработки прерывания начинается на границе между двумя командами.

- •Синхронизация работы микропроцессора. Микросхема 580гф24.

- •Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

- •Построение разрядно-модульных микропроцессоров.

- •Микропроцессорная секция 1804вс1.

- •Микропроцессорный комплект бис 1815 для конвейерных систем цос.

- •Универсальный процессорный элемент 1815вф1.

- •Сумматор последовательных числе 1815им1.

- •Бис ортогональной регистровой памяти 1815ир1.

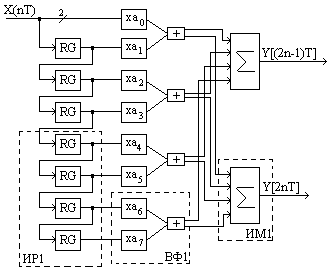

- •Цифровая фильтрация на микропроцессорном комплекте 1815.

- •Микропроцессор 1815 вф3.

- •Особенности реализации систем цос на бис 1815вф3.

- •Микропроцессор 1810вм86/88.

- •Inta – сигнал подтверждения прерывания.

- •Модель процессора 1810вм86 для программистов.

- •Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

- •Сопроцессор 1810вм87.

- •Системный контроллер 1810вг88.

- •Включение процессора 1810вм86 в максимальном режиме.

- •Арбитр шин 1810вб89.

- •Организация приоритетного арбитража.

- •2.На системной магистрали располагается память, на резидентной магистрали только увв.

- •Программируемый контроллер прерываний 1810вн59.

- •Контроллер пдп 1810вт37.

- •Процессоры 2, 3 и 4 – ого поколения.

- •Процессор 80386.

Сумматор последовательных числе 1815им1.

Микросхема ИМ1 осуществляет суммирование до 8-ми слов неограниченной длины, представленных в модифицированном дополнительном коде, т.е. сигналов поступающих с выхода микросхемы ВФ1. Суммирование слов неограниченной длины становится возможным из-за применения дополнительного кода, в котором знаковый разряд обрабатывается также, кок и цифровые разряды.

Схема

содержит 7 сумматоров, объединённых в

3 ступени. Каждый сумматор является 2-х

входовым, 2-х разрядным устройством. Все

сумматоры имеют одинаковую схему.

Обработка информации производится по

тактовым сигналам SYN.

Сигналы CSI

синхронизируют передачу знаковых

разрядов. Предполагается, что входная

и выходная информация является числами

с фиксированной запятой меньшими 1. При

сложении нескольких чисел возможно

переполнение. Чтобы этого не происходило

в схеме производится автоматической

выравнивание чисел на 2 или 3 разряда.

Переключением между выравниванием на

2 или 3 разряда управляет сигнал МО. При

выравнивании происходит сдвиг чисел

на 2 или 3 разряда в сторону младших

разрядов. Это выравнивание необходимо

учитывать при ручном масштабировании

результатов. Т.е. схема работает с числами

как с правильными дробями, т.е. меньшими

1.

Схема

содержит 7 сумматоров, объединённых в

3 ступени. Каждый сумматор является 2-х

входовым, 2-х разрядным устройством. Все

сумматоры имеют одинаковую схему.

Обработка информации производится по

тактовым сигналам SYN.

Сигналы CSI

синхронизируют передачу знаковых

разрядов. Предполагается, что входная

и выходная информация является числами

с фиксированной запятой меньшими 1. При

сложении нескольких чисел возможно

переполнение. Чтобы этого не происходило

в схеме производится автоматической

выравнивание чисел на 2 или 3 разряда.

Переключением между выравниванием на

2 или 3 разряда управляет сигнал МО. При

выравнивании происходит сдвиг чисел

на 2 или 3 разряда в сторону младших

разрядов. Это выравнивание необходимо

учитывать при ручном масштабировании

результатов. Т.е. схема работает с числами

как с правильными дробями, т.е. меньшими

1.

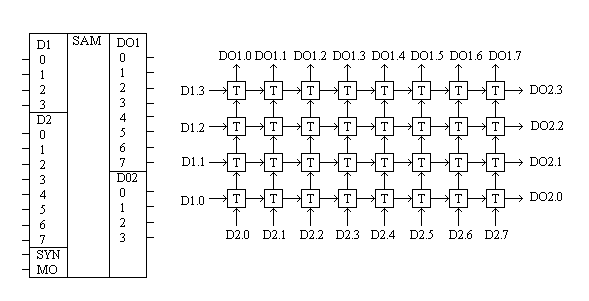

Режим со сдвигом на 2 разряда используется в том случае, когда количество входным операндов меньше или равно 4. При сдвиге на 3 разряда результат выдаётся с одним знаковым разрядом при сдвиге на 2 разряда результат выдаётся в двумя знаковыми разрядами.

На выходе DO1 всегда выдаются нечётные разряды, а на DO2 – чётные. Чтобы выполнялось данное правило как при выравнивании на 2 разряда, так и при выравнивании на 3 разряда в схему введён мультиплексор, которые осуществляет переключение разрядов между выходными шинами. Схема имеет задержку между входными и выходными данными на 8 тактов.

Бис ортогональной регистровой памяти 1815ир1.

Микросхема регистровой памяти представляет из себя матрицу памяти размером 8х4 или 4х8 и предназначена для задержки информации обрабатываемой микросхемами ВФ1 и ИМ1.

Информация продвигается вдоль регистров по тактам синхронизации SYN. Сигнал МО определяет направление передвижения. Схема имеет возможность обрабатывать 4-х разрядные и 8-ми разрядные слова. При этом в первом случае задержка составляет 8 тактов, во втором 4 такта. Основное назначение микросхемы – это задержка отсчётов 8-ми, 16 или 32-х разрядных слов в системе ЦОС построенных на микросхемах серии 1814. Микросхема выполнена по ТТЛШ технологии и имеет напряжение питания +5В.

Цифровая фильтрация на микропроцессорном комплекте 1815.

Математическая

работа цифрового фильтра описывается

разностным уравнением:

![]() х

– это отсчёты выходной переменной, аi

и bj

– весовые коэффициенты, именно они

определяют свойства фильтра. Если все

bj=0,

то фильтр называется не рекурсивным. В

противном случае – рекурсивный фильтр

(фильтр без памяти). Т – это период

выборки входного сигнала, n

– это размер выборки. Для функции y

введём понятие z

преобразования:

х

– это отсчёты выходной переменной, аi

и bj

– весовые коэффициенты, именно они

определяют свойства фильтра. Если все

bj=0,

то фильтр называется не рекурсивным. В

противном случае – рекурсивный фильтр

(фильтр без памяти). Т – это период

выборки входного сигнала, n

– это размер выборки. Для функции y

введём понятие z

преобразования:

![]() Точно также можно ввести это понятие

для х:

Точно также можно ввести это понятие

для х:

![]()

Передаточная

функция фильтра – это отношение z

преобразования выходной величины к z

преобразованию входной величины.

Данная

передаточная функция – это передаточная

функция рекурсивного фильтра.

Данная

передаточная функция – это передаточная

функция рекурсивного фильтра.

У

не рекурсивного фильтра:

![]() (все bj=0,

отсюда знаменатель равен 1). Умножение

на z-1

эквивалентно задержке на один отсчёт.

Передаточные функции фильтров не зависят

от формы входных и выходных сигналов.

(все bj=0,

отсюда знаменатель равен 1). Умножение

на z-1

эквивалентно задержке на один отсчёт.

Передаточные функции фильтров не зависят

от формы входных и выходных сигналов.

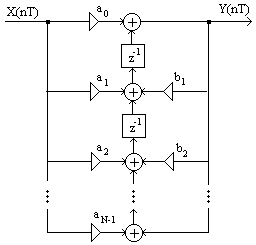

Возможны 3 способа реализации цифровых фильтров:

Прямой.

Каскадный или последовательный.

Параллельный.

П рямая

структура рекурсивного фильтра использует

выражение (**).

рямая

структура рекурсивного фильтра использует

выражение (**).

У не рекурсивного фильтра будет отсутствовать обратная связь. Возможно сокращение числа элементов задержки, если в приведённой схеме одни и те же элементы задержки z-1 использовать как для задержки отсчётов х, так и для задержки отсчётов у.

Съема рекурсивного фильтра в канонической форме.

В данном фильтре сократилось число элементов задержки. Вместо общего сумматора сумматор стал распределённым.

2.Каскадная

форма получается, если полиномы

располагающиеся в числителе и знаменателе

представить через их корни.

![]() Но

т.к. корни могут быть комплексными, то

будем представлять в виде:

Но

т.к. корни могут быть комплексными, то

будем представлять в виде:

![]()

![]() Данная

схема реализуется последовательным

включением звеньев с характеристикой

Данная

схема реализуется последовательным

включением звеньев с характеристикой

![]() HK(p)

– описывает передаточную функцию

биквадратного звена.

HK(p)

– описывает передаточную функцию

биквадратного звена.

3.Параллельная

структура. преобразуем уравнения (2) и

(3) к виду:

![]()

1 ,

2, …L2

– биквадратные звенья.

,

2, …L2

– биквадратные звенья.

Проанализируем прямую схему. Операция умножения на постоянные коэффициенты аi и bi в серии 1815 реализуется на микросхеме ВФ1. В случае 8-ми разрядных входных данных на этой же микросхеме производится и частичное суммирование. Суммирование осуществляется микросхемой ИМ1. Элементы задержки реализуются на регистровой схеме ИР1.

Пример: реализуем не рекурсивный фильтр 7-ого порядка. Будем считать, что входные данные 8-ми разрядные.