- •Часть I. Цепи, сигналы, электроника и схемотехника

- •Часть II. Практикум на Electronics Workbench

- •Глава 1. Электрические цепи Часть I. Цепи, сигналы, электроника и схемотехника

- •1. Электрические цепи

- •1.1. Ток, напряжение, мощность и энергия

- •1.1. Ток, напряжение, мощность и энергия

- •Глава 1. Электрические цепи

- •1.2. Элементы электрических цепей и их уравнения

- •1.2. Элементы электрических цепей и их уравнения

- •Глава 1. Электрические цепи нику напряжения при малых токах близки аккумуляторы, батареи, электрическая сеть 220 в/50 Гц. Идеальный источник тока — это элемент, генерирующий задан-

- •1.2. Элементы электрических цепей и их уравнения

- •Глава 1. Электрические цепи л . Емкость измеряется в фарадах (ф). В радиоэлектронике чаще ис-

- •1.2. Элементы электрических цепей и их уравнения

- •Глава 1. Электрические цепи Из анализа этой формулы следует, что условие передачи максиму-

- •1.3. Электрическая цепь и уравнения соединений

- •1.3. Электрическая цепь и уравнения соединений

- •Глава 1. Электрические цепи Контур цепи — это замкнутый путь из ветвей. Например, в цепи

- •1.3. Электрическая цепь и уравнения соединений

- •Глава 1. Электрические цепи

- •1.3. Электрическая цепь и уравнения соединений

- •Глава 1. Электрические цепи

- •2. Цепи при гармоническом воздействии

- •2.1. Гармоническое колебание и комплексная амплитуда

- •2.1. Гармоническое колебание и комплексная амплитуда

- •Глава 2. Цепи при гармоническом воздействии Комплексные амплитуды нескольких сигналов удобно изобразить

- •2.2. Уравнения элементов в комплексной форме

- •2.2. Уравнения элементов в комплексной форме

- •Глава 2. Цепи при гармоническом воздействии

- •2.2. Уравнения элементов в комплексной форме

- •Глава 2. Цепи при гармоническом воздействии

- •2.3. Уравнения соединений в комплексной форме

- •2.3. Уравнения соединений в комплексной форме

- •Глава 2. Цепи при гармоническом воздействии

- •2.3. Уравнения соединений в комплексной форме

- •Глава 2. Цепи при гармоническом воздействии

- •2.4, Мгновенная, активная, полная и реактивная мощности

- •2.4. Мгновенная, активная, полная и реактивная мощности

- •Глава 2. Цепи при гармоническом воздействии

- •2.4. Мгновенная, активная, полная и реактивная мощности

- •Глава 2. Цепи при гармоническом воздействии

- •Глава 3. Методы анализа сложных электрических цепей 3. Методы анализа сложных электрических цепей

- •3.1. Особенности анализа сложных цепей

- •3.2. Метод узловых напряжений

- •3.2. Метод узловых напряжений

- •Глава 3. Методы анализа сложных электрических цепей

- •3.2. Метод узловых напряжений

- •Глава 3. Методы анализа сложных электрических цепей

- •3.3. Метод контурных токов

- •3.3. Метод контурных токов

- •Глава 3. Методы анализа сложных электрических цепей Рассмотрим изменения, возникающие в уравнениях цепи, обуслов-

- •3.3. Метод контурных токов

- •Глава 3. Методы анализа сложных электрических цепей

- •3.4. Свойства линейных цепей

- •3.4. Свойства линейных цепей

- •Глава 3. Методы анализа сложных электрических цепей

- •3.4. Свойства линейных цепей

- •Глава 3. Методы анализа сложных электрических цепей

- •3.4. Свойства линейных цепей

- •Глава 3. Методы анализа сложных электрических цепей

- •Глава 4. Четырехполюсники, фильтры и длинные линии 4. Четырехполюсники, фильтры и длинные линии

- •4.1. Четырехполюсники

- •4.1. Четырехполюсники

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.1. Четырехполюсники

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.1. Четырехполюсники

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.2. Электрические фильтры

- •4.2. Электрические фильтры

- •Глава 4. Четырехполюсники, фильтры и длинные линии Кроме ачх для описания фильтра используют фазочастотную ха-

- •4.2. Электрические фильтры

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.2. Электрические фильтры

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.2. Электрические фильтры

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.3. Длинные линии и телеграфные уравнения

- •4.3. Длинные линии и телеграфные уравнения

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.3. Длинные линии и телеграфные уравнения

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.3. Длинные линии и телеграфные уравнения

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.4. Коэффициент отражения, стоячие и смешанные волны

- •4.4. Коэффициент отражения, стоячие и смешанные волны

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •4.4. Коэффициент отражения, стоячие и смешанные волны

- •Глава 4. Четырехполюсники, фильтры и длинные линии

- •Глава 4. Четырехполюсники, фильтры и длинные линии 7. Используя частотные свойства конденсатора и катушки индуктивности, объяснить работу фнч т-типа.

- •5.1. Линейные пространства и понятие спектра сигнала

- •5. Сигналы и их спектры

- •5.1. Линейные пространства и понятие спектра сигнала

- •Глава 5. Сигналы и их спектры

- •5.1. Линейные пространства и понятие спектра сигнала

- •Глава 5. Сигналы и их спектры

- •5.1. Линейные пространства и понятие спектра сигнала

- •Глава 5. Сигналы и их спектры

- •5.2. Спектр периодического сигнала

- •5.2. Спектр периодического сигнала

- •Глава 5. Сигналы и их спектры

- •5.2. Спектр периодического сигнала

- •Глава 5. Сигналы и их спектры

- •5.3. Спектр непериодического сигнала и преобразование

- •Глава 5. Сигналы и их спектры

- •Глава 5. Сигналы и их спектры

- •Глава 5. Сигналы и их спектры

- •Глава 5. Сигналы и их спектры

- •Глава 5. Сигналы и их спектры Например, из первой теоремы следует, что при увеличении скоро-

- •5.4. Преобразование сигналов в линейной цепи

- •5.4. Преобразование сигналов в линейной цепи

- •Глава 5. Сигналы и их спектры

- •5.4. Преобразование сигналов в линейной цепи

- •Глава 5. Сигналы и их спектры Таким образом, для линейной цепи справедливы три уравнения

- •5.5. Модулированные сигналы и их спектры

- •5.5. Модулированные сигналы и их спектры

- •Глава 5. Сигналы и их спектры

- •5.5. Модулированные сигналы и их спектры

- •Глава 5. Сигналы и их спектры

- •5.5. Модулированные сигналы и их спектры

- •Глава 5. Сигналы и их спектры

- •5.5. Модулированные сигналы и их спектры

- •Глава 5. Сигналы и их спектры

- •Глава 6. Полупроводниковые приборы 6. Полупроводниковые приборы 6.1. Электронно-дырочный переход и полупроводниковые диоды к полупроводникам относят материалы, проводимость которых

- •Глава 6. Полупроводниковые приборы установившемся состоянии диффузионный ток будет равен дрейфо- вому току. Пусть к р-и-переходу подключен источник небольшого постоянно-

- •Глава 6. Полупроводниковые приборы

- •Глава 6. Полупроводниковые приборы

- •Глава 6. Полупроводниковые приборы Импульсные диоды предназначены для работы с быстро изменяю-

- •6.2. Биполярные транзисторы

- •6.2. Биполярные транзисторы

- •Глава 6. Полупроводниковые приборы

- •6.2. Биполярные транзисторы

- •Глава 6. Полупроводниковые приборы

- •6.2. Биполярные транзисторы

- •Глава 6. Полупроводниковые приборы

- •6.3. Полевые транзисторы

- •6.3. Полевые транзисторы

- •Глава 6. Полупроводниковые приборы

- •6.3. Полевые транзисторы

- •Глава 6. Полупроводниковые приборы

- •6.3. Полевые транзисторы

- •Глава 6. Полупроводниковые приборы

- •Глава 6. Полупроводниковые приборы 7. Перечислите все разновидности биполярных и полевых транзисторов. При- ведите их условные обозначения.

- •7.1. Три основные схемы усилителей на транзисторах

- •7.1. Три основные схемы усилителей на транзисторах

- •Глава 7. Электронные усилители и преобразователи сигналов По режимам работы различают линейные и нелинейные усилители.

- •7.1. Три основные схемы усилителей на транзисторах

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.1. Три основные схемы усилителей на транзисторах

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.1. Три основные схемы усилителей на транзисторах

- •Глава 7. Электронные усилители и преобразователи сигналов 1 _l

- •7.2. Резистивный и резонансный усилители

- •7.2. Резистивный и резонансный усилители

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.2. Резистивный и резонансный усилители

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.2. Резистивный и резонансный усилители

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.3. Обратная связь в усилителях

- •7.3. Обратная связь в усилителях

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.3. Обратная связь в усилителях

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.3. Обратная связь в усилителях

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.4. Операционный усилитель и аналоговый перемножитель

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.4. Операционный усилитель и аналоговый перемножитель

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.4. Операционный усилитель и аналоговый перемножитель

- •Глава 7. Электронные усилители и преобразователи сигналов

- •7.4. Операционный усилитель и аналоговый перемножитель

- •Глава 7. Электронные усилители и преобразователи сигналов

- •Глава 7. Электронные усилители и преобразователи сигналов

- •8. Нелинейные преобразования сигналов

- •8.1. Нелинейный элемент и воздействие на него одного

- •Глава 8. Нелинейные преобразования сигналов

- •Глава 8. Нелинейные преобразования сигналов

- •8.2. Воздействие на нелинейный элемент двух сигналов

- •8.2. Воздействие на нелинейный элемент двух сигналов

- •Глава 8. Нелинейные преобразования сигналов

- •8.2. Воздействие на нелинейный элемент двух сигналов

- •Глава 8. Нелинейные преобразования сигналов

- •8.2. Воздействие на нелинейный элемент двух сигналов

- •Глава 8. Нелинейные преобразования сигналов

- •8.3. Автогенераторы гармонических колебаний

- •8.3. Автогенераторы гармонических колебаний

- •Глава 8. Нелинейные преобразования сигналов

- •8.3. Автогенераторы гармонических колебаний

- •Глава 8. Нелинейные преобразования сигналов

- •8.3. Автогенераторы гармонических колебаний

- •Глава 8. Нелинейные преобразования сигналов

- •8.4. Стационарный режим автогенератора

- •8.4. Стационарный режим автогенератора

- •Глава 8. Нелинейные преобразования сигналов Из анализа уравнения баланса фаз (3) следует, что в автогенерато-

- •8.4. Стационарный режим автогенератора

- •Глава 8. Нелинейные преобразования сигналов Для генерации последовательности прямоугольных импульсов ис-

- •Глава 8. Нелинейные преобразования сигналов 4. Рассчитайте амплитуду напряжения на выходе умножителя частоты в два раза, выполненного на аналоговом перемножителе, если коэффициент k пе-

- •Глава 9. Импульсные и цифровые устройства 9. Импульсные и цифровые устройства 9.1. Импульсные сигналы и электронный ключ в предыдущих главах рассматривались аналоговые сигналы: по-

- •9.1. Импульсные сигналы и электронный ключ

- •Глава 9. Импульсные и цифровые устройства

- •9.1. Импульсные сигналы и электронный ключ

- •Глава 9. Импульсные и цифровые устройства

- •9.2. Базовые логические элементы

- •9.2. Базовые логические элементы

- •Глава 9. Импульсные и цифровые устройства Рассмотрим работу схемы ттл-элемента при подаче различных

- •9.2. Базовые логические элементы

- •Глава 9. Импульсные и цифровые устройства

- •9.2. Базовые логические элементы

- •Глава 9. Импульсные и цифровые устройства

- •9.3. Комбинационные устройства

- •9.3. Комбинационные устройства

- •Глава 9. Импульсные и цифровые устройства

- •9.3. Комбинационные устройства

- •Глава 9. Импульсные и цифровые устройства Комбинационная схема, выполняющая арифметическое сложение

- •9.3. Комбинационные устройства

- •Глава 9. Импульсные и цифровые устройства

- •9.4. Триггеры

- •9.4. Триггеры

- •9.4. Триггеры

- •Глава 9. Импульсные и цифровые устройства

- •9.5. Счетчики и регистры

- •9.5. Счетчики и регистры

- •Глава 9. Импульсные и цифровые устройства

- •9.5. Счетчики и регистры

- •Глава 9. Импульсные и цифровые устройства

- •Глава 10. Цифровая обработка сигналов 10. Цифровая обработка сигналов 10.1. Дискретизация и квантование Цифровая обработка сигналов (цос) — это преобразование фор-

- •10.1. Дискретизация и квантование

- •Глава 10. Цифровая обработка сигналов

- •10.1. Дискретизация и квантование

- •Глава 10. Цифровая обработка сигналов

- •10.1. Дискретизация и квантование

- •Глава 10. Цифровая обработка сигналов

- •10.2. Аналого-цифровые и цифро-аналоговые

- •Глава 10. Цифровая обработка сигналов

- •Глава 10. Цифровая обработка сигналов

- •10.3. Цифровые фильтры

- •10.3. Цифровые фильтры

- •Глава 10. Цифровая обработка сигналов На рис. 2 в качестве примера приведена схема цифрового фильтра

- •10.3. Цифровые фильтры

- •Глава 10. Цифровая обработка сигналов

- •10.4. Дискретное преобразование Фурье

- •10.4. Дискретное преобразование Фурье

- •Глава 10. Цифровая обработка сигналов

- •10.4. Дискретное преобразование Фурье

- •Глава 10. Цифровая обработка сигналов

- •10.4. Дискретное преобразование Фурье

- •Глава 10. Цифровая обработка сигналов

- •Часть II. Практикум на Electronics

- •1. Уравнения элементов и уравнения соединений

- •2. Метод комплексных амплитуд

- •3. Анализ сложных цепей

- •4. Параметры и функции четырехполюсника

- •5. Частотные характеристики фильтров

- •6. Процессы в длинных линиях

- •7. Спектры периодических сигналов (ряд Фурье)

- •8. Метод ряда Фурье

- •9. Метод интеграла Фурье

- •10. Метод преобразования Лапласа

- •II. Спектры модулированных сигналов

- •12. Характеристики диодов

- •13. Параметры и характеристики транзисторов

- •14. Усилитель на биполярном транзисторе

Глава 9. Импульсные и цифровые устройства Комбинационная схема, выполняющая арифметическое сложение

двух двоичных чисел, называется сумматором. Сумматор — важней-

шая часть арифметико-логического блока микропроцессора. Различа-

ют две разновидности сумматоров: полусумматор и полный сумма-

тор. Полный сумматор отличается тем, что на его дополнительный

вход поступает сигнал переноса от предыдущей схемы суммирования.

Такого дополнительного входа у полусумматора нет. Сумматоры ха-

рактеризуются разрядностью. Различают одно- и многоразрядные

сумматоры. Как правило, многоразрядные сумматоры строятся на ос-

нове одноразрядных сумматоров.

HS i

b—

p

а)

Рис. 6

Условные обозначения полусумматора и полного сумматора при-

ведены на рис. 6, а, б соответственно. На рисунке: а, Ь — входные

двоичные числа, р и р„ — сигналы переноса, р„ _ ] — входной сигнал

переноса, s — сумма двух чисел.

Таблица истинности для одноразрядного полусумматора показана

на рис. 7. На основании данных этой таблицы, используя совершен-

ВходыВыходы

аЬsр

0000

1100

1 1 00

11 0 1

Рис. 7

ную нормальную дизъюнктивную форму логических функций, легко

получить формулы для суммы: s = ab + ab, и для сигнала переноса:

р- аЪ.

Из анализа этих формул следует, что для построения полусумма-

тора необходимо использовать схемы И, инверторы НЕ и схему ИЛИ.

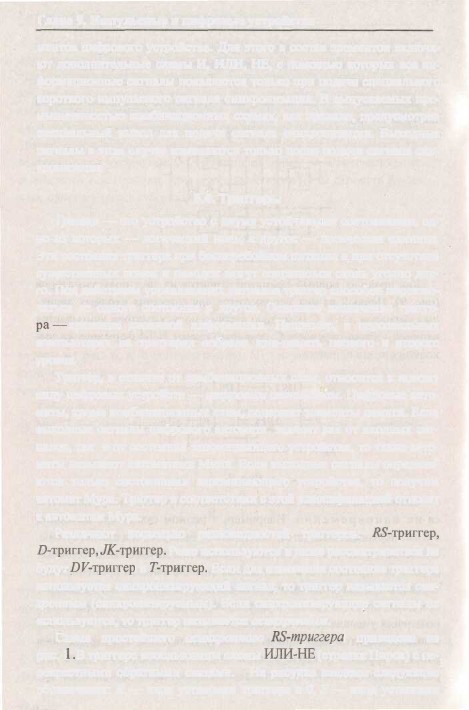

Функциональная схема полусумматора показана на рис. 8. С помощью

двух

инверторов, включенных на входе

полусумматора, на внутрен-

ней

четырехразрядной шине данных

предварительно формируется на-

бор

логических сигналов: a, a, b, b . С помощью

схем логическо-

го

умножения и сложения получаем требуемые

выходные сигналы

полусумматора.

а

а Ь ь

а

\

&

1

'

&

&

D

1

,

^—

р

Рис.8

Как

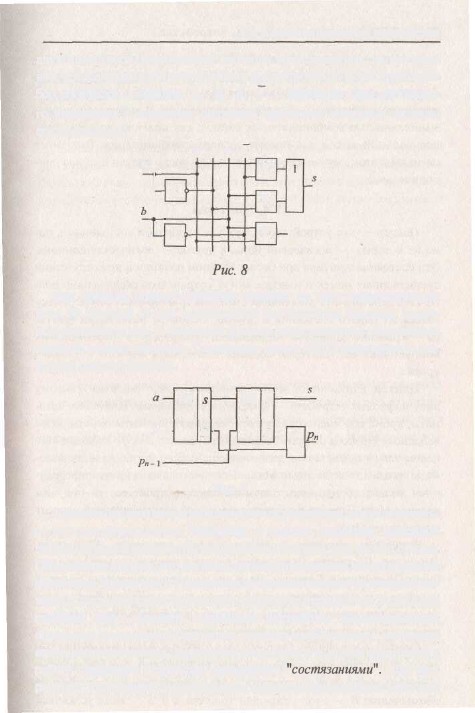

правило, полный сумматор строится из

двух полусумматоров9.3. Комбинационные устройства

(рис. 9). Первый из них используется для сложения входных двоич-

ных сигналов а и Ъ. С помощью второго полусумматора учитывается

входной сигнал переноса. С помощью схемы ИЛИ формируется вы-

ходной сигнал переноса.

HS s

HS s

Ъ—

Р

1Г

Рис. 9

Р— 1

Рп

Сигналы на выходах комбинационных устройств могут появлять-

ся не о д н о в р е м е н н о . Например, в полном сумматоре выходной

сигнал переноса появляется, как правило, быстрее, чем сигнал суммы.

Объясняется это тем, что сигналы проходят различное число ступеней

обработки. Кроме того, в импульсном сигнале имеется временной ин-

тервал, когда значение логического сигнала не определено. Указанные

причины могут вызывать в цифровом устройстве неодновременное

появления управляющих сигналов, ложные срабатывания, возникно-

вение дополнительных паразитных импульсов и т. п. Эти нарушения в

работе цифрового устройства называются "состязаниями". Для уст-

ранения "состязаний" осуществляют синхронизацию работы всех эле-