- •Види пам'яті.

- •Класифікація оп:

- •Напівпровідникові запам'ятовуючі пристрої.

- •Типи динамічної пам'яті.

- •Едо (Extended Data Output) dram.(Гіперсторінковим режимом обміну нрм (Hyper Page Mode).)

- •Тип ведо (Burst edo) dram.

- •Синхронні типи пам'яті

- •Перспективні типи пам'яті.

- •Пам'ять із внутрішнім кэшем.

- •(Нове покоління типів пам'яті.)

- •Порівняльна характеристика і перспективні типи динамічної пам'яті.

- •Коротка характеристика розглянутих типів пам'яті

- •Використання відеопам'яті. Стандартні архітектури

- •Відеопам'ять (ram).

- •Відеопам'ять (rom).

- •Необов'язкова пам'ять rom і ram.

- •Нові типи відеопам'яті

- •Що нас очікує в майбутньому?

- •Віртуальна пам'ять і організація захисту пам'яті Концепція віртуальної пам'яті

- •Сторінкова організація пам'яті

- •Сегментація пам'яті

- •Логічне представлення основної пам'яті пеом.

- •Стандартна пам'ять.

- •Додаткова пам'ять.

- •Верхня пам'ять.

Зміст.

Види пам'яті.

ОЗП

Ядро

Напівпровідникові запам'ятовуючі пристрої.

Типи динамічної пам'яті.

Тип FPM (Fast Page Mode) (Швидкий сторінковий обмін).

ЕДО (Extended Data Output) DRAM.(Гіперсторінковим режимом обміну) Тип EDO.

Тип ВЕДО (Burst EDO) DRAM.

Синхронні типи пам'яті

Перспективні типи пам'яті.

Порівняльна характеристика і перспективні типи динамічної пам'яті.

Використання відеопам'яті.

Стандартні архітектури

Відеопам'ять (RAM).

Відеопам'ять (ROM).

Необов'язкова пам'ять ROM і RAM.

Нові типи відеопам'яті

Що нас очікує в майбутньому?

Віртуальна пам'ять і організація захисту пам'яті

Концепція віртуальної пам'яті

Сторінкова організація пам'яті

Сегментація пам'яті

Логічне представлення основної пам'яті ПЕОМ.

Стандартна пам'ять.

Додаткова пам'ять.

Верхня пам'ять.

27. Література.

Види пам'яті.

Яке місце пам'ять займає в обчислювальній системі? При характеристиці ПК говоримо 1) тип процесора

2) його швидкодія

3) обсяг ОЗП

швидкодія пам'яті не в останню чергу визначає продуктивність ПК. Приклад тому – скачок «потужності» при переході на шину в 100мгц. Згадаємо, що «елементарні частки» інтегральних схем здебільшого розташовані в пам'яті: У ПК з ОЗП=64мб у Пентиуме 3 їх більш напівмільярди -переважна більшість в ОЗП і тільки 9,5 мільйона - у процесорі.

Імовірність збою зростає при збільшенні елементів системи, отже, надійність ПК залежить від надійності пам'яті. Відома увага до кількості пам'яті, а от до якості- обмаль.

По своїй функціональній ознаці пам'ять будь-який ПЕОМ поділяється на наступні ієрархічні рівні:

Сверхоперативна пам'ять (СОП). Використовується для збереження покажчиків адрес і проміжних результатів обчислень;

Кеш-пам'ять, що виконує роль буфера між мікропроцесором і іншими пристроями;

ОЗП і ПЗП;

Зовнішню оперативно-доступну пам'ять (ВОДП), призначену для збереження програм, що можуть бути безпосередньо завантажені в ОЗП для їхнього виконання, а також масивів даних, використовуваних виконуваними програмами і формованими цими програмами;

Зовнішню дублюючу пам'ять (ВДП), призначену для створення резервних копій (архівів) програм і даних, а також для зв'язку з «зовнішнім світом» (тобто з зовнішніми всілякими електронними пристроями) стосовно системного блоку ПЕОМ.

З фізичної точки зору ОП являє собою сукупність мікросхем пам'яті, розташованих усередині системного блоку ПЕОМ.

На логічному рівні ОП являє собою сукупність осередків визначеної розрядності (як правило, 1 байт), до вмісту яких можна звертатися по їхній адресі під час операції читання або записи.

ОП характеризується такими показниками:

Часом доступу (швидкодією);

Ємністю;

Вартістю;

Споживаною потужністю (енергоспоживанням).

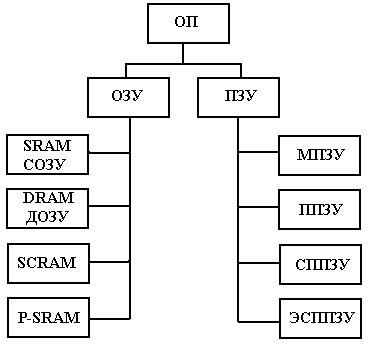

Класифікація оп:

ОЗП

У залежності від способу збереження інформації ОЗП поділяються на:

Статичні ОЗП (SRAM);

Динамічні ОЗП (DRAM);

Статичні векторні ОЗП (SCRAM);

Псевдостатические ОЗП (P-SRAM).

Основна пам'ять сучасних комп'ютерів реалізується на мікросхемах статичних і динамічних ЗУПВ (Запам'ятовуючий Пристрій з Довільною Вибіркою). Мікросхеми статичних ЗП мають менший час доступу і не вимагають циклів регенерації. Мікросхеми динамічних ЗП характеризуються більшою ємністю і меншою вартістю, але вимагають схем регенерації і мають значно більший час доступу.

У процесі розвитку ДЗП з ростом їхньої ємності основним питанням вартості таких мікросхем було питання про кількість адресних ліній і вартості відповідного корпуса. Було прийняте рішення про необхідність мультиплексированія адресних ліній, що дозволило скоротити наполовину кількість контактів корпуса, необхідних для передачі адреси. Тому звертання до ДЗП звичайно відбувається в два етапи: перший етап починається з видачі сигналу RAS - row-access strobe (строб адреси рядка), що фіксує в мікросхемі адреса рядка, що надійшла, другий етап включає переключення адреси для вказівки адреси стовпця і подачу сигналу CAS - column-access stobe (строб адреси стовпця), що фіксує цю адресу і дозволяє роботу вихідних буферів мікросхеми. Назви цих сигналів зв'язані з внутрішньою організацією мікросхеми, що як правило являє собою прямокутну матрицю, до елементів якої можна адресуватися за допомогою вказівки адреси рядка й адреси стовпця.

Додатковою вимогою організації ДЗП є необхідність періодичної регенерації її стану. При цьому всі біти в рядку можуть регенеруватися одночасно, наприклад, шляхом читання цього рядка. Тому до всіх рядків усіх мікросхем ДЗП основної пам'яті комп'ютера повинні вироблятися періодичні звертання в межах визначеного тимчасового інтервалу порядку 8 мілісекунд.

Це вимога крім всього інші означає, що система основної пам'яті комп'ютера виявляється іноді недоступної процесорові, тому що вона змушена розсилати сигнали регенерації кожній мікросхемі. Розроблювачі ДЗП намагаються підтримувати час, затрачуваний на регенерацію, на рівні менш 5% загального часу. Звичайно контролери пам'яті включають у свій склад апаратуру для періодичної регенерації ДЗППВ.

На відміну від динамічних, статичні ЗП не вимагають регенерації і час доступу до них збігається з тривалістю циклу. Для мікросхем, що використовують приблизно ту саму технологію, ємність ДЗП за грубими оцінками в 4 - 8 разів перевищує ємність СЗП, але останні мають у 8 - 16 разів меншу тривалість циклу і велику вартість. З цих причин в основній пам'яті практично будь-якого комп'ютера, проданого після 1975 року, використовувалися напівпровідникові мікросхеми ДЗП (для побудови кеш-пам'яті при цьому застосовувалися СЗП). Природно минулого і виключення, наприклад, в оперативній пам'яті суперкомп'ютерів компанії Cray Research використовувалися мікросхеми СЗП.

Для забезпечення збалансованості системи з ростом швидкості процесорів повинна лінійно рости і ємність основної пам'яті. В останні роки ємність мікросхем динамічної пам'яті учетверялась кожні три роки, збільшуючись приблизно на 60% у рік. На жаль швидкість цих схем за цей же період росла набагато меншими темпами (приблизно на 7% у рік). У той же час продуктивність процесорів починаючи з 1987 року практично збільшувалася на 50% у рік.

Отже можна говорити, що ОЗП бувають статистичні (сверхоперативі) і динамічні. Статистичні ( у 13 разів швидше, ніж динамічні (4,5 нс проти 60нс). Сьогодні їхнє використання дуже дороге. Тому застосовуються мікросхеми статистичної пам'яті КЭШ- пам'яттю першого, другого (42) третього (43) рівнів (якщо вона не інтегрована на один кристал із процесором). Обсяг (42 і 43) звичайно не перевищує 1мб (частіше 256-512 кб). Обсяг 41 (більш швидкого)=64кб (звичайно 41 на одному кристалі з процесором). Отже, динамічна пам'ять (у силу дешевини) використовується як основну пам'ять. 64 Мб для неї звичний обсяг.

Популярна сьогодні інтегрована система пам'яті має обсяг 64 мбіт тобто67108264 осередку. Якби до кожного осередку підводили окремий провідник для запису і зчитування, навіть при кроці в 0,25 мкм загальна ширина їхній буде 16,78 м!, а сумарна площа - величезне число.

Придуманий спосіб рішення цієї проблеми – потрібно розмістити осередку на перехрестя сітки з проводів. Тоді розміщення проводів стане простим і їхньою кількістю зменшиться до 2 х кількість осередків, тобто в нашому випадку буде 8000 у кожнім напрямку. Тепер кожен осередок підключений до двох проводів – один для керування зчитування (записом) осередку, іншої – для передачі значення в ній що зберігається.

Ядро

У мікросхемах пам'яті деякі групи осередків виявляються зв'язаними. Осередку, об'єднані керуючим провідником, прийнято називати рядком або row (немов вони розташовані в квадратній таблиці горизонтально). Осередку, об'єднані провідником, що передає значення, називають стовпцем або column (якби вони розташувалися по вертикалі) тоді при виборі рядка зчитуються відразу всі її осередки, тобто на __із провідників стовпців виникає напруга, обумовлене логічним значенням відповідного осередку обраного рядка. Описана сукупність осередків, що обрамляють їхні логічні елементи, зв'язані з вибором рядків і стовпців і називаються ядром інтегральної схеми.

Існує інтерфейсна логіка, що забезпечує взаємодію ядра з зовнішнім світом.

Використовується 2 поняття:

1)логічна організація інтегральної схеми;

2)структура ядра.

Під логічною організацією рОЗПміємо – розрядність мікросхеми (тобто число ліній уведення/висновку даних і глибину адресного простору (тобто кількість біт, що можуть бути збережені для ___ розряду)). Їх звичайно представляють у виді добутку; наприклад:64мбітні інтегральні схеми випускають з організацією 16м х 4; 8м х 8; 4м х 16.Даний добуток показує обсяг пам'яті мікросхеми (у бітах) часто називаний щільністю. Таким чином, з погляду логічної організації “рядка” і “стовпця” мають адреси, представлені на зовнішніх висновках, причому стовпець містить стільки розрядів, скільки є ліній уведення/висновку даних. Помітимо, що стовпець, що має зовнішню адресу і стовпець у ядрі – одне і теж, тільки при однорозрядній організації пам'яті (у нашому прикладі було при 64м х 1).

Обсяг пам'яті в ПК завжди вказується в байтах. На модулі пам'яті (платі з інтегральними схемами пам'яті) розміщають стільки інтегральних схем, скільки потрібно для одержання потрібної розрядності. У нашому прикладі – для створення 64 розрядного модуля пам'яті ємністю 32 мб (тобто на ньому потрібно розмістити наприклад 4 інтегральні схеми з організацією 4м х 16).

Існуючі фізичні обмеження описаної організації ядра і засобів доступу до осередків визначають максимально можливу частоту масиву комірок пам'яті. Тому прискорити роботу ядра не удасться. Тому зусилля зосередилися на обслуговуючій електроніці.

Розглянемо звертання до пам'яті: воно складається з 2 частин :1) указує характер операції (читання/запис); 2)передає адресу, по якому виконається обмін даними.

Зовнішні інтерфейсні адресні лінії в типів динамічної пам'яті загальні для рядків і стовпців. Адреси рядків і стовпців не використовуються одночасно отже це дозволяє вдвічі скоротити кількість висновків у інт.схемі отже знизити її ціну. Передача повної адреси в 2 етапи: сигналу, адреса рядка, потім стовпця. У першому випадку сигнал RAS (Row Access Strobe), у другому CAS (Coluvn Access Strobe). Подають них із затримкою. Контролер (керуючий цим процесором) – пристрій синхронне, тобто спрацьовує тільки по тактових імпульсах, отже, на кожну операцію треба мінімальний такт. Звичайної інт.схемі для проведення кожної операції з одним рядком треба 5 тактів.

1)указівка типу операції й установки адреси рядка;

2)формування сигналу RAS ;

3)установка адреси стовпця

4)формування сигналу CAS;

5)повернення сигналів RAS і CAS у неактивний стан.

Щоб забезпечити схоронність даних треба регулярно (часто) виконувати регенерацію. Адже конденсатор, у якому зберігається значення осередку згодом розряджається отже його заряд треба періодично відновлювати (тому пам'ять і названа динамічної).