- •Введение

- •Список сокращений

- •1. Архитектура современных микропроцессоров

- •1.1. Термины и определения

- •1.2. Микропроцессорные системы управления

- •1.3. Архитектурные особенности микропроцессоров

- •1.3.1. Гарвардская и принстонская архитектура

- •1.3.2. Архитектура системы команд (cisc и risc)

- •1.4. Корпус микропроцессоров

- •1.5. Технология изготовления кристаллов

- •1.6. Общие положения об обозначении импортных цифровых микросхем

- •1.6.1. Система обозначений микросхем производства Atmel

- •2. Структура микропроцессорной системы

- •2.1. Модуль питания

- •2.2. Модуль сброса и синхронизации

- •2.2.1. Сторожевой таймер

- •2.2.2. Тактирование системы

- •2.3. Модуль памяти

- •2.3.1. Супервизор напряжения

- •2.3.2. Память микропроцессорного устройства

- •2.4. Контроллер прерываний

- •2.5. Терминал

- •2.6. Центральный процессор

- •2.7. Суперскалярный конвейер

- •3. Программирование микропроцессорных устройств

- •3.1. Основные этапы проектирования и отладки программного обеспечения

- •3.2. Языки высокого уровня

- •3.3. Язык Ассемблера

- •3.3.1. Способы адресации на языке ассемблера

- •3.4. Алгоритм выполнения команды

- •3.5. Типы данных микропроцессора

- •4. Микропроцессоры с архитектурой х86

- •4.1. Микропроцессор Pentium

- •4.2. Микропроцессор Pentium 4

- •4.3. Микропроцессоры компании amd

- •4.4. Микропроцессор к7

- •5. Микропроцессоры с архитектурой x64

- •5.1.Микропроцессор Itanium ia-64

- •Отличия архитектур процессоров х86 и ia-64

- •5.2. Микропроцессоры семейства Hammer

- •Микропроцессоры c архитектурой power pc и arm

- •6.1. Микропроцессоры с архитектурой power

- •Процессоры arm

- •6.2. Микропроцессоры с архитектурой arm

- •4. Микроконтроллеры семейства mcs-51

- •4.1. Структура микроконтроллеров семейства mcs-51

- •4.2 Способы адресации и система команд микроконтроллеров семейства mcs-51

- •4.3. Функции выводов

- •5. Микроконтроллеры семейства Motorola

- •5.1. Общая структура микроконтроллеров семейства 68нс05/705/08

- •4.2.2. Регистровая модель микроконтроллеров семейства 68нс05/705/08

- •4.2.3. Способы адресации и система команд микроконтроллеров семейства 68нс05/705/08

- •6. Микроконтроллеры avr компании Atmel

- •5.1. Архитектура микроконтроллеров avr

- •5.2. Процессор микроконтроллера avr

- •5.3. Запоминающее устройство FlashRom

- •5.4. Периферийные устройства

- •Микроконтроллеры семейства piCmicro

- •12.1. Младшие подсемейства picMicro

- •Основные характеристики микроконтроллеров младшего подсемейства

- •12.2. Архитектура микроконтроллеров младшего подсемейства

- •Стандартный набор операций алу микроконтроллеров PlCmicro

- •12.3. Среднее подсемейство picMicro

- •12.5. Старшее подсемейство picMicro

- •12.6 Архитектура микроконтроллеров старшего подсемейства

- •Ввод-вывод данных микропроцессорной системы

- •6.1 Аналоговый ввод/вывод микропроцессорной системы

- •6.2. Таймеры микропроцессорной системы

- •6.3. Параллельный ввод-вывод данных

- •6.2.2. Асинхронный последовательный обмен

- •6.2.3 Синхронный последовательный обмен

- •6.3. Микроконтроллерная сеть

- •6.3.1 Протокол i2c

- •6.3.2. Протокол can

- •Характеристика протокола can

- •Выбор скорости передачи данных исходя из расстояния

- •6.3.3. Протокол rs-485 и rs-422

- •Стандартные параметры интерфейсов rs-422 и rs-485

- •Лекция 7 Микропроцессорные системы управления

- •7.1. Подключение светодиодов

- •7.2. Подключение 7-сегментных светодиодных индикаторов

- •7.3. Ввод с матричной клавиатуры

- •7.4. Управление жидкокристаллическим индикатором

- •7.5. Управление соленоидом и реле

- •7.6. Управление электродвигателем

- •6.5.1. Управление шаговым двигателем

- •7.6. Управление мощной нагрузкой

- •Лекция 8 Цифровая обработка сигналов

- •8.1. Типовые задачи решаемые цос

- •8.2. Способы реализации алгоритмов цос

- •8.3. Структура процессора цифровой обработки сигналов

- •8.4. Пцос с фиксированной и плавающей точкой

- •8.5. Гибридные процессоры

- •Библиографический список

- •Фирмы-производители 8-, 16- и 32-разрядных микроконтроллеров

- •Высокопроизводительные 8-разрядные risc микроконтроллеры семейства avr

- •1.6.2. Система обозначений микросхем производства

- •1.6.3. Система обозначений микросхем производства Motorola

- •1.6.4. Система обозначений микросхем производства

1.3.2. Архитектура системы команд (cisc и risc)

ПО процессоров имеет две основные архитектуры набора команд CISC и RISC, которые используются компьютерной промышленностью.

RISC (Reduced Instruct Set Computers) – это класс процессоров который имеет меньший и более простой набор инструкций. Сложная инструкция создаётся из значительно более простых. Для эффективной работы RISC-процессора на его кристалле располагается большое количество регистров, что сокращает число обращений к внешней памяти. RISC-процессор отличается простотой, которая в сочетании с высокой тактовой частотой и более эффективным выполнением инструкций позволяет создавать на основе RISC-процессора компьютеры с очень большим быстродействием.

CISC (Complex Instruction Set Computers) – это класс процессоров который предполагает широкий набор инструкций. Увеличение производительности таких процессоров связано с повышением тактовой частоты. Так как процессоры типа CISC работают со сложными инструкциями, требующими много тактов, их выполнение характеризуется относительно невысокой скоростью, хотя в них используется конвейерная обработка инструкций.

Основоположником CISC-архитектуры можно считать компанию IBM с ее базовой архитектурой ES/360, ядро которой, используется с1964 года, и дошло до наших дней.

Лидером в разработке МП c полным набором команд (CISC) считается компания Intel со своей серией x86 и Pentium. Эта архитектура является практическим стандартом для рынка микрокомпьютеров. Для CISC-процессоров характерно:

– сравнительно небольшое число регистров общего назначения;

– большое количество машинных команд, некоторые из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и выполняются за много тактов;

– большое количество методов адресации; большое количество форматов команд различной разрядности;

– преобладание двухадресного формата команд; наличие команд обработки типа регистр-память.

В настоящее время существует множество RISC процессоров, так как сложилось мнение, что RISC быстрее, чем CISC процессоры. Такое мнение не совсем верно. Имеется много процессоров называемых RISC, но на самом деле относящихся к CISC. Более того, в некоторых приложениях CISC-процессоры выполняют программный код быстрее, чем это делают RISC-процессоры, или решают такие задачи, которые RISC-процессоры не могут выполнить.

CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации. В RISC-процессорах набор выполняемых команд сокращен до минимума.

Успех при использовании RISC-процессоров обеспечивается благодаря тому, что их более простые команды требуют для выполнения значительно меньшее число машинных циклов.

1.4. Корпус микропроцессоров

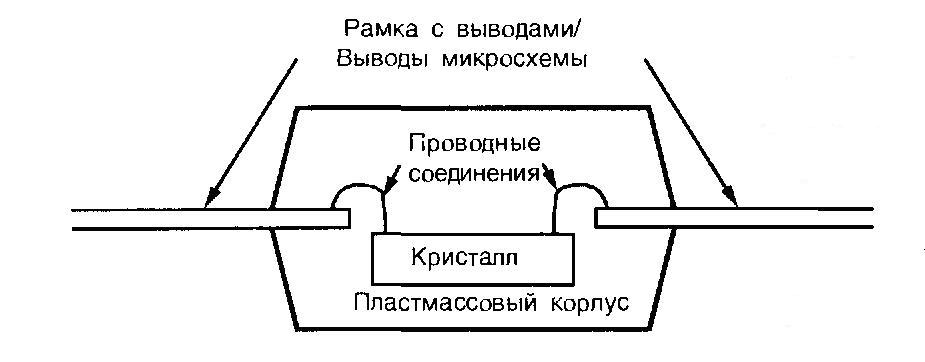

Наиболее распространенными являются пластмассовые корпуса. Кристалл, помещенный в такой корпус, соединяется с внешними выводами при помощи тонких алюминиевых проволочек, которые привариваются к кристаллу с использованием ультразвука. Для заливки пластиковых корпусов используется эпоксидный герметик. Когда герметик затвердеет, кристалл становится защищенным от света, влаги и механического воздействия как показано на рис 5.

Для защиты кристаллов от внешней среды используются два основных материала пластмасса и керамика.

Рис. 5. Пластмассовый корпус для интегральных схем

Ранее более распространенными являлись компоненты, изготовленные в DIP (Dual In-line Package) – корпусах, которые обычно имеют от 8 до 40 выводов. Данный корпус имеет прямоугольную форму с двумя рядами выводов по длинным сторонам. Преимуществом этой технологии монтажа является ее простота, которая не требует сложного оборудования и специальной подготовки. Недостатком является то, что отверстие занимает на плате значительную площадь, и расстояние между соседними выводами интегральной схемы (ИС) должно быть существенно больше, что увеличивает размеры платы. Корпуса, выполненные из пластика, обозначаются PDIP или керамики CDIP.

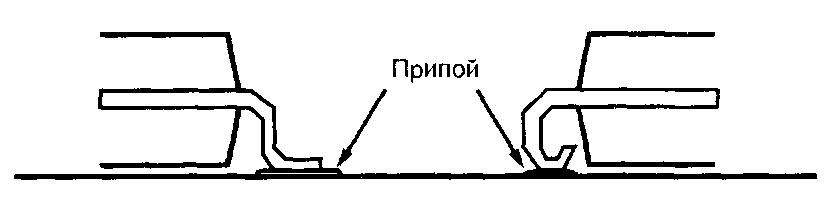

Для уменьшения размеров печатных плат используется технология поверхностного монтажа (SMT – surface mount technology). По данной технологии изготавливают QFP (Quad Flat Package) – корпуса ИС, имеющих планарные выводы, расположенные по всем четырём сторонам. На рис 6. представлен монтаж корпусов на поверхность печатной платы.

Рис. 6. Способ монтажа микросхем на печатной плате

Корпус с данным выводом позволяет производить ручную пайку и обеспечивает более простой контроль паяных соединений. В настоящее время корпуса с данными выводами значительно более популярны, так как их использование позволяет применять более простое производственное оборудование и обеспечить переход к сверхплотному монтажу, когда расстояние между центрами выводов уменьшается до 0,41 мм

Типичное значение шага расположения выводов DIP – корпусов составляет 2,54 мм, тогда как шаг для QFP – корпуса имеет шаг выводов от 1,27 мм до 0,41 мм.

Для производителя установка и снятие QFP – корпусов реализуется проще, чем DIP – корпусов. На посадочные места наносится специальная смесь припоя и флюса, которая называется паяльной пастой, затем плата помещается в печь, где паста расплавляется и припаивает ИС к плате. Чтобы снять компонент с платы, его выводы обдуваются горячим воздухом или азотом, который расплавляет припой, после чего компонент может быть удален. В то время как производителю, имеющему специальное оборудование, легче работать с QFP – корпусами, для инженера-разработчика или радиолюбителя это намного сложнее, поэтому используются кроватки под ИС.

Выпускаются ИС в других корпусах, которые перечислены далее. Тип корпуса SOIC (Small-Outline Integrated Circuit – маленькая интегральная схема), предназначенный для поверхностного монтажа. Имеет форму прямоугольника с двумя рядами выводов по длинным сторонам. ИС в корпусе SOIC занимают на 30-50% меньше площади печатной платы, чем их аналоги в корпусе DIP, а также обычно имеют меньшую на 70% толщину.

Тип корпуса PLCC (Plastic Leaded Chip Carrier) и СLCC (Ceramic Leaded Chip Carrier) представляют собой квадратный корпус с расположенными по краям контактами, предназначенный для установки в специальную панель.

Для монтажа кристаллов с очень большим количеством выводов (более 300) используются технологии шариковых выводов – BGA (Ball Grid Array – корпус с матрицей шариковых выводов).

LGA (Land Grid Array) – представляет собой корпус PGA, в котором штырьковые контакты заменены на контактные площадки. Может устанавливаться в специальное гнездо, имеющее пружинные контакты, либо устанавливаться на печатную плату.