- •Введение

- •Список сокращений

- •1. Архитектура современных микропроцессоров

- •1.1. Термины и определения

- •1.2. Микропроцессорные системы управления

- •1.3. Архитектурные особенности микропроцессоров

- •1.3.1. Гарвардская и принстонская архитектура

- •1.3.2. Архитектура системы команд (cisc и risc)

- •1.4. Корпус микропроцессоров

- •1.5. Технология изготовления кристаллов

- •1.6. Общие положения об обозначении импортных цифровых микросхем

- •1.6.1. Система обозначений микросхем производства Atmel

- •2. Структура микропроцессорной системы

- •2.1. Модуль питания

- •2.2. Модуль сброса и синхронизации

- •2.2.1. Сторожевой таймер

- •2.2.2. Тактирование системы

- •2.3. Модуль памяти

- •2.3.1. Супервизор напряжения

- •2.3.2. Память микропроцессорного устройства

- •2.4. Контроллер прерываний

- •2.5. Терминал

- •2.6. Центральный процессор

- •2.7. Суперскалярный конвейер

- •3. Программирование микропроцессорных устройств

- •3.1. Основные этапы проектирования и отладки программного обеспечения

- •3.2. Языки высокого уровня

- •3.3. Язык Ассемблера

- •3.3.1. Способы адресации на языке ассемблера

- •3.4. Алгоритм выполнения команды

- •3.5. Типы данных микропроцессора

- •4. Микропроцессоры с архитектурой х86

- •4.1. Микропроцессор Pentium

- •4.2. Микропроцессор Pentium 4

- •4.3. Микропроцессоры компании amd

- •4.4. Микропроцессор к7

- •5. Микропроцессоры с архитектурой x64

- •5.1.Микропроцессор Itanium ia-64

- •Отличия архитектур процессоров х86 и ia-64

- •5.2. Микропроцессоры семейства Hammer

- •Микропроцессоры c архитектурой power pc и arm

- •6.1. Микропроцессоры с архитектурой power

- •Процессоры arm

- •6.2. Микропроцессоры с архитектурой arm

- •4. Микроконтроллеры семейства mcs-51

- •4.1. Структура микроконтроллеров семейства mcs-51

- •4.2 Способы адресации и система команд микроконтроллеров семейства mcs-51

- •4.3. Функции выводов

- •5. Микроконтроллеры семейства Motorola

- •5.1. Общая структура микроконтроллеров семейства 68нс05/705/08

- •4.2.2. Регистровая модель микроконтроллеров семейства 68нс05/705/08

- •4.2.3. Способы адресации и система команд микроконтроллеров семейства 68нс05/705/08

- •6. Микроконтроллеры avr компании Atmel

- •5.1. Архитектура микроконтроллеров avr

- •5.2. Процессор микроконтроллера avr

- •5.3. Запоминающее устройство FlashRom

- •5.4. Периферийные устройства

- •Микроконтроллеры семейства piCmicro

- •12.1. Младшие подсемейства picMicro

- •Основные характеристики микроконтроллеров младшего подсемейства

- •12.2. Архитектура микроконтроллеров младшего подсемейства

- •Стандартный набор операций алу микроконтроллеров PlCmicro

- •12.3. Среднее подсемейство picMicro

- •12.5. Старшее подсемейство picMicro

- •12.6 Архитектура микроконтроллеров старшего подсемейства

- •Ввод-вывод данных микропроцессорной системы

- •6.1 Аналоговый ввод/вывод микропроцессорной системы

- •6.2. Таймеры микропроцессорной системы

- •6.3. Параллельный ввод-вывод данных

- •6.2.2. Асинхронный последовательный обмен

- •6.2.3 Синхронный последовательный обмен

- •6.3. Микроконтроллерная сеть

- •6.3.1 Протокол i2c

- •6.3.2. Протокол can

- •Характеристика протокола can

- •Выбор скорости передачи данных исходя из расстояния

- •6.3.3. Протокол rs-485 и rs-422

- •Стандартные параметры интерфейсов rs-422 и rs-485

- •Лекция 7 Микропроцессорные системы управления

- •7.1. Подключение светодиодов

- •7.2. Подключение 7-сегментных светодиодных индикаторов

- •7.3. Ввод с матричной клавиатуры

- •7.4. Управление жидкокристаллическим индикатором

- •7.5. Управление соленоидом и реле

- •7.6. Управление электродвигателем

- •6.5.1. Управление шаговым двигателем

- •7.6. Управление мощной нагрузкой

- •Лекция 8 Цифровая обработка сигналов

- •8.1. Типовые задачи решаемые цос

- •8.2. Способы реализации алгоритмов цос

- •8.3. Структура процессора цифровой обработки сигналов

- •8.4. Пцос с фиксированной и плавающей точкой

- •8.5. Гибридные процессоры

- •Библиографический список

- •Фирмы-производители 8-, 16- и 32-разрядных микроконтроллеров

- •Высокопроизводительные 8-разрядные risc микроконтроллеры семейства avr

- •1.6.2. Система обозначений микросхем производства

- •1.6.3. Система обозначений микросхем производства Motorola

- •1.6.4. Система обозначений микросхем производства

Отличия архитектур процессоров х86 и ia-64

Процессор х86 |

Процессор IA-64 |

Использование сложных инструкций переменной длины, обрабатываемых по одной. |

Использование простых инструкций, сгруппированных по три, одинаковой длины. |

Переупорядочивание и оптимизация инструкций во время выполнения. |

Переупорядочивание и оптимизация инструкций во время компиляции. |

Попытки предсказания переходов. |

Исполнение нескольких последовательностей команд одновременно без предсказания переходов. |

Загрузка данных из памяти по мере необходимости |

Загрузка данных до того, как они потребуются |

Основными особенностями EPIC являются: большое количество регистров; масштабируемость по количеству функциональных устройств; явное задание параллелизма в машинном коде; предикатное исполнение инструкций; упреждающая загрузка данных по предположению.

Архитектура IA-64 объединяет в себе лучшие качества суперскалярных микропроцессоров и микропроцессоров с длинным командным словом (VLIW – Very Long Instruction Words). В микропроцессоре Itanium, как и в других микропроцессорах VLIW-архитектуры, последовательность команд и план загрузки исполнительных устройств формируются на этапе компиляции. В ходе выполнения программы последовательность команд не изменяется. В микропроцессоре используется динамическое предсказание переходов, спекулятивное (по предположению) исполнение команд, аппаратная поддержка конвейерного выполнения циклов, отложенные операции обращения к памяти, предварительная загрузка данных в кэш.

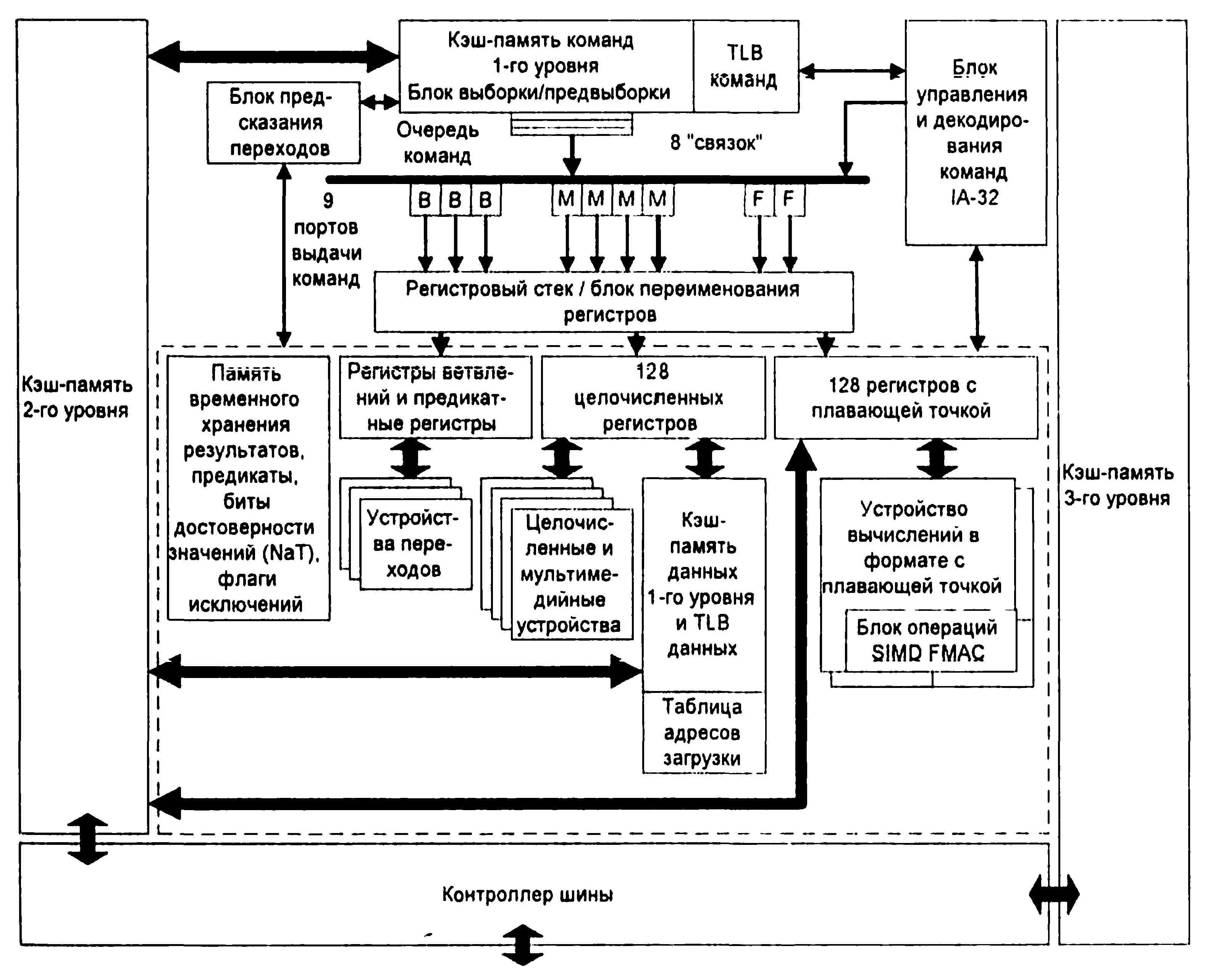

Структура микропроцессора Itanium показана на рис. 27.

Рис. 27. Структура микропроцессора Itanium

Данная структура содержит: четыре целочисленных устройства; четыре устройства обработки мультимедийных данных; по два устройства вычислений в формате с плавающей точкой одинарной и расширенной точности; два устройства загрузки/сохранения; три устройства выполнения переходов.

Все функциональные устройства микропроцессора конвейеризированы. Команда выполняется за 10 тактов, причем одновременно в микропроцессоре может выполняться до шести команд.

Высокоскоростной интерфейс процессор-память с пропускной способностью 2,1 Гбайт/с обеспечивает интенсивную подкачку данных и команд в микропроцессор.

Процессор может напрямую адресовать до 18 Гбайт оперативной памяти. Itanium использует трехуровневую кэш-память:

- первый уровень – внутренняя раздельная кэш-память команд и данных, по 16 Кбайт каждая;

- второй уровень – внутренняя общая кэш-память команд и данных, 96 Кбайт;

- третий уровень – внешняя (в картридже) общая кэш-память команд и данных до 4 Мбайт.

Команды микропроцессора группируются компилятором в «связку» длиной 128 бит. Связка содержит 3 команды и шаблон, указывающий, какие команды в текущей и следующей связке могут выполняться одновременно. Команды в связках могут размещаться в порядке, отличном от исходного, заданного в тексте программы, и могут быть как зависимые (по управлению и данным), так и независимые.

IA-64 поддерживает следующие типы данных: целые: 1, 2, 4 и 8 байт; с плавающей точкой: одинарный, двойной и расширенный двойной форматы; 0 указатели: 8 байт.

Другой особенностью IA-64 является предварительная загрузка данных в кэш-память. Сущность ее заключается в разнесении по времени команд загрузки данных из памяти и команд, их использующих.

Для обеспечения совместимости с ранее разработанными 32-разрядными приложениями в микропроцессоре Itanium поддерживаются два режима декодирования команд: VLIW и CISC.

В Itanium предусмотрена аппаратная поддержка выполнения циклов. Цикл разделяется на три фазы выполнения: пролог, ядро и эпилог.