- •Інструкція до лабораторної роботи №5 Дослідження тригерів на бле і-Не

- •Напрям підготовки 6.050102 “Комп’ютерна інженерія”

- •Викладач Технологічного коледжу Національного університету «Львівська політехніка» т.Д. Мандзевич

- •1. Мета роботи

- •2. ТеоретичНа частина

- •3. Експериментальна частина

- •3.1. Опис лабораторного макету.

- •5. Контрольні запитання

- •6. Література

МІНІСТЕРСТВО ОСВІТИ І НАУКИ, молоді та спорту УКРАЇНИ

Технологічний коледж Національного університету

«Львівська політехніка»

Відділення комп’ютерних технологій

Інструкція до лабораторної роботи №5 Дослідження тригерів на бле і-Не

з дисципліни “Комп’ютерна електроніка”

для студентів коледжу

Спеціальність 5.05010201 “Обслуговування комп’ютерних систем і мереж”

Напрям підготовки 6.050102 “Комп’ютерна інженерія”

ЛЬВІВ 2012

Інструкція до лабораторної роботи №5 “Дослідження тригерів на БЛЕ І-НЕ” з дисципліни "Комп’ютерна електроніка" для студентів коледжу спеціальності 5.05010201 “Обслуговування комп’ютерних систем і мереж” напряму підготовки 6.050102 “Комп’ютерна інженерія”- Львів: Видавництво Технологічного коледжу Національного університету «Львівська політехніка», 2012 - с. 16.

Укладач:

Викладач Технологічного коледжу Національного університету «Львівська політехніка» т.Д. Мандзевич

Інструкція до лабораторної роботи обговорена та схвалена на засіданні циклової комісії спеціальних комп’ютерних дисциплін коледжу

Протокол № від “____” __________2012 р.

Голова циклової комісії _______________ Л.М. Павліш

Рецензенти:

Войтович П.В. – викладач вищої категорії Технологічного коледжу Національного університету «Львівська політехніка»

Деревянченко Ю.Г. – викладач вищої категорії Технологічного коледжу Національного університету «Львівська політехніка»

Відповідальний за випуск:

Павліш Л.М. – Голова циклової комісії спеціальних комп’ютерних дисциплін Технологічного коледжу Національного університету «Львівська політехніка»

© Мандзевич Т.Д., 2012

1. Мета роботи

Метою роботи є вивчення принципів побудови та функціонування різних схем одноступеневих тригерів на базових логічних елементах І-НЕ.

2. ТеоретичНа частина

Тригером називається пристрій, що має два стійких стани. В одному з них на виході тригера присутній високий потенціал, в іншому – низький. Аналогічно мультивібратору перехід тригера з одного стану в інший відбувається лавиноподібно, але тільки з приходом перемикаючого (запускаючого) сигналу.

По принципу дії тригер подібний до стисненої пружини, яка спускається зовнішньою силою. Звідси ще одна назва тригера – спусковий пристрій.

В інтервалі між запускаючи ми сигналами стан тригера не міняється, тобто тригер «запам’ятовує» поступлення сигналу, відображаючи це величиною потенціалу на виході. Це дає можливість використовувати тригер як елемент пам’яті. Якщо сукупність тригерів встановити в однакове (початкове) положення, а потім на кожний тригер подати сигнал, відповідний елементу цифрового коду, то на виходах тригерів встановляться і можуть необмежено довго існувати потенціали, які представляють цей код в паралельній формі.

При перемиканні тригера потенціали на його виходах змінюються лавиноподібно, тобто на виході формується прямокутний імпульс з крутими фронтами. Це дозволяє використовувати тригер для формування прямокутних імпульсів з напруги іншої форми (наприклад, з синусоїдальної).

При надходженні кожної пари перемикаючих імпульсів потенціал на виході тригера міняється від високого до низького і навпаки, тобто на виході формується один імпульс. Отже, тригер можна використовувати як подільник частоти перемикаючих імпульсів на два.

Промисловість випускає різноманітні типи тригерів в інтегральному виконанні. Крім того, вони можуть бути виконані на цифрових інтегральних мікросхемах, операційних підсилювачах і дискретних компонентах (серед яких активними елементами є головним чином транзистори).

Інтегральний тригер може бути виконаний монолітним (тригер інтегрального виконання) або реалізований на логічних мікросхемах. Обидва види інтегральних тригерів зазвичай мають однакову функціональну структуру. Інтегральні тригери є асинхронні (нетактовані) і синхронні (тактовані). Аналогічно тригеру на дискретних компонентах, інтегральний асинхронний тригер має лише інформаційні входи, сигнали на яких від моменту їх появи визначають стан тригера. Синхронний тригер крім інформаційних входів має синхронізуючий (тактуючий, тактовий) вхід; сигнали на інформаційних входах діють на такий тригер тільки при наявності сигналу на синхронізуючому вході.

Будь-який тригер має два виходи. Потенціали

на них взаємно інвертовані: високий

потенціал на одному виході відповідає

низькому потенціалу на іншому. Один з

виходів називають основним (і

зазвичай позначають буквами Q

або P), другий –

інверсним (позначають буквами

![]() або

або

![]() ).

).

Стан тригера визначається станом його основного виходу. Якщо на ньому встановився потенціал, який кодується логічною одиницею, то говорять, що тригер знаходиться одиничному стані і позначають це як Q=1 (або P=1).

Вхід, по якому запускаючий імпульс перемикає тригер в стан Q=1, називають входом установки тригера в одиницю і позначають буквою S. Другий називають входом установки тригера в нуль і позначають буквою R. Входи S і R являються інформаційними: через них в тригер поступає інформація, яка виражається наявністю чи відсутністю перемикаючого сигналу. Такі тригери називають тригерами з установочними входами або RS-тригерами. Якщо перемикання тригера здійснюється установившимся рівнем запускаючого сигналу (тобто вимагає значної тривалості сигналу), то входи тригера є статичними.

Асинхронний RS-тригер. На виході елемента І-НЕ (АБО-НЕ) є інвертор (підсилювач). Тому на двох таких елементах можна виконати тригер, якщо вхід одного елемента з’єднати з виходом іншого.

Такий асинхронний RS-тригер являється найпростішим інтегральним тригером, який застосовується самостійно, а також входить до складу більш складних інтегральних тригерів як запам’ятовуюча комірка.

RS-тригер на елементах АБО-НЕ. Передусім розглянемо дію на такий тригер (рис. 1, а) комбінацій сигналів S=1, R=1 і S=0, R=0.

а) б)

Рис. 1. Схема RS-тригера на БЛЕ АБО-НЕ (а),

його умовне графічне зображення і позначення (б)

Поєднання S=1, R=1 являється забороненим, так як при ньому на обох виходах тригера встановлюються логічні 0 і після зняття вхідних сигналів стан його непередбачуваний.

Для елемента АБО-НЕ логічний 0 являється пасивним сигналом: з його поступленням на вхід стан виходу логічного елемента не зміниться. Тому поява комбінації S=0, R=0 не змінить стан тригера.

Логічна 1 для елемента АБО-НЕ є активним сигналом: наявність її на вході однозначно визначає на виході логічний 0 не залежно від сигналу на іншому вході. Як наслідок, перемикаючим сигналом для такого тригера являється логічна 1, а також те, що вхід S (установка тригера в стан Q=1) повинен бути зв’язаний з елементом, вихід якого прийнятий за (рис. 1, а).

З всього сказаного зрозуміло, що для перемикання тригера в стан Q=1 на його входи слід подати комбінацію S=1, R=0, а для перемикання в стан Q=0 – комбінацію S=0, R=1.

Нехай тригер (рис. 1, а) знаходиться в стані 0 (Q=0, =1), а на входах діють сигнали S=0, R=0. Для його перемикання в стан Q=1 подамо на входи комбінацію S=1, R=0. Тоді на виході елемента DD 1.2 встановиться логічний 0, на входах елемента DD 1.1 будуть одночасно діяти логічні 0 і на виході Q встановиться логічна 1 – тригер перемикається в новий стан (Q=1, =0). Для його перемикання з цього стану на входи повинна поступити комбінація S=0, R=1. Після цього на виході Q буде логічний 0, на входах елемента DD 1.2 одночасно з’являться логічні 0 і його вихід прийме потенціал =1 – тригер перемикається в стан Q=0, =1.

З викладеного випливає, що час перемикання тригера (tпер) дорівнює подвоєному часу перемикання логічного елемента (подвоєному часу затримки 2tз). Часто, передбачаючи запас, приймають tпер=3tз. для надійного перемикання тригера тривалість перемикаючого сигналу не повинна бути менша tпер.

Умовне позначення тригера зі статичними входами приведено на рис. 1, б.

На входи елементів тригера поступають чотири сигнали: S, R, Q t, t, де Q t, t характеризують початковий стан тригера (до зміни сигналів на входах S і R). Три з них (S, R, Q t) являються незалежними змінними. Ними визначається новий стан тригера (Q t+1), в який він перемикається слідом за зміною сигналів на входах S і R. Вказана залежність відображається таблицею перемикань (табл. 1), де прочерком у стовбці Q t+1 відзначені заборонені комбінації сигналів на S і R входах (набори 3, 7).

Таблиця 1

Номер набору n |

S |

R |

Q t |

Q t+1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

2 |

0 |

1 |

0 |

0 |

3 |

1 |

1 |

0 |

- |

4 |

0 |

0 |

1 |

1 |

5 |

1 |

0 |

1 |

1 |

6 |

0 |

1 |

1 |

0 |

7 |

1 |

1 |

1 |

- |

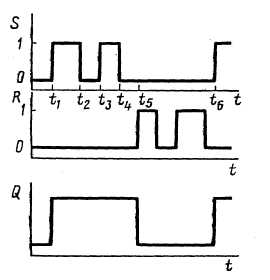

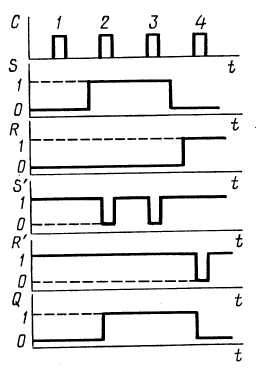

На рис 2 приведена ідеалізована часова діаграма RS-тригера, на якій час перемикання прийнято рівним нулеві. Припускається, що до моменту t1 S=0, R=0, а тригер знаходиться в стані Q=0. В момент t1 комбінація S=1, R=0 перемикає тригер в стан Q=1. При t= t2 на входах встановлюється поєднання S=0, R=0, при якому стан тригера зберігається попереднім. Комбінація S=1, R=0, що появляється в момент t3 і комбінація S=0, R=0 в момент t4 ніяких змін не вносять – надалі Q=1.

Тільки

в момент t5 поєднання S=0, R=1

викликає перемикання тригера в стан

Q=0. Слідом за тим зміна логічної

змінної на вході R

стан тригера не міняє. Нове перемикання

відбувається в момент t6

при поступленні комбінації S=1,

R=0. Зауважимо, що заборонене поєднання

сигналів S=1, R=1

на діаграмі відсутнє.

Тільки

в момент t5 поєднання S=0, R=1

викликає перемикання тригера в стан

Q=0. Слідом за тим зміна логічної

змінної на вході R

стан тригера не міняє. Нове перемикання

відбувається в момент t6

при поступленні комбінації S=1,

R=0. Зауважимо, що заборонене поєднання

сигналів S=1, R=1

на діаграмі відсутнє.

Рис. 2. Осцилограма RS-тригера

RS-тригер на елементах І-НЕ. Для елемента І-НЕ активним сигналом являється логічний 0: наявність його хоч би на одному вході обумовлює на виході логічну 1 не залежно від сигналів на інших входах. Логічна 1 для такого елемента являється пасивним сигналом: з її поступленням на вхід стан виходу елемента не міняється.

а) б)

Рис. 3. Схема RS-тригера на БЛЕ І-НЕ (а), його умовне графічне

зображення і позначення (б)

Отже, тригер на елементах І-НЕ (рис. 3, а) перемикається логічним 0. На умовному зображенні такого тригера (рис. 3, б) це відображають інверсними входами (кружками). Очевидно, що для даного тригера комбінація вхідних сигналів S=0, R=0 є забороненою (набори 0, 4 табл. 2), а комбінація S=1, R=1 не змінює його попереднього стану (набори 3, 7 табл. 2).

Так як тригери на елементах АБО-НЕ та І-НЕ перемикаються протилежними логічними сигналами, то таблицю перемикань для тригера, що розглядається, можна отримати з табл. 1, заміняючи 1 на 0 і навпаки в стовбцях S і R (табл. 2).

Таблиця 2

Номер набору n |

S |

R |

Q t |

Q t+1 |

0 |

0 |

0 |

0 |

- |

1 |

1 |

0 |

0 |

0 |

2 |

0 |

1 |

0 |

1 |

3 |

1 |

1 |

0 |

0 |

4 |

0 |

0 |

1 |

- |

5 |

1 |

0 |

1 |

0 |

6 |

0 |

1 |

1 |

1 |

7 |

1 |

1 |

1 |

1 |

Більш того, табл. 1 буде відповідати

тригеру на елементах І-НЕ, якщо рахувати,

що у вказаних стовбцях записані інверсії

вхідних сигналів

![]() і

і

![]() .

Щоби підкреслити перемикання тригера

нулем, такі позначення іноді ставлять

біля його вхідних виводів.

.

Щоби підкреслити перемикання тригера

нулем, такі позначення іноді ставлять

біля його вхідних виводів.

Синхронний RS-тригер. На входи логічного елемента або пристрою сигнали не завжди поступають одночасно, так як перед тим можуть проходити через різне число вузлів, що не завжди мають однаковий час затримки. Це явище називають змаганнями або гонками. В результаті нього на протязі деякого часу на входах створюється непередбачувана ситуація: нові значення одних сигналів поєднуються з попередніми значеннями інших, що може привести до хибного спрацювання елемента (пристрою).

Наслідки гонок можна ліквідувати часовим стробуванням, коли на елемент крім інформаційних сигналів подаються тактові (синхронізуючі) імпульси, до моменту приходу яких інформаційні сигнали однозначно встигають встановитися на входах.

Одноступеневий синхронний RS-тригер. На рис. 4, а зображена схема тактованого RS-тригера. Вона містить асинхронний RS-тригер Т1 з прямими входами (зібраний на елементах АБО-НЕ) і два кон’юнктора. Останні передають перемикаючу логічну 1 з інформаційного S- або R- входу на відповідні входи Т1 тільки при наявності на синхронізуючому вході С логічної 1. При С=0 інформація з S- і R- входів на тригер Т1 не передається. Умовне позначення тактованого RS-тригера приведено на рис. 4, б.

а) б)

Рис. 4. Схема одноступеневого RSС-тригера (а), його умовне графічне

зображення і позначення (б)

На рис. 5 дана схема тактованого RS-тригера, основу якого складає асинхрон-ний RS-тригер Т1 з інверсними входами (аналогічний зображеному на рис. 3, а).

Рис. 5. Одноступеневий синхронний RSС-тригер на БЛЕ І-НЕ

Щоби забезпечити перемикаючий логічний 0 на відповідному вході Т1, в схемі використані елементи І-НЕ. Логічний 0 на виході такого елемента буде при логічних 1 на його входах, тобто при S=1, С=1, або при R=1, С=1.

Тактований рівнем «1» RS-тригер функціонує у відповідності з табл. 3. З цієї таблиці видно, що даний тригер зберігає свій стан при С = 0 і працює як асинхронний RS-тригер при С=1 та має заборонену комбінацію RSC=111 (11, 15).

На рис 6 приведені часові діаграми тригера, зображеного на рис. 5 без врахування часу його перемикання. Перемикання тригера в стан Q=1 відбувається при S=1 з надходженням синхроімпульсу 2, коли на виході SI з’являється логічний 0. Сигнал SI =0, що виникає при поступленні синхроімпульсу 3, перемикання не викликає, так як до цього тригер вже встановлений в одиничний стан. Синхроімпульс 4 з сигналом R=1 забезпечує RI =0, що перемикає тригер в стан Q=0.

Таблиця 3

Номер набору n |

С |

S |

R |

Q t |

Q t+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

3 |

0 |

1 |

1 |

0 |

0 |

4 |

0 |

0 |

0 |

1 |

1 |

5 |

0 |

1 |

0 |

1 |

1 |

6 |

0 |

0 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

0 |

0 |

9 |

1 |

1 |

0 |

0 |

1 |

10 |

1 |

0 |

1 |

0 |

0 |

11 |

1 |

1 |

1 |

0 |

- |

12 |

1 |

0 |

0 |

1 |

1 |

13 |

1 |

1 |

0 |

1 |

1 |

14 |

1 |

0 |

1 |

1 |

0 |

15 |

1 |

1 |

1 |

1 |

- |

Рис. 6. Осцилограма RSС-тригера

В тексті тактований RS-тригер скорочено позначають символами RSC.

Тригер затримки (D-тригер).

D-тригер має один інформаційний

D-вхід і тактовий

С-вхід. Він складається з синхронного

RSC-тригера,

доповненого інвертором (рис. 7, а). При

С=1 потенціал D-входу

передається на S-вхід

тригера Т1 (S=D),

а на вході R встановлюється

потенціал R=![]() ,

тобто сигнали на S- і

R- входах

виявляються взаємно інвертованими

(S=

).

,

тобто сигнали на S- і

R- входах

виявляються взаємно інвертованими

(S=

).

а) б)

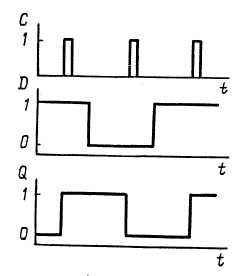

Рис. 7. Схема D-тригера (а), його часові діаграми (б)

Це приводить до того, що довільний сигнал на вході D створює на S- і R- входах комбінацію (S=1, R=0 або S=0, R=1), здатну переключити тригер в стан Q=S=D. Отже, при С=1 D- тригер є повторювачем: на виході Q повторюється потенціал входу D. Проте це повторення починається тільки з поступленням тактового імпульсу на вхід С, тобто із затримкою відносно потенціалу на D- вході, що змінився.

При С=0 тригер Т1 і D-вхід розділені; тому S=R=0 і тригер зберігає інформацію, що поступила при С=1 з D-входу.

На рис. 7, б приведені часові діаграми D-тригера. Вихід Q повторює стан D-входу з поступленням чергового тактового імпульсу на вхід С, тобто із затримкою.

D-тригер можна реалізувати на базі одноступеневого синхронного RSС-тригера на БЛЕ І-НЕ, якщо проміжні змінні RI та SI будуть описуватись логічними виразами

SI

=

![]() ;

RI

=

;

RI

=

![]() (1)

(1)

Вираз (1) відображає структуру синхронного D-тригера, що приведена на рис. 8. Дана схема широко використовується для побудови регістрів і в пристроях керування. Цей тригер функціонує у відповідності з табл. 4, звідки видно, що при С=0 він зберігає свій стан (Q t+1=Q t), а при С=1 Q t+1=D.

Рис. 8. Схема D-тригера в базисі І-НЕ

Таблиця 4

Номер набору n |

C |

D |

Q t |

Q t+1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

2 |

0 |

0 |

1 |

1 |

3 |

0 |

1 |

1 |

1 |

4 |

1 |

0 |

0 |

0 |

5 |

1 |

1 |

0 |

1 |

6 |

1 |

0 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |