- •Архитектура ом

- •Структура машин фон-Неймана, із загальною шиною, з каналами прямого доступу в пам'ять. Порівняльний аналіз і область застосування.

- •Апаратно-програмна реалізація обчислювальної системи. Призначення й основні функції операційної системи, однопрограмний і багатопрограмний режими роботи системи.

- •Класифікація операцій. Формати представлення команд і даних. Чотири-, трьох-, двох-, одно- і нуль-адресні команди. Определение наборов операций

- •Форматы команд

- •Способи адресації операндів. Безпосередня, пряма, непряма й індексна адресації. Призначення й область застосування.

- •Відносна, сторінкова і сегментна адресація. Переміщення програм і даних в оперативній пам'яті машини.

- •Операції переходу і розгалуження, їхня реалізація.

- •Операції звертання до підпрограм. Способи організації підпрограм. Організація динамічного розподілу пам'яті для підпрограм і їхніх даних.

- •Віртуальна пам'ять. Сторінкова організація віртуальної пам'яті. Алгоритми звертання до пам'яті.

- •Самообумовлені дані. Теги і дескриптори. Призначення і їхнє застосування.

- •Захист пам'яті. Призначення. Методи захисту верхніми і нижніми границями.

- •Захист пам'яті за допомогою ключів захисту. Структурна схема пам'яті з захистом. Достоїнства і недоліки.

- •Віртуальні процесори. Призначення і реалізація.

- •Віртуальні периферійні пристрої. Призначення, приклад реалізації.

- •Віртуальні машини. Призначення і приклад реалізації.

- •Операції вводу-виводу в ibm pc.

- •НкДтаЕ еом

- •Об'єкт діагностування, клас несправності, тест, система діагностування. Основні поняття і визначення.

- •Методи параметричного діагностування (пд).

- •Детермінований функціональний підхід до синтезу тестів.

- •Детермінований структурний підхід до синтезу тестів.

- •Обзор существующих методов

- •Застосування логічного моделювання для синтезу тесту.

- •Методи аналізу вихідних реакцій.

- •Ймовірний подхід до синтезу тестів.

- •Основні підходи до тестування мікропроцесорних пристроїв.

- •Попередні перетворення опису схем для синтезу схем.

- •Двійкова і двійково-кодована система числення.

- •Представлення числової інформації в еом.

- •Алгоритми додавання чисел.

- •Алгоритми множення чисел.

- •Алгоритми ділення чисел.

- •Виконання арифметичних операцій над числами з плаваючою крапкою.

- •Виконання арифметичних операцій у двійковій-десятковій системі числення.

- •Контроль по модулю арифметичних операцій.

- •Точність представлення чисел і виконання арифметичних операцій.

- •Проектування мпс

- •Мікропроцесори 2 і 3-го покоління фірми Intel.

- •Організація пам'яті в мікропроцесорних системах.

- •Організація переривань у мікропроцесорних системах.

- •Програмуємий послідовний інтерфейс мпс.

- •Організація вводу-виводу на базі віс пдп.

- •Реалізація внутрішніх системних інтерфейсів мпс.

- •Однокристальні мікро-еом фірми Intel.

- •Віс мпк 2 і 3-го поколінь фірми Intel.

- •Зовнішні інтерфейси мпс.

- •Структура пеом ibm pc.

- •Структура 32-х розрядних мікропроцесорів 4-го покоління фірми Intel.

- •Структура віс мікропроцесорного комплекту 4-го покоління для 32-х розрядних мікропроцесорних систем.

- •Комбінаційні схеми (кс). Основні поняття і визначення. Канонічний метод синтезу кс.

- •Комбінаційні схеми (кс). Аналіз кс. Основні методи аналізу кс.

- •Абстрактний автомат. Основні поняття і визначення. Класифікація. Способи завдання.

- •Способы описания и задания автоматов.

- •Канонічний метод синтезу кінцевого автомата.

- •Кодування внутрішніх станів автомата.

- •Кодирование состояний и сложность комбинационной схемы автомата.

- •Принцип мікропрограмного керування.

- •Структура операційного пристрою. Функції операційного і керуючого автоматів.

- •Мікропрограмні автомати (мпа). Інтерпретація граф-схеми алгоритму. Способы описания алгоритмов и микропрограмм

- •Канонічний метод синтезу мпа Милі з "жорсткою" логікою.

- •Канонічний метод синтезу мпа Мура з "жорсткою" логікою.

- •Достоинства и недостатки автоматов с жесткой логикой.

- •Синтез мпа Мура на базі регістру зсуву. Синтез управляющего автомата Мура на базе регистра сдвига.

- •Операційний автомат і мікропрограма додавання дробових чисел з фіксованою крапкою.

- •Операційний автомат і мікропрограма множення дробових чисел з фіксованою крапкою.

- •Двійкові-десяткові коди (д-коды) і їхньої властивості. Виконання арифметичних операцій у д-кодах.

- •Система числення в залишкових класах. Її особливість і застосування в обчислювальній техніці.

Методи аналізу вихідних реакцій.

Методы анализа схем можно разделить на прямые и косвенные. Прямые методы анализа опираются на различные алгебраические или иные формы, отражающие в том или ином виде структуру схемы. Они позволяют непосредственно синтезировать входные последовательности, необходимые для получения заданной реакции схемы. Например, синтезировать входные наборы, обеспечивающие появление на выходе схемы нулевого сигнала.

Классическая стратегия тестирования цифровых схем основана на формировании тестовых последовательностей, позволяющих обнаруживать заданные множества их неисправностей. При этом, для проведения процедуры тестирования, хранятся как сами тестовые последовательности, так и эталонные выходные реакции схем на их воздействие. В процессе тестирования при соответствии полученных реакций схемы эталонным она считается исправной, в противном случае схема содержит неисправность и находится в неисправном состоянии.

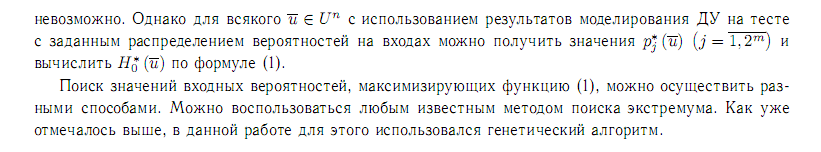

Основные функциональные блоки, используемые при тестировании цифровой схемы:

ГТВ – генератор тестовых воздействий (генератор М- последовательности)

ЦС – цифровая схема

МСА – многоканальный сигнатурный анализатор

Блок эталонных реакций - блок, хранящий сжатые выходные реакции

Логическая взаимосвязь функциональных блоков построена следующим образом: с генератора тестовых воздействий через цифровую схему сигналы поступают на схему сжатия информации (сигнатурный анализатор). Сжатые выходные реакции (сигнатуры) попадают на схему сравнения, где они сравниваются с эталонными сигнатурами, которые хранятся в блоке эталонных реакций. Далее информация попадает в устройство вывода информации о состоянии схемы.

Все данные блоки реализованы в виде математической модели на компьютере.

В данной работе в качестве блока сжатия информации смоделирован многоканальный сигнатурный анализатор.

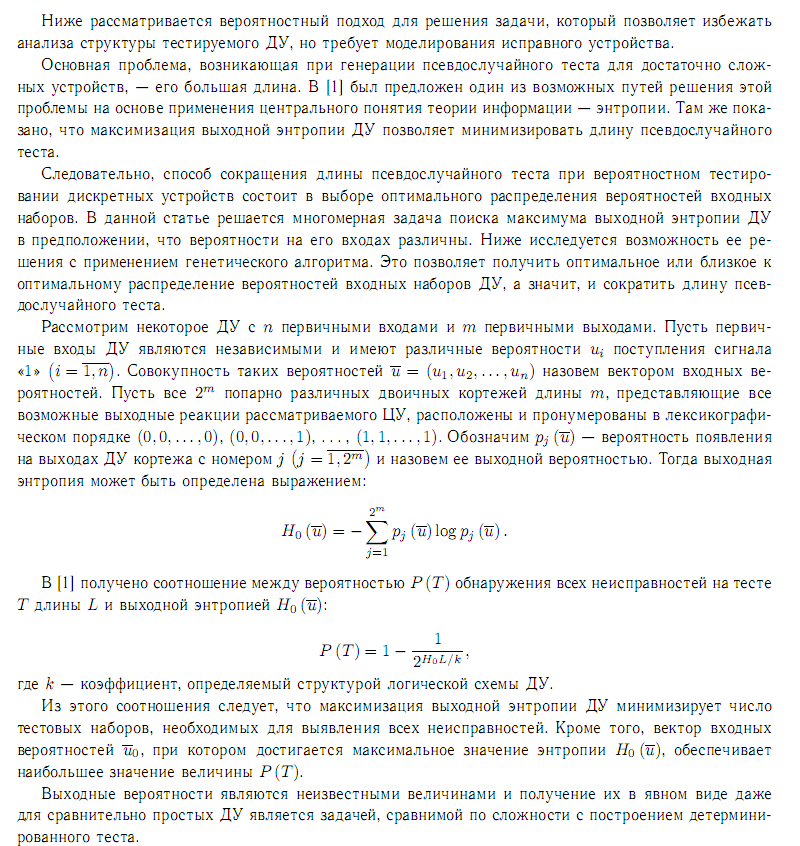

Ймовірний подхід до синтезу тестів.

![]()

Основні підходи до тестування мікропроцесорних пристроїв.

Тестирование микропроцессоров и микропроцессорных систем. Микропроцессоры и микропроцессорные системы представляют собой сложные объекты диагностирования, для которых не существует общих формальных методов синтеза тестов, таких, как мы имеем для комбинационных схем. «Сложность» объекта диагностирования заключается в следующих схемных особенностях.

Объем дискретных элементов составляет сотни тысяч и миллионы вентилей. Анализ объекта в целом на вентильном уровне практически неосуществим.

Структура объекта диагностирования неоднородна, иерархична, т.е. состоит из различных функциональных узлов с самыми различными видами топологических соединений: возможны аналоговые узлы, асинхронные узлы, генераторы, формирователи и т.п. Ограничен доступ к требуемому участку схемы для постановки диагностического эксперимента. Поэтому для микропроцессоров, как объектов диагностирования, класс константных неисправностей является неприемлемым. В данном случае микропроцессор либо микропроцессорная система рассматривается как программно-управляемый объект, для которого наиболее удобно рассматривать неисправности типа: неисполнение команды, неверное исполнение команды, исполнение незаданной команды и т.п.

Тест микропроцессора выглядит как проверка отдельных функций системы команд. Очевидно, что полнота теста будет определяться объемом выполненных команд, причем, особенно для команд регистровых пересылок, следует проверять правильность передачи как нулей, так и единиц.

При составлении теста микропроцессорной системы используют так называемую стратегию «раскрутки». То есть определяется некоторое ядро (как правило, ввод / вывод, простейшие команды пересылок и минимальная индикация), которое тестируется в первую очередь. Последующие проверки включают новые узлы объекта диагностирования (при этом полагают, что проверенная часть работоспособна).

Тест микропроцессора строится как совокупность функциональных тестов отдельных узлов и модулей:

- тест канала ввода / вывода;

- тест арифметико-логического устройства;

- тест программно-доступных регистров общего назначения;

- тест таймера;

- тест ОЗУ, ПЗУ;

- тест интерфейсов и периферийных устройств.

На этапе проектирования вычислительной системы синтез теста сопровождается логическим и событийным моделированием отдельных неисправностей на заданных функциональных проверках.