- •Содержание

- •Введение

- •Сапр и объекты проектирования в промышленности.

- •1.1 Классификация сапр

- •Понятие «промышленной» сапр

- •1.3 Основные объекты проектирования и производства в электронной промышленности

- •2 Промышленные системы автоматизированного проектирования электронных систем и устройств

- •2.1 Сапр программируемых логических интегральных схем

- •2.1.1 Обобщенная технология проектирования плис

- •Сапр производителей (вендоров) плис

- •2.1.2.1 Сапр фирмы Actel Сo

- •2.1.2.2 Сапр фирмы altera

- •2.1.2.3 Сапр фирмы atmel

- •2.1.2.4 Сапр фирмы minc Inc.

- •2.1.2.5 Сапр фирмы Xilinx

- •2.1.3 Универсальные сапр, поддерживающие проектирование плис

- •2.1.3.1 Сапр Synopsys

- •2.1.3.2 Сапр Cadence

- •2.1.3.3 Сапр Mentor Graphics

- •2.2 Подсистемы сапр, решающие отдельные задачи проектирования

- •2.2.1 Spice-подобные схемные симуляторы

- •2.2.2 Пакеты решения отдельных задач конструктор- ского проектирования

- •2.3 Сапр цифро-аналоговой и смешанной аппаратуры

- •2.3.1 Сапр Mentor Graphics

- •2.3.2 Сапр фирмы accel Technologies (accel eda)

- •2.3.3 Сапр p-cad

- •2.3.4 Сапр cadstar (zuken Ltd.)

- •2.3.5 Advanced cam Technologies (act)

- •Оценка эффективности и выбор сапр

- •Составляющие эффективности сапр

- •Методика расчета неэкономических показателей

- •3.3 Экономические показатели эффективности сапр

- •3.4 Организация проведения расчетов по экономической эффективности

- •3.5 Методы расчета экономической эффективности сапр

- •Литература

2.1.3.2 Сапр Cadence

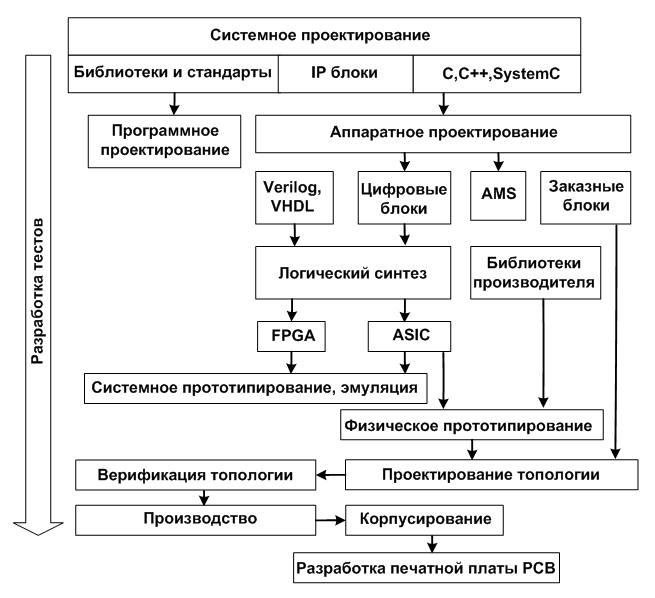

В целом проектирование БИС в среде Cadence, реализуемое сегодня на платформе Virtuoso, включает этапы, изображенные на рисунке 2.4.

• системное проектирование – построение модели системы на высоком уровне абстракции с использованием языков программирования C/C++ и SystemC, разбиение на программные и аппаратные модули, исследование параметров системы, получение спецификаций (набора требуемых параметров) на программные и аппаратные блоки;

• аппаратное проектирование и верификация – разработка на основе спецификации поведенческих моделей отдельных блоков системы с использованием языков Verilog/VHDL, реализация проекта в базисе библиотек производителя ИС, проверка программно-аппаратной реализации на соответствие спецификациям, полученным на системном уровне;

Рисунок 2.4- Этапы проектирования БИС в среде Cadence

• физическое прототипирование – предварительное размещение элементов, оценка потребляемой мощности, планирование шин питания и иерархии тактовых сигналов, качественная оценка возможных искажений сигнала;

• проектирование и верификация топологии кристалла – разработка топологии заказных блоков, трассировка на уровне ячеек, проверка правил проектирования топологии, экстракция паразитных параметров.

Информационные источники, использованные при подготовке раздела:

2.1.3.3 Сапр Mentor Graphics

Комплексное проектирование систем на базе PLD/FPGA/ASIC схем реализуется в среде САПР Mentor Graphics в соответствии со схемой (рис.2.5 ):

Из приведенной схемы можно выделить базовые программные решения, используемые Mentor Graphics при проектировании БИС:

HDL Designer – комплексное средство графического и текстового ввода проектов многомиллионных кристаллов FPGA/ASIC/SoC/FPSoC на основе языков VHDL, Verilog и их “смеси”, управления процессом проектирования и выпуска документации. Поддерживает концепции коллективного проектирования, в том числе с возможностью дистанционного доступа через Intranet или Internet, повторного использования стандартных решений (IP-blocks) и многовариантного проектирования;

Рисунок 2.5 - Комплексное проектирование систем на базе PLD/FPGA/ASIC схем в среде САПР Mentor Graphics

ModelSim – система цифрового моделирования проектов на основе VHDL, Verilog и “смешанных” описаний с встроенными функциями анализа производительности, индикации “активности” кода (code coverage), компаратора временных диаграмм и визуализатора Enhanced Dataflow Window. Основные функциональные возможности: высокая скорость моделирования для RTL и Gate проектов; единое моделирующее ядро и оптимизированная архитектура Native Compiled; интерактивная отладка и анализ с помощью модуля Debug Detective; интегрированный анализ Code Coverage; оптимизация скорости моделирования с помощью анализатора производительности Performance Analyzer; исчерпывающая трассировка сигналов Signal Spy; встроенный отладчик C; поддержка интерфейсов C и Tcl/Tk; поддержка ОС Unix/Windows/Linux;

Leonardo Spectrum – пакет логического синтеза и оптимизации CPLD/FPGA/ASIC на основе VHDL, Verilog и “смешанных” описаний проектов на базе библиотек всех ведущих изготовителей (более 100). Основные функциональные возможности: единая среда для проектирования CPLD, FPGA и ASIC; поддержка проектов, использующих любую комбинацию VHDL, Verilog и EDIF и стандартных решений в виде IP-блоков; высокое качество результатов (QoR) в сочетании с высокой скоростью синтеза; возможность генерации оптимизированного HDL-кода с помощью модуля HDLInventor; использование оптимизирующего алгоритма F.A.S.T.; полная интеграция со средствами размещения и траcсировки изготовителей кристаллов (P&R Integrator); усовершенствованные отладочные возможности схемотехнического браузера LeonardoInsight;

Precision Synthesis RTL – пакет логического синтеза, оптимизированный для FPGA. Высокая скорость синтеза и простота использования. Практически не требует ручной настройки (работа по принципу “нажал кнопку – получил результат”). Высокое качество результатов с первого прохода. Оптимизация временных параметров (до 30%). Полностью интегрирован с HDL Designer, ModelSim, LeonardoSpectrum, FPGA Advantage;

Precision Physical Synthesis - пакет физического синтеза, ориентированный на оптимизированные, с точки зрения производительности, FPGA-проекты. В отличие от традиционного подхода RTL Synthesis + P&R, как правило, требующего большого числа итераций, Precision Physical реализует временную оптимизацию на этапе синтеза на основе конкретных физических параметров библиотек изготовителей, что позволяет сократить или полностью исключить необходимость повторных итераций размещения и трассировки;

Catapult C Synthesis - пакет поведенческого синтеза, позволяющий получить синтезируемое RTL-описание проекта (VHDL или Verilog) на основе входного функционального описания на С или С++. Основное отличие от других маршрутов проектирования верхнего уровня (например, на основе MATLAB, System C, Handle C и других) состоит в том, что Catapult C не требует никаких промежуточных представлений (System C, Handle C), а непосредственно синтезирует исходный С-код в том виде, в котором он был написан инженером-системщиком, что существенно сокращает цикл проектирования. При этом результат зависит не от исходного кода, а от тех ограничений и настроек, которые выполняются непосредственно в Catapult C;

FPGA Advantage (HDL Designer + ModelSim + Leonardo Spectrum/Precision Synthesis) – комплекс, включающий все модули маршрута проектирования CPLD/FPGA/ASIC. Оптимальное решение по стоимости.

Информационные источники, использованные при подготовке раздела: