- •Содержание

- •Введение

- •1. Функции алгебры логики и их свойства

- •1.1. Функции одной переменной

- •1.2. Функции двух переменных

- •1.4. Обратные и инверсные логические функции

- •1.4.1. Обратные функции

- •Прямое соответствие (рис. 2,а)

- •Обратное соответствие (рис. 2,б)

- •1.4.2. Инверсные функции

- •1.5. Приоритеты операций

- •1.6. Законы и тождества булевой алгебры

- •1.7. Вопросы для самоконтроля

- •2. Формы задания логических функций

- •2.1. Словесная форма

- •2.2. Табличная форма

- •2.3. Задание формулой

- •2.3.1. Совершенная дизъюнктивная нормальная форма

- •Выводы:

- •Правила составления сднф

- •2.3.2. Совершенная конъюнктивная нормальная форма

- •Правила составления скнф

- •2.3.3. Дизъюнктивные и конъюнктивные нормальные формы

- •2.3.4. Минтермы, макстермы и их свойства

- •2.4. Другие формы задания логических функций

- •2.5. Вопросы для самоконтроля

- •3. Функционально полные системы функций

- •Штрих Шеффера

- •Стрелка Пирса

- •Импликация и «0»

- •3.1. Теорема Поста–Яблонского

- •3.1.1. Определение минимального базиса

- •3.1.2. Функции, не сохраняющие 0 и 1

- •3.1.3. Двойственная функция

- •3.1.4. Монотонная функция

- •3.3. Вопросы для самоконтроля

- •4. Минимизация логических функций

- •4.1. Расчетный метод

- •4.1.1. Склеивание

- •4.1.2. Поглощение

- •4.1.3. Развертывание

- •4.2. Карты Карно

- •4.3. Минимизация систем логических уравнений

- •4.4. Частично определенная логическая функция

- •4.5. Вопросы для самоконтроля

- •5. Синтез и анализ логических схем

- •5.1. Схемы на переключателях, диодах и транзисторах

- •5.2. Схемы на логических элементах

- •5.2.1. Реализация функции на элементах и, или, не

- •5.2.2. Реализация функции на элементах и–не

- •5.2.3. Реализация функции на элементах или–не

- •5.3. Анализ схем

- •5.4. Оценка качества схем

- •5.5. Вопросы для самоконтроля

- •6. Булева производная

- •6.1. Контроль работоспособности логических схем

- •6.2. Построение тестов методом булевой производной

- •6.2.1. Свойства булевой производной

- •6.3. Вопросы для самоконтроля

- •7. Примеры преобразований логических функций

- •7.1. Представление логических функций в системе и, или, не

- •7.2. Построение таблиц истинности

- •7.3. Преобразование кнф в днф и днф в кнф Преобразование кнф в днф

- •Преобразование днф в кнф

- •7.4. Доказательства равенства логических функций

- •7.5. Разложение логических функций по переменным

- •7.5.1. Последовательное разложение по всем переменным Разложение по п. 1.6.13 (1)

- •Разложение по п. 1.6.13 (2)

- •7.5.2. Параллельное разложение по всем переменным разложение по п. 1.6.13 (1)

- •Разложение по п. 1.6.13 (2)

- •8. Домашняя работа

- •8.1. Задание

- •8.2. Выполнение

- •Проверить двумя способами эквивалентность формул

- •С помощью эквивалентных преобразований привести формулу к днф, кнф, сднф, скнф, получить полином Жегалкина.

- •С помощью карт Карно найти все минимальные днф функции трех переменных ƒ(X,y,z).

- •С помощью карт Карно найти все минимальные днф и кнф булевой функции четырех переменных , заданной вектором своих значений.

- •Является ли полной система функций? Образует ли она минимальный базис?

- •9. Список литературы

- •Введение в булеву алгебру

- •Гоу впо “Московский государственный университет приборостроения и информатики”

- •107996, Москва, ул. Стромынка, 20

5.5. Вопросы для самоконтроля

Какова последовательность действий в процессе создания и анализа схемы, реализующей логическую функцию?

Как реализуются логические функции с помощью контактов переключателей и реле? Приведите примеры.

Приведите примеры реализации логических функций на диодах и транзисторах.

Приведите условные графические обозначения типовых логических элементов.

Какова последовательность действий при реализации логической функции на элементах И, ИЛИ, НЕ?

Какова последовательность действий при реализации логической функции на элементах И–НЕ?

Какова последовательность действий при реализации логической функции на элементах ИЛИ–НЕ?

Какова последовательность действий при реализации логической функции, если имеется ограничение на число входов элементов?

Как проводится анализ комбинационной логической схемы?

Как оценивается качество логических схем?

6. Булева производная

6.1. Контроль работоспособности логических схем

Булеву алгебру применяют не только для анализа и синтеза логических схем, но также и для построения контролирующих тестов таких схем.

В простейшем случае проверку работоспособности логической схемы можно провести сравнением на всех возможных наборах входных переменных значений функции, реализуемой схемой, и требуемой. Однако отличия этих функций при наличии в схеме неисправности проявляются только на некоторых наборах входных переменных, а поэтому, с целью экономии времени и средств на проверку работоспособности логической схемы, необходимо знать эти наборы.

Подачу на логическую схему заранее определенной последовательности наборов входных переменных (входных наборов) и анализ ее реакции на эти воздействия называют тестовым контролем.

Совокупность входных наборов, позволяющую определить работоспособность логической схемы, называют контролирующим тестом.

Выбор входных наборов для контроля работоспособности логической схемы осуществляется из тех соображений, чтобы реакции исправной схемы и схемы с любой неисправностью отличались хотя бы на одном наборе. Неисправности, для которых невозможно найти ни одного такого набора, называются необнаруживаемыми.

Неисправность логической схемы – это следствие явлений или действий, вызывающих переход схемы в неисправное состояние. Различают неисправности одиночные и кратные, устойчивые и неустойчивые, произвольные и специальные, детерминированные и стохастические.

Большинство

существующих методов построения тестов

эффективны только при одиночных,

устойчивых, детерминированных

неисправностях вида "константа 1"

и "константа 0". Именно такие

неисправности будут иметься в виду в

настоящем пособии (при необходимости

будем обозначать эти неисправности

![]() 1

и

0).

1

и

0).

У одного логического элемента могут быть константные неисправности четырех видов:

при любом входном наборе сигнал на выходе элемента имеет постоянное значение 1;

при любом входном наборе сигнал на выходе элемента имеет постоянное значение 0;

на каком–либо входе элемента сигнал имеет постоянное значение 1;

на каком–либо входе элемента сигнал имеет постоянное значение 0.

Если элемент имеет n входов и один выход, то количество его возможных одиночных константных неисправностей равно 2(n + 1).

Введем понятие существенной переменной.

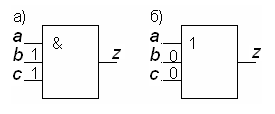

Для логического элемента И (рис. 18,а) можно записать

z = a·b·c.

Если положить b = 1 и c = 1, то в соответствии с законами тождественных преобразований булевой алгебры получим

z = a·1·1 = a.

Иными словами, если b = 1 и c = 1, то вход a управляет выходом z.

Рисунок 18 – Задание существенных переменных

а) для элемента И, б) для элемента ИЛИ

Для логического элемента ИЛИ (рис. 18,б) имеем

z = a v b v c.

Если здесь положить b = 0 и c = 0 , то получим

z = а v 0 v 0 = a.

То есть, для элемента ИЛИ вход a управляет выходом, если на остальные входы подать значение 0.

Входная переменная логического элемента называется существенной, если она и только она определяет значение выхода этого элемента.

Чтобы некоторую входную переменную элемента И (И–НЕ) сделать существенной, необходимо другим его входным переменным присвоить значения 1 (рис. 18,а).

Чтобы некоторую входную переменную элемента ИЛИ (ИЛИ–НЕ) сделать существенной, необходимо другим его входным переменным присвоить значения 0 (рис. 18,б).

Любая одиночная константная неисправность типа 0 или 1 существенного входа (входа, к которому приложена существенная переменная) или выхода элементов И и ИЛИ может быть обнаружена путем наблюдения значения выхода элемента при подаче на существенный вход значения существенной переменной, обратного значению неисправности.

Неисправности существенного входа элементов И–НЕ, ИЛИ–НЕ могут быть обнаружены при тех же условиях, что и для элементов И и ИЛИ. Неисправности выходов элементов И–НЕ, ИЛИ–НЕ могут быть обнаружены при подаче на существенный вход значений, равных значениям неисправностей.