- •1 Задачи анализа;

- •2 Задачи синтеза;

- •3 Задачи идентификации.

- •Основные задачи теории кс

- •1. Задачи анализа;

- •2. Задачи синтеза;

- •3. Задачи идентификации.

- •2. Высокой интенсивностью взаимодействия и вытекающим отсюда требованием уменьшения времени ответа.

- •Функционирование кс

- •Основные задачи теории вычислительных систем

- •Общая характеристика методов теории вычислительных систем

- •3. Классификация вычислительных систем

- •Характеристики производительности и надежности кс

- •Характеристики надежности кс

- •1 Холодное резервирование. Работает только основной канал.

- •2 Нагруженный резерв. Включены оба канала (резервный канал занимается посторонними задачами). Время перехода на основную задачу меньше чем в холодном резерве.

- •Общая характеристика методов теории вычислительных систем

- •Характеристики производительности кс

- •1. Номинальная производительность ;

- •2. Комплексная производительность ;

- •3. Пакеты тестовых программ spec XX

- •Характеристики надежности кс

- •1 Холодное резервирование. Работает только основной канал.

- •2 Нагруженный резерв. Включены оба канала (резервный канал занимается посторонними задачами). Время перехода на основную задачу меньше чем в холодном резерве.

- •4) Указывается начальное состояние системы;

- •8) Находятся показатели качества вс на основе найденных вероятностей состояния системы.

- •Анализ надежности кс со сложной структурой

- •2.Расчет надежности кс

- •2. Для каждой вершины можно вычислить среднее количество попаданий вычислительного процесса в эту вершину по формуле

- •1. Разбить множество операторов на классы:

- •Модели вычислительных систем как систем массового обслуживания

- •1 Общие понятия и определения

- •Например m/m/1

- •2 Параметры систем массового обслуживания

- •Модели массового обслуживания вычислительных систем|

- •1. Представление вычислительной системы в виде стохастической сети

- •2. Потоки заявок

- •3. Длительность обслуживания заявок

- •Характеристики одноканальных смо

- •Многопроцессорные системы

- •5. Характеристики бесприоритетных дисциплин обслуживания

- •1) В порядке поступления (первой обслуживается заявка, поступившая раньше других);

- •2) В порядке, обратном порядку поступления заявок (первой обслуживается заявка, поступившая позже других);

- •3) Наугад, т. Е. Путем случайного выбора из очереди.

- •6. Характеристики дисциплины обслуживания с относительными приоритетами заявок

- •3.8. Характеристики дисциплин обслуживания со смешанными приоритетами

- •§ 3.9. Обслуживание заявок в групповом режиме

- •§ 3.10. Смешанный режим обслуживания заявок

- •§ 3.11. Диспетчирование на основе динамических приоритетов

- •§ 3.12. Оценка затрат на диспетчирование

- •1.Определяется интенсивность потока заявок I в смо Si из системы алгебраических уравнений

- •2.Вычисляются коэффициенты передач для каждой смо

- •3.Определяется среднее время обслуживания Ui заявки в смо Si :

- •6.Для моделирующей сети в целом характеристики п.5 определяются как

- •2.Расчет характеристик мультипроцессорной системы

- •1) Имеет доступ к общей памяти;

- •1.Средняя длина очереди заявок, ожидающих обслуживания в системе:

- •3. Среднее время пребывания заявок в системе :

- •Основные задачи теории кс

- •1. Задачи анализа;

- •2. Задачи синтеза;

- •3. Задачи идентификации.

- •1) С неограниченным временем пребывания заявок;

- •2) С относительными ограничениями на время пребывания заявок;

- •3) С абсолютными ограничениями на время пребывания заявок;

- •2.4. Контроллеры и сетевые комплексы ge Fanuc

- •Модели 311,313/323, 331

- •Коммуникационные возможности серии 90-30

- •2.4.3. Контроллеры VersaMax

- •2.4.4. Программное обеспечение

- •Общая характеристика протоколов и интерфейсов асу тп

- •2. Протоколы и интерфейсы нижнего уровня.

- •2. Основные технические характеристики контроллеров и программно-технических комплексов

- •Требования к корпоративной сети

- •2) Одновременное решение различных задач или частей одной задачи;

- •3) Конвейерная обработка информации.

- •1. Суть проблемы и основные понятия

- •1.1 Главные этапы распараллеливания задач

- •1.2 Сведения о вычислительных процессах

- •1.3 Распределенная обработка данных

- •1. Классификации архитектур параллельных вычислительных систем

- •1.1 Классификация Флинна

- •1. Процессоры

- •Память компьютерных систем

- •Простые коммутаторы

- •Простые коммутаторы с пространственным разделением

- •Составные коммутаторы

- •Коммутатор Клоза

- •Баньян-сети

- •Распределенные составные коммутаторы

- •Коммутация

- •Алгоритмы выбора маршрута

- •Граф межмодульных связей Convex Exemplar spp1000

- •Граф межмодульных связей мвс-100

- •3. Граф межмодульных связей мвс-1000

- •1. Построения коммуникационных сред на основе масштабируемого когерентного интерфейса sci

- •2. Коммуникационная среда myrinet

- •3. Коммуникационная среда Raceway

- •4. Коммуникационные среды на базе транспьютероподобных процессоров

- •1. Структура узла

- •2. Пакеты и свободные символы

- •3. Прием пакетов

- •4. Передача пакетов

- •5. Управление потоком

- •1. Структура адресного пространства

- •2. Регистры управления и состояния

- •3. Форматы пакетов

- •Когерентность кэш-памятей

- •1. Организация распределенной директории

- •2. Протокол когерентности

- •3. Алгоритм кэширования.

- •1 . Основные характеристики

- •1.2. Происхождение

- •1.3. Механизм когерентности

- •1. 4. Предназначение

- •1. 5. Структура коммуникационных сред на базе sci

- •1. 6. Физическая реализация

- •1. 7. Обозначение каналов

- •2. Реализация коммуникационной среды

- •2.1. На структурном уровне коммуникационная среда состоит из трех компонентов, как показано на рис. 2.1:

- •Масштабируемый когерентный интерфейс sci

- •Сетевая технология Myrinet

- •Коммуникационная среда Raceway

- •Коммуникационные среды на базе транспьютероподобных процессоров

- •1.Информационные модели

- •1.2. Мультипроцессоры

- •1.3. Мультикомпьютеры

- •Сравнительный анализ архитектур кс параллельного действия.

- •Архитектура вычислительных систем

- •Smp архитектура

- •Симметричные мультипроцессорные системы (smp)

- •Mpp архитектура

- •Массивно-параллельные системы (mpp)

- •Гибридная архитектура (numa)

- •Системы с неоднородным доступом к памяти (numa)

- •Pvp архитектура

- •Параллельные векторные системы (pvp)

- •1. Системы с конвейерной обработкой информации

- •1.2 Мультипроцессоры uma с много- ступенчатыми сетями

- •Мультипроцессоры numa

- •Мультипроцессор Sequent numa-q

- •Мультикомпьютеры с передачей сообщений

- •1. Общая характеристика кластерных систем.

- •2.Особенности построения кластерных систем.

- •Планирование работ в cow.

- •Без блокировки начала очереди (б); заполнение прямоугольника «процессоры-время» (в). Серым цветом показаны свободные процессоры

- •Общие сведения

- •Общие сведения

- •Логическая структура кластера

- •Логические функции физического узла.

- •Устройства памяти

- •Программное обеспечение

- •Элементы кластерных систем

- •1.1. Характеристики процессоров

- •Рассмотрим в начале процессор amd Opteron/Athlon 64.

- •Примеры промышленых разработок

- •Кластерные решения компании ibm

- •Диаграмма большого Linux-кластера.

- •Аппаратное обеспечение

- •Вычислительные узлы, выполняющие основные вычислительные задачи, для которых спроектирована система.

- •Программное обеспечение

- •Кластерные решения компании hp

- •Кластерные решения компании sgi

- •Производительность операций с плавающей точкой

- •Производительность памяти

- •Производительность системы ввода/вывода Linux

- •Масштабируемость технических приложений

- •Системное программное обеспечение

- •Архитектура san

- •Компоненты san

- •Примеры решений на основе san

- •San начального уровня

- •San между основным и резервным центром

- •Практические рекомендации

- •Построение san

- •Заключение

- •Принципы построения кластерных архитектур.

- •Оценки производительности параллельных систем

- •1) Имеет доступ к общей памяти;

- •2) Имеет общий доступ к устройствам ввода-вывода;

- •3) Управляется общей операционной системой, которая обеспечивает требуемое взаимодействие между процессорами и выполняемыми им программами как на аппаратном, так и на программном уровне.

- •4 Вероятность того, что в момент поступления очередной заявки все n процессоров заняты обслуживанием

- •Выбор коммутационного компонента.

- •Проблема сетевой перегрузки.

- •1. Обзор современных сетевых решении для построения кластеров.

- •1000-Мега битный вариант Ethernet

- •Организация внешней памяти

- •Эффективные кластерные решения

- •Концепция кластерных систем

- •Разделение на High Avalibility и High Performance системы

- •3. Проблематика High Performance кластеров

- •Проблематика High Availability кластерных систем

- •Смешанные архитектуры

- •6.Средства реализации High Performance кластеров

- •7.Средства распараллеливания

- •8.Средства реализации High Availability кластеров

- •9.Примеры проверенных решений

- •Архитектура san

- •Компоненты san

- •Примеры решений на основе san

- •San начального уровня

- •San между основным и резервным центром

- •Практические рекомендации

- •Построение san

- •Заключение

- •Symmetrix десять лет спустя

- •Матричная архитектура

- •Средства защиты данных

- •Ревизионизм и фон-неймановская архитектура

- •Литература

- •Связное программное обеспечение для мультикомпьютеров

- •1. Синхронная передача сообщений.

- •2. Буферная передача сообщений.

- •Планирование работ в cow

- •Средства распараллеливания

- •7.Средства распараллеливания

- •2. Кластерн ый вычислительн ый комплекс на основе интерфейса передачи сообщений

- •2.2 Программная реализация интерфейса передачи сообщений

- •2.3 Структура каталога mpich

- •2.4 «Устройства» mpich

- •2.5 Выполнение параллельной программы

- •2.6 Особенности выполнения программ на кластерах рабочих станций

- •2.7 Тестирование кластерного комплекса

- •Параллельная виртуальная машина

- •3 Кластерн ый вычислительн ый комплекс на основе пАраллельной виртуальной машины

- •3.1 Параллельная виртуальная машина

- •3.1.1 Общая характеристика

- •3.1.2 Гетерогенные вычислительные системы

- •3.1.3 Архитектура параллельной виртуальной машины

- •3.2 Настройка и запуск параллельной виртуальной машины

- •3.3 Структура каталога pvm

- •3.4 Тестирование параллельной виртуальной машины

- •На рисунке 3.2 представлена диаграмма, отображающая сравнение производительности коммуникационных библиотек mpi и pvm.

- •3.5 Сходства и различия pvm и mpi

- •4 . Кластерн ый вычислительн ый комплекса на основе программного пакета openMosix

- •4.1 Роль openMosix

- •4.2 Компоненты openMosix

- •4.2.1 Миграция процессов

- •4.2.2 Файловая система openMosix (oMfs)

- •4.3 Планирование кластера

- •4.4 Простая конфигурация

- •4.4.1 Синтаксис файла /etc/openmosix.Map

- •4.4.2 Автообнаружение

- •4. 5. Пользовательские утилиты администрирования openMosix

- •4. 6. Графические средства администрирования openMosix

- •4. 6.1 Использование openMosixView

- •4. 6.1.2 Окно конфигурации. Это окно появится после нажатия кнопки “cluster-node”.

- •4. 6.1.3 Окно advanced-execution. Если нужно запустить задания в кластере, то диалог "advanced execution" может сильно упростить эту задачу.

- •4.6.1.4 Командная строка. Можно указать дополнительные аргументы командной строки в поле ввода вверху окна. Аргументы приведены в таблице 9.2.

- •4. 6.2.2 Окно migrator. Этот диалог появляется, если кликнуть на каком-либо процессе из окна списка процессов.

- •4. 6.2.3 Управление удалёнными процессами. Этот диалог появляется при нажатии кнопки “manage procs from remote”

- •4.5.3 Использование openMosixcollector

- •4. 6.4 Использование openMosixanalyzer

- •4. 6.4. 1 Окно load-overview. Здесь отображается хронология нагрузки openMosix.

- •4. 6.4. 2 Статистическая информация об узле

- •4.5.4.3 Окно memory-overview. Здесь представляется обзор использования памяти (Memory-overview) в openMosixanalyzer.

- •4. 6.4.4 Окно openMosixhistory

- •4. 6.5 Использование openMosixmigmon

- •4.6 Список условных сокращений

- •Перечень ссылок

- •Общие сведения

- •2. Создание Windows-кластера

- •Суперкомпьютерная Программа "скиф"

- •Описание технических решений

- •Направления работ

- •Основные результаты

- •Кластер мгиу

- •Содержание

- •Понятие о кластере

- •Аппаратное обеспечение

- •Пропускная способность и латентность

- •1. Определение распределенной системы

- •2.1. Соединение пользователей с ресурсами

- •2.2. Прозрачность

- •Прозрачность в распределенных системах

- •2.3. Открытость

- •2.4. Масштабируемость

- •3.1. Мультипроцессоры

- •3.2. Гомогенные мультикомпьютерные системы

- •3.3. Гетерогенные мультикомпьютерные системы

- •4. Концепции программных решений рс

- •4.1. Распределенные операционные системы

- •4.2. Сетевые операционные системы

- •4.3. Программное обеспечение промежуточного уровня

- •5. Модель клиент-сервер рс

- •5.1. Клиенты и серверы

- •5.2. Разделение приложений по уровням

- •5.3. Варианты архитектуры клиент-сервер

- •Формы метакомпьютера

- •Настольный суперкомпьютер.

- •2. Интеллектуальный инструментальный комплекс.

- •Сетевой суперкомпьютер.

- •Проблемы создания метакомпьютера

- •Сегодняшняя архитектура метакомпьютерной среды

- •Взаимосвязь метакомпьютинга с общими проблемами развития системного по

- •5. Модель клиент-сервер рс

- •5.1. Клиенты и серверы

- •5.2. Разделение приложений по уровням

- •5.3. Варианты архитектуры клиент-сервер

- •Symmetrix десять лет спустя

- •Матричная архитектура

- •Средства защиты данных

- •Ревизионизм и фон-неймановская архитектура

- •Однородные вычислительные среды

- •Однокристальный ассоциативный процессор сам2000

- •Модели нейронных сетей

- •Модели инс

- •Оптимизационные системы.

- •Неуправляемые системы распознавания образов.

- •Системы feed forward.

- •Элементы нейрологики с позиции аппаратной реализации

- •Реализация нейронных сетей

- •Программные нейрокомпьютеры

- •Программно-аппаратные нейрокомпьютеры

- •Практическое использование инс

Граф межмодульных связей Convex Exemplar spp1000

В качестве примера реального графа межмодульных связей рассмотрим структуру системы Convex Exemplar SPP1000.

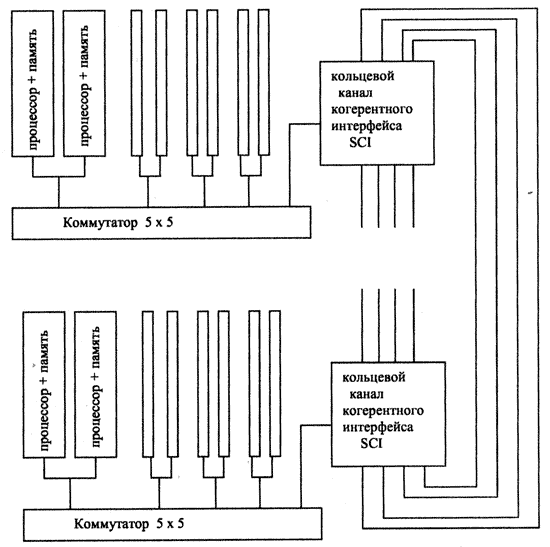

В основе каждого составного блока системы лежит прямоугольный коммутатор (5х5), до 16 подобных блоков объединяются каналами “точка-точка” в кольцо (одномерный тор), состоящее из четырех независимых подканалов.

Рис. 2.4. Граф межмодульных связей Convex Exemplar SPP1000

Внутри каждого блока четыре входа и выхода прямоугольного коммутатора (5х5) используются для взаимодействия устройств внутри блока (при этом в каждом блоке располагается по два процессора), пятые вход и выход используются для объединения блоков в кольцо. При этом каждый из четырех кольцевых каналов рассматривается как независимый ресурс, и система сохраняет работоспособность до тех пор, пока существует хотя бы один функционирующий кольцевой канал.

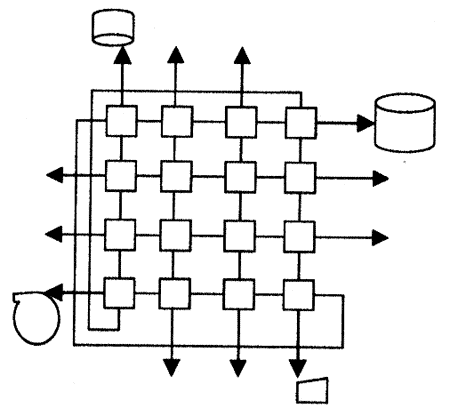

Граф межмодульных связей мвс-100

Система МВС-100 предлагает блочный подход к построению архитектуры параллельной вычислительной системы. Структурный модуль системы состоит из 16 вычислительных узлов, образующих матрицу 4х4 (рис. 2.5). Угловые узлы соединяются попарно по диагонали, таким образом, максимальная длина пути между любой парой элементов равна трем. В исходной же матрице 4 х 4 эта длина равна шести. Каждый блок имеет 12 выходов, что позволяет объединять их в более сложные структуры.

Рис. 2.5. Структурный модуль МВС-100

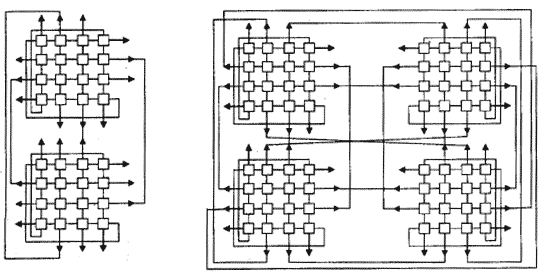

Для МВС-100 базовый вычислительный блок содержит 32 узла. Такой блок строится из двух структурных модулей в соответствии со схемой, приведенной на рис. 2.6. В этом случае максимальная длина пути между любой парой вычислительных узлов равна пяти. При этом остается 16 свободных связей, что позволяет продолжить объединение. При объединении двух базовых блоков по схеме, приведенной на рис. 6 (64 вычислительных узла) максимальная длина пути составит 6, как и в гиперкубе, количество свободных связей будет равно 16.

Рис. 2.6. Варианты объединения структурных модулей МВС-100

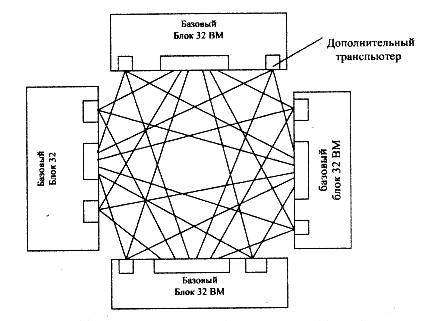

3. Граф межмодульных связей мвс-1000

Архитектура системы МВС-1000 аналогична архитектуре МВС-100. Основой системы МВС-1000 является масштабируемый массив процессорных узлов.

Каждый узел содержит вычислительный микропроцессор Alpha 21164 с производительностью 2 GFLOPS при тактовой частоте 500 MHz и оперативную память объемом 128 MB, с возможностью расширения. Процессорные узлы взаимодействуют через коммуникационные процессоры TMS320C44 производства Texas Instruments, имеющие по 4 внешних канала (линка) с общей пропускной способностью 80 Мбайт/с (20 Мбайт/с каждый).

Также разрабатывается вариант системы с использованием коммуникационных процессоров SHARC (ADSP 21060) компании Analog Devices, имеющих по 6 каналов с общей пропускной способностью до 240 Мбайт/с (40 Мбайт/с каждый). Процессорные узлы связаны между собой по оригинальной схеме, сходной с топологией двухмерного тора (для 4-линковых узлов). Структурный модуль МВС-1000 состоит из 16 вычислительных модулей, образующих матрицу 4x4, в которой четыре угловых элемента соединяются через транспьютерные линки по диагонали попарно. Оставшиеся 12 линков предназначаются для подсоединения внешних устройств (4 линка угловых ВМ) и соединений с подобными ВМ.

Конструктивным образованием МВС-1000 является базовый вычислительный блок, содержащий 32 вычислительных модуля. Максимальная длина пути между любыми из 32 вычислительных модулей равна пяти, при этом число свободных линков после комплектации блока составляет 16, что позволяет продолжить процедуру объединения. Возможная схема объединения четырех базовых блоков в 128-процессорную систему приведена на рис. 2.7.

Рис. 2.7. Структура 128-процессорной системы МВС-1000, 4 базовых блока.

Выводы

В больших мультипроцессорах взаимодействие между

процессорами и удаленной памятью почти всегда состоит

в том, что процессор посылает в память сообщение, так

называемый пакет, который запрашивает определенные

данные, а память посылает процессору ответный пакет.

Интерфейсы — это устройства, которые вводят и

выводят сообщения из центральных процессоров

и модулей памяти.

Важное свойство сети межсоединений — это ее пропускная

способность, то есть количество данных, которое она способна

передавать в секунду.

Очень важная характеристика — бисекционная пропускная

способность. Чтобы вычислить это число, нужно мысленно

разделить сеть межсоединений на две равные

(с точки зрения числа узлов) несвязанные части путем

удаления ряда дуг из графа. Затем нужно вычислить

общую пропускную способность дуг, которые мы удалили.

Часто основная цель при разработке сети межсоединений —

сделать бисекционную пропускную способность максимальной.

Сети межсоединений можно характеризовать по их размерности.

Размерность определяется по числу возможных вариантов

перехода из исходного пункта в пункт назначения.

Диаметр сети— это логарифм по основанию 2 от числа узлов.

Коммуникационные среды вычислительных систем

(ВС) состоят из адаптеров вычислительных модулей (ВМ) и

коммутаторов, обеспечивающих соединения между ними.

Используются как простые коммутаторы, так и составные, компонуемые из набора простых.

Типы простых коммутаторов:

- с временным разделением;

- с пространственным разделением.

Достоинства: простота управления и высокое быстродействие. Недостатки: малое количество входов и выходов.Простые коммутаторы могут соединять лишь малое число ВМ в силу физических ограничений, однако обеспечивают при этом минимальную задержку при установлении соединения.

Составные коммутаторы, обычно строящиеся из простых в виде многокаскадных схем с помощью линий «точка-точка», преодолевают ограничение на малое количество соединений, однако увеличивают и задержки.

Обзор технологий для построения коммуника-ционных сред

Конкретная реализация соединения компьютеров между собой, с памятью и с внешними устройствами называется коммуникационной средой компьютера. Одна из самых простых реализаций – это использование общей шины, к которой подключаются как процессоры, так и память. Сама шина состоит из определенного числа линий связи, необходимых для передачи адресов, данных и управляющих сигналов между процессором и памятью. Этот способ реализован в SMP системах. Основным недостатком таких систем является плохая масштабируемость. Увеличение, даже незначительное числа устройств на шине вызывает заметные задержки при обмене с памятью и катастрофическое падение производительности системы в целом. Необходимы другие подходы для построения коммуникационной среды, и одним из них является разделение памяти на независимые модули и обеспечение возможности доступа разных процессоров к различным модулям одновременно посредством использования различного рода коммутаторов.

При этом возможны различные конфигурации получающихся систем связи. Так, в компьютерах семейства Cray T3D/T3E все процессоры были объединены специальными высокоскоростными каналами в трехмерный тор, в котором каждый вычислительный узел имел непосредственные связи с шестью соседями.

Топологические структуры сетей межсоединений и их характеристики

В компьютерах IBM SP/2 взаимодействие процессоров происходит через иерархическую систему коммутаторов, также обеспечивающую возможность соединения каждого процессора с любым другим. Эти оригинальные уникальные решения значительно увеличивают цену суперкомпьютеров.

Примеры реализации.

В настоящее время существует ряд технологий по для построения соединительных сетей мультипроцессоров мультикоипьютеров:

Масштабируемый когерентный интерфейс SCI

Сетевая технология Myrinet

Коммуникационная среда Raceway

Коммуникационные среды на базе транспьютероподобных процессоров