- •1 Задачи анализа;

- •2 Задачи синтеза;

- •3 Задачи идентификации.

- •Основные задачи теории кс

- •1. Задачи анализа;

- •2. Задачи синтеза;

- •3. Задачи идентификации.

- •2. Высокой интенсивностью взаимодействия и вытекающим отсюда требованием уменьшения времени ответа.

- •Функционирование кс

- •Основные задачи теории вычислительных систем

- •Общая характеристика методов теории вычислительных систем

- •3. Классификация вычислительных систем

- •Характеристики производительности и надежности кс

- •Характеристики надежности кс

- •1 Холодное резервирование. Работает только основной канал.

- •2 Нагруженный резерв. Включены оба канала (резервный канал занимается посторонними задачами). Время перехода на основную задачу меньше чем в холодном резерве.

- •Общая характеристика методов теории вычислительных систем

- •Характеристики производительности кс

- •1. Номинальная производительность ;

- •2. Комплексная производительность ;

- •3. Пакеты тестовых программ spec XX

- •Характеристики надежности кс

- •1 Холодное резервирование. Работает только основной канал.

- •2 Нагруженный резерв. Включены оба канала (резервный канал занимается посторонними задачами). Время перехода на основную задачу меньше чем в холодном резерве.

- •4) Указывается начальное состояние системы;

- •8) Находятся показатели качества вс на основе найденных вероятностей состояния системы.

- •Анализ надежности кс со сложной структурой

- •2.Расчет надежности кс

- •2. Для каждой вершины можно вычислить среднее количество попаданий вычислительного процесса в эту вершину по формуле

- •1. Разбить множество операторов на классы:

- •Модели вычислительных систем как систем массового обслуживания

- •1 Общие понятия и определения

- •Например m/m/1

- •2 Параметры систем массового обслуживания

- •Модели массового обслуживания вычислительных систем|

- •1. Представление вычислительной системы в виде стохастической сети

- •2. Потоки заявок

- •3. Длительность обслуживания заявок

- •Характеристики одноканальных смо

- •Многопроцессорные системы

- •5. Характеристики бесприоритетных дисциплин обслуживания

- •1) В порядке поступления (первой обслуживается заявка, поступившая раньше других);

- •2) В порядке, обратном порядку поступления заявок (первой обслуживается заявка, поступившая позже других);

- •3) Наугад, т. Е. Путем случайного выбора из очереди.

- •6. Характеристики дисциплины обслуживания с относительными приоритетами заявок

- •3.8. Характеристики дисциплин обслуживания со смешанными приоритетами

- •§ 3.9. Обслуживание заявок в групповом режиме

- •§ 3.10. Смешанный режим обслуживания заявок

- •§ 3.11. Диспетчирование на основе динамических приоритетов

- •§ 3.12. Оценка затрат на диспетчирование

- •1.Определяется интенсивность потока заявок I в смо Si из системы алгебраических уравнений

- •2.Вычисляются коэффициенты передач для каждой смо

- •3.Определяется среднее время обслуживания Ui заявки в смо Si :

- •6.Для моделирующей сети в целом характеристики п.5 определяются как

- •2.Расчет характеристик мультипроцессорной системы

- •1) Имеет доступ к общей памяти;

- •1.Средняя длина очереди заявок, ожидающих обслуживания в системе:

- •3. Среднее время пребывания заявок в системе :

- •Основные задачи теории кс

- •1. Задачи анализа;

- •2. Задачи синтеза;

- •3. Задачи идентификации.

- •1) С неограниченным временем пребывания заявок;

- •2) С относительными ограничениями на время пребывания заявок;

- •3) С абсолютными ограничениями на время пребывания заявок;

- •2.4. Контроллеры и сетевые комплексы ge Fanuc

- •Модели 311,313/323, 331

- •Коммуникационные возможности серии 90-30

- •2.4.3. Контроллеры VersaMax

- •2.4.4. Программное обеспечение

- •Общая характеристика протоколов и интерфейсов асу тп

- •2. Протоколы и интерфейсы нижнего уровня.

- •2. Основные технические характеристики контроллеров и программно-технических комплексов

- •Требования к корпоративной сети

- •2) Одновременное решение различных задач или частей одной задачи;

- •3) Конвейерная обработка информации.

- •1. Суть проблемы и основные понятия

- •1.1 Главные этапы распараллеливания задач

- •1.2 Сведения о вычислительных процессах

- •1.3 Распределенная обработка данных

- •1. Классификации архитектур параллельных вычислительных систем

- •1.1 Классификация Флинна

- •1. Процессоры

- •Память компьютерных систем

- •Простые коммутаторы

- •Простые коммутаторы с пространственным разделением

- •Составные коммутаторы

- •Коммутатор Клоза

- •Баньян-сети

- •Распределенные составные коммутаторы

- •Коммутация

- •Алгоритмы выбора маршрута

- •Граф межмодульных связей Convex Exemplar spp1000

- •Граф межмодульных связей мвс-100

- •3. Граф межмодульных связей мвс-1000

- •1. Построения коммуникационных сред на основе масштабируемого когерентного интерфейса sci

- •2. Коммуникационная среда myrinet

- •3. Коммуникационная среда Raceway

- •4. Коммуникационные среды на базе транспьютероподобных процессоров

- •1. Структура узла

- •2. Пакеты и свободные символы

- •3. Прием пакетов

- •4. Передача пакетов

- •5. Управление потоком

- •1. Структура адресного пространства

- •2. Регистры управления и состояния

- •3. Форматы пакетов

- •Когерентность кэш-памятей

- •1. Организация распределенной директории

- •2. Протокол когерентности

- •3. Алгоритм кэширования.

- •1 . Основные характеристики

- •1.2. Происхождение

- •1.3. Механизм когерентности

- •1. 4. Предназначение

- •1. 5. Структура коммуникационных сред на базе sci

- •1. 6. Физическая реализация

- •1. 7. Обозначение каналов

- •2. Реализация коммуникационной среды

- •2.1. На структурном уровне коммуникационная среда состоит из трех компонентов, как показано на рис. 2.1:

- •Масштабируемый когерентный интерфейс sci

- •Сетевая технология Myrinet

- •Коммуникационная среда Raceway

- •Коммуникационные среды на базе транспьютероподобных процессоров

- •1.Информационные модели

- •1.2. Мультипроцессоры

- •1.3. Мультикомпьютеры

- •Сравнительный анализ архитектур кс параллельного действия.

- •Архитектура вычислительных систем

- •Smp архитектура

- •Симметричные мультипроцессорные системы (smp)

- •Mpp архитектура

- •Массивно-параллельные системы (mpp)

- •Гибридная архитектура (numa)

- •Системы с неоднородным доступом к памяти (numa)

- •Pvp архитектура

- •Параллельные векторные системы (pvp)

- •1. Системы с конвейерной обработкой информации

- •1.2 Мультипроцессоры uma с много- ступенчатыми сетями

- •Мультипроцессоры numa

- •Мультипроцессор Sequent numa-q

- •Мультикомпьютеры с передачей сообщений

- •1. Общая характеристика кластерных систем.

- •2.Особенности построения кластерных систем.

- •Планирование работ в cow.

- •Без блокировки начала очереди (б); заполнение прямоугольника «процессоры-время» (в). Серым цветом показаны свободные процессоры

- •Общие сведения

- •Общие сведения

- •Логическая структура кластера

- •Логические функции физического узла.

- •Устройства памяти

- •Программное обеспечение

- •Элементы кластерных систем

- •1.1. Характеристики процессоров

- •Рассмотрим в начале процессор amd Opteron/Athlon 64.

- •Примеры промышленых разработок

- •Кластерные решения компании ibm

- •Диаграмма большого Linux-кластера.

- •Аппаратное обеспечение

- •Вычислительные узлы, выполняющие основные вычислительные задачи, для которых спроектирована система.

- •Программное обеспечение

- •Кластерные решения компании hp

- •Кластерные решения компании sgi

- •Производительность операций с плавающей точкой

- •Производительность памяти

- •Производительность системы ввода/вывода Linux

- •Масштабируемость технических приложений

- •Системное программное обеспечение

- •Архитектура san

- •Компоненты san

- •Примеры решений на основе san

- •San начального уровня

- •San между основным и резервным центром

- •Практические рекомендации

- •Построение san

- •Заключение

- •Принципы построения кластерных архитектур.

- •Оценки производительности параллельных систем

- •1) Имеет доступ к общей памяти;

- •2) Имеет общий доступ к устройствам ввода-вывода;

- •3) Управляется общей операционной системой, которая обеспечивает требуемое взаимодействие между процессорами и выполняемыми им программами как на аппаратном, так и на программном уровне.

- •4 Вероятность того, что в момент поступления очередной заявки все n процессоров заняты обслуживанием

- •Выбор коммутационного компонента.

- •Проблема сетевой перегрузки.

- •1. Обзор современных сетевых решении для построения кластеров.

- •1000-Мега битный вариант Ethernet

- •Организация внешней памяти

- •Эффективные кластерные решения

- •Концепция кластерных систем

- •Разделение на High Avalibility и High Performance системы

- •3. Проблематика High Performance кластеров

- •Проблематика High Availability кластерных систем

- •Смешанные архитектуры

- •6.Средства реализации High Performance кластеров

- •7.Средства распараллеливания

- •8.Средства реализации High Availability кластеров

- •9.Примеры проверенных решений

- •Архитектура san

- •Компоненты san

- •Примеры решений на основе san

- •San начального уровня

- •San между основным и резервным центром

- •Практические рекомендации

- •Построение san

- •Заключение

- •Symmetrix десять лет спустя

- •Матричная архитектура

- •Средства защиты данных

- •Ревизионизм и фон-неймановская архитектура

- •Литература

- •Связное программное обеспечение для мультикомпьютеров

- •1. Синхронная передача сообщений.

- •2. Буферная передача сообщений.

- •Планирование работ в cow

- •Средства распараллеливания

- •7.Средства распараллеливания

- •2. Кластерн ый вычислительн ый комплекс на основе интерфейса передачи сообщений

- •2.2 Программная реализация интерфейса передачи сообщений

- •2.3 Структура каталога mpich

- •2.4 «Устройства» mpich

- •2.5 Выполнение параллельной программы

- •2.6 Особенности выполнения программ на кластерах рабочих станций

- •2.7 Тестирование кластерного комплекса

- •Параллельная виртуальная машина

- •3 Кластерн ый вычислительн ый комплекс на основе пАраллельной виртуальной машины

- •3.1 Параллельная виртуальная машина

- •3.1.1 Общая характеристика

- •3.1.2 Гетерогенные вычислительные системы

- •3.1.3 Архитектура параллельной виртуальной машины

- •3.2 Настройка и запуск параллельной виртуальной машины

- •3.3 Структура каталога pvm

- •3.4 Тестирование параллельной виртуальной машины

- •На рисунке 3.2 представлена диаграмма, отображающая сравнение производительности коммуникационных библиотек mpi и pvm.

- •3.5 Сходства и различия pvm и mpi

- •4 . Кластерн ый вычислительн ый комплекса на основе программного пакета openMosix

- •4.1 Роль openMosix

- •4.2 Компоненты openMosix

- •4.2.1 Миграция процессов

- •4.2.2 Файловая система openMosix (oMfs)

- •4.3 Планирование кластера

- •4.4 Простая конфигурация

- •4.4.1 Синтаксис файла /etc/openmosix.Map

- •4.4.2 Автообнаружение

- •4. 5. Пользовательские утилиты администрирования openMosix

- •4. 6. Графические средства администрирования openMosix

- •4. 6.1 Использование openMosixView

- •4. 6.1.2 Окно конфигурации. Это окно появится после нажатия кнопки “cluster-node”.

- •4. 6.1.3 Окно advanced-execution. Если нужно запустить задания в кластере, то диалог "advanced execution" может сильно упростить эту задачу.

- •4.6.1.4 Командная строка. Можно указать дополнительные аргументы командной строки в поле ввода вверху окна. Аргументы приведены в таблице 9.2.

- •4. 6.2.2 Окно migrator. Этот диалог появляется, если кликнуть на каком-либо процессе из окна списка процессов.

- •4. 6.2.3 Управление удалёнными процессами. Этот диалог появляется при нажатии кнопки “manage procs from remote”

- •4.5.3 Использование openMosixcollector

- •4. 6.4 Использование openMosixanalyzer

- •4. 6.4. 1 Окно load-overview. Здесь отображается хронология нагрузки openMosix.

- •4. 6.4. 2 Статистическая информация об узле

- •4.5.4.3 Окно memory-overview. Здесь представляется обзор использования памяти (Memory-overview) в openMosixanalyzer.

- •4. 6.4.4 Окно openMosixhistory

- •4. 6.5 Использование openMosixmigmon

- •4.6 Список условных сокращений

- •Перечень ссылок

- •Общие сведения

- •2. Создание Windows-кластера

- •Суперкомпьютерная Программа "скиф"

- •Описание технических решений

- •Направления работ

- •Основные результаты

- •Кластер мгиу

- •Содержание

- •Понятие о кластере

- •Аппаратное обеспечение

- •Пропускная способность и латентность

- •1. Определение распределенной системы

- •2.1. Соединение пользователей с ресурсами

- •2.2. Прозрачность

- •Прозрачность в распределенных системах

- •2.3. Открытость

- •2.4. Масштабируемость

- •3.1. Мультипроцессоры

- •3.2. Гомогенные мультикомпьютерные системы

- •3.3. Гетерогенные мультикомпьютерные системы

- •4. Концепции программных решений рс

- •4.1. Распределенные операционные системы

- •4.2. Сетевые операционные системы

- •4.3. Программное обеспечение промежуточного уровня

- •5. Модель клиент-сервер рс

- •5.1. Клиенты и серверы

- •5.2. Разделение приложений по уровням

- •5.3. Варианты архитектуры клиент-сервер

- •Формы метакомпьютера

- •Настольный суперкомпьютер.

- •2. Интеллектуальный инструментальный комплекс.

- •Сетевой суперкомпьютер.

- •Проблемы создания метакомпьютера

- •Сегодняшняя архитектура метакомпьютерной среды

- •Взаимосвязь метакомпьютинга с общими проблемами развития системного по

- •5. Модель клиент-сервер рс

- •5.1. Клиенты и серверы

- •5.2. Разделение приложений по уровням

- •5.3. Варианты архитектуры клиент-сервер

- •Symmetrix десять лет спустя

- •Матричная архитектура

- •Средства защиты данных

- •Ревизионизм и фон-неймановская архитектура

- •Однородные вычислительные среды

- •Однокристальный ассоциативный процессор сам2000

- •Модели нейронных сетей

- •Модели инс

- •Оптимизационные системы.

- •Неуправляемые системы распознавания образов.

- •Системы feed forward.

- •Элементы нейрологики с позиции аппаратной реализации

- •Реализация нейронных сетей

- •Программные нейрокомпьютеры

- •Программно-аппаратные нейрокомпьютеры

- •Практическое использование инс

Коммутация

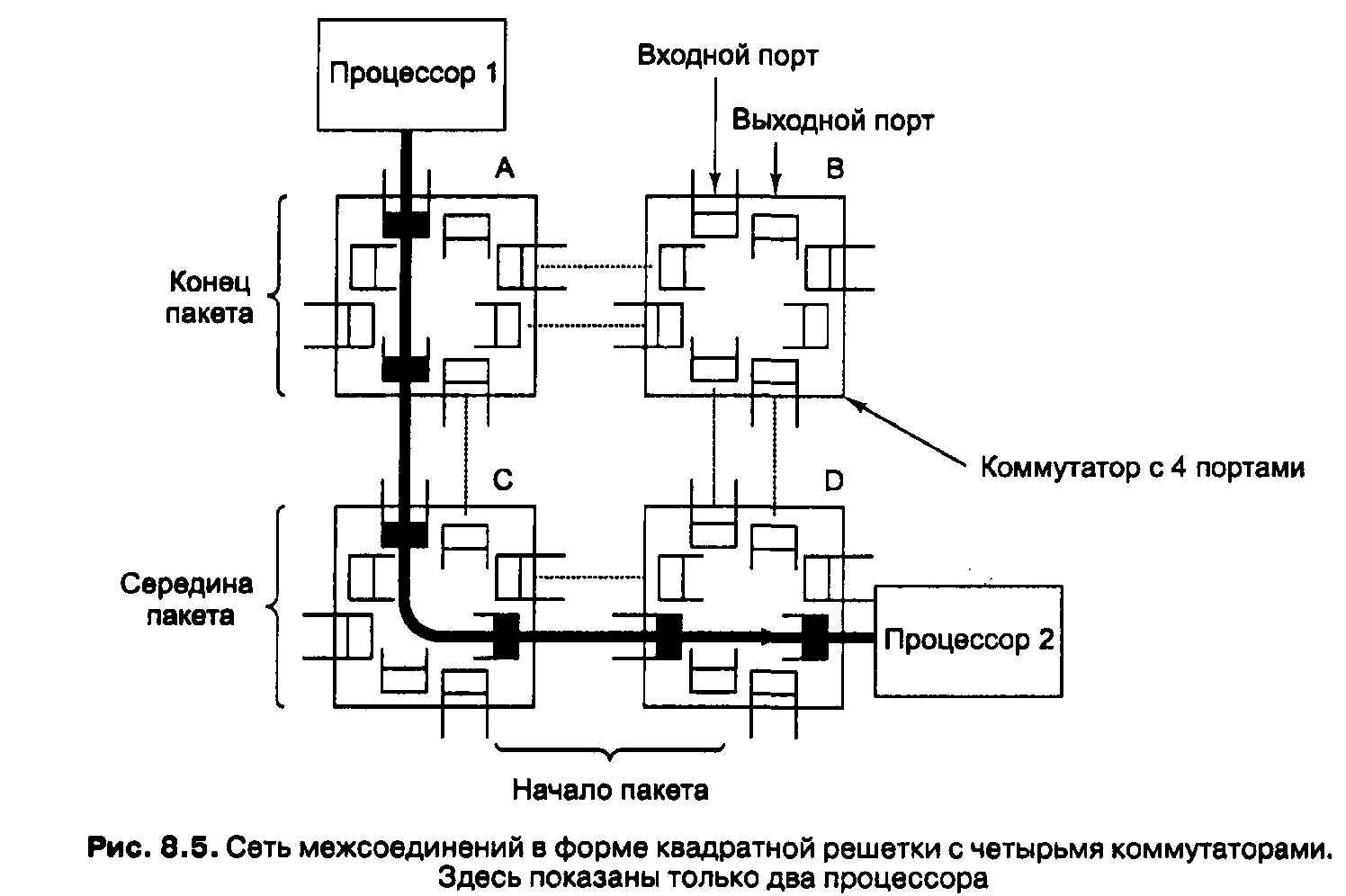

Сеть межсоединений состоит из коммутаторов и проводов, соединяющих их. На рисунке 8.5 изображена небольшая сеть межсоединений с четырьмя коммутаторами. В данном случае каждый коммутатор имеет 4 входных порта и 4 выходных порта. Кроме того, каждый коммутатор содержит несколько центральных процессоров и схемы соединения (на рисунке они показано не полностью). Задача коммутатора — принимать пакеты, которые приходят на любой входной порт, и отправлять пакеты из соответствующих выходных портов.

Каждый выходной порт связан с входным портом другого коммутатора через последовательный или параллельный канал (на рис. 8.5. это пунктирная линия). Последовательные каналы передают один бит единовременно. Параллельные каналы могут передавать несколько битов сразу. Существуют специальные сигналы для управления каналом. Параллельные каналы характеризуются более высокой производительностью, чем последовательные каналы с такой же тактовой часто-

той, но в них возникает проблема расфазировки данных (нужно быть уверенным, что все биты прибывают одновременно), и они стоят гораздо дороже.

Существует несколько стратегий переключения.

Первая из них — коммутация каналов. Перед тем как послать пакет, весь путь от начального до конечного пункта резервируется заранее. Все порты и буферы затребованы заранее, поэтому когда начинается процесс передачи, все необходимые ресурсы гарантированно доступны, и биты могут на полной скорости перемещаться от исходного пункта через все коммутаторы к пункту назначения. На рис. 8.5 показана коммутация каналов, где резервируются канал от процессора 1 к процессору 2 (черная жирная стрелка). Здесь резервируются три входных и три выходных порта.

Коммутацию каналов можно сравнить с перекрытием движения транспорта во время парада, когда блокируются все прилегающие улицы. При этом требуется предварительное планирование, но после блокирования прилегающих улиц парад может продвигаться на полной скорости, поскольку никакой транспорт препятствовать этому не будет. Недостаток такого метода состоит в том, что требуется предварительное планирование и любое движение транспорта запрещено, даже если парад (или пакеты) еще не приближается.

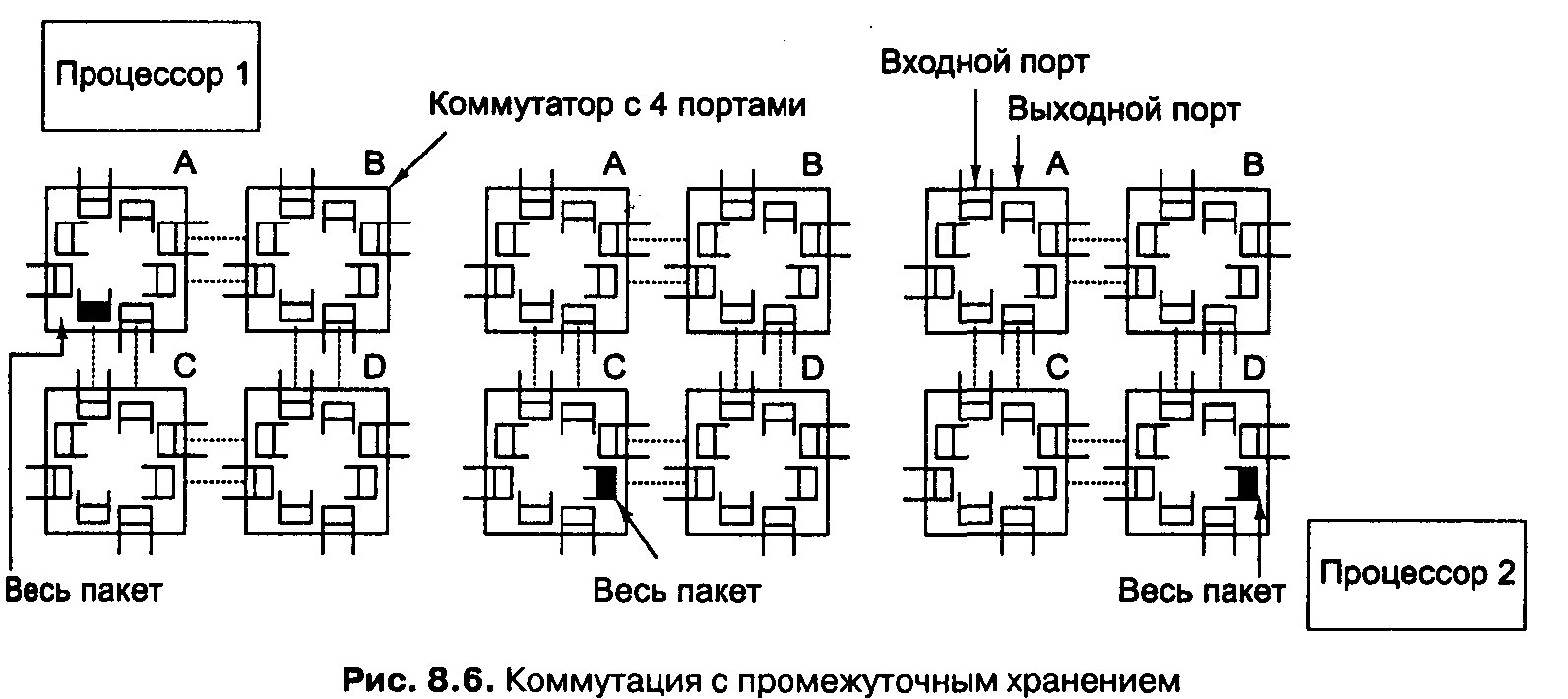

Вторая стратегия — коммутация с промежуточным хранением. Здесь не требуется предварительного резервирования. Из исходного пункта посылается целый пакет к первому коммутатору, где он хранится целиком. На рис. 8.6, а исходным пунктом является процессор 1, а весь пакет, который направляется в процессор 2, сначала сохраняется внутри коммутатора А. Затем этот пакет перемещается в коммутатор С, как показано на рис. 8.6, б. Затем весь пакет целиком перемещается в коммутатор D (рис. 8.6, в). Наконец, пакет доходит до пункта назначения — до процессора 2. Отметим, что никакого предварительного резервирования ресурсов не требуется.

Коммутаторы с промежуточным хранением должны отправлять пакеты в буфер, поскольку когда исходный пункт (например, процессор, память или коммутатор) выдает пакет, требующийся выходной порт может быть в данный момент занят передачей другого пакета. Если бы не было буферизации, входящие пакеты, которым нужен занятый в данный момент выходной порт, пропадали бы. Применяется три метода буферизации. При буферизации на входе один или несколько буферов связываются с каждым входным портом в форме очереди типа FIFO («первым вошел, первым вышел»). Если пакет в начале очереди нельзя передать по причине занятости нужного выходного порта, этот пакет просто ждет своей очереди.

Однако если пакет ожидает, когда освободится выходной порт, то пакет, идущий за-ним, тоже не может передаваться, даже если нужный ему порт свободен. Ситуация называется блокировкой начала очереди. Проиллюстрируем ситуацию на примере. Представим дорогу из двух рядов. Вереница машин в одном из рядов не может двигаться дальше, поскольку первая машина в этом ряду хочет повернуть налево, но не может из-за движения машин другого ряда. Даже если второй и всем следующим за ней машинам нужно ехать прямо, первая машина в ряду препятствует их движению.

Проблему можно устранить с помощью буферизации на выходе.

В этой системе буферы связаны с выходными портами. Биты пакета по мере пребывания сохраняются в буфере, который связан с нужным выходным портом. Поэтому пакеты, направленные в порт т, не могут блокировать пакеты, направленные в порт п. И при буферизации на входе, и при буферизации на выходе с каждым портом связано определенное количество буферов. Если места недостаточно для хранения всех пакетов, то какие-то пакеты придется выбрасывать. Чтобы разрешить эту проблему, можно использовать общую буферизацию, при которой один буферный пул динамически распределяется по портам по мере необходимости. Однако такая схема требует более сложного управления, чтобы следить за буферами, и позволяет одному занятому соединению захватить все буферы, оставив другие соединения ни с чем. Кроме того, каждый коммутатор должен вмещать самый большой пакет и даже несколько пакетов максимального размера, а для этого потребуется ужесточить требования к памяти и снизить максимальный размер пакета.

Хотя метод коммутации с промежуточным хранением гибок и эффективен, здесь возникает проблема возрастающей задержки при передаче данных по сети межсоединений. Предположим, что время, необходимое для перемещения пакета по одному транзитному участку на рис. 8.6, занимает Т не. Чтобы переместить пакет из процессора 1 в процессор 2, нужно скопировать его 4 раза (в А, в С, в D и в процессор 2), и следующее копирование не может начаться, пока не закончится предыдущее, поэтому задержка по сети составляет 4Т. Чтобы выйти из этой ситуации, нужно разработать гибридную сеть межсоединений, объединяющую в себе коммутацию каналов и коммутацию пакетов. Например, каждый пакет можно разделить на части. Как только первая часть поступила в коммутатор, ее можно сразу направить в следующий коммутатор, даже если оставшиеся части пакета еще не прибыли в этот коммутатор.

Такой подход отличается от коммутации каналов тем, что ресурсы не резервируются заранее. Следовательно, возможна конфликтная ситуация в соревновании за право обладания ресурсами (портами и буферами). При коммутации без буферизации пакетов, если первый блок пакета не может двигаться дальше, оставшаяся часть пакета продолжает поступать в коммутатор. В худшем случае эта схема превратится в коммутацию с промежуточным хранением. При другом типе маршрутизации, так называемой «wonnhole routing» (червоточина), если первый блок не может двигаться дальше, в исходный пункт передается сигнал остановить передачу, и пакет может оборваться, будучи растянутым на два и более коммутаторов. Когда необходимые ресурсы становятся доступными, пакет может двигаться дальше.

Следует отметить, что оба подхода аналогичны конвейерному выполнению команд в центральном процессоре. В любой момент времени каждый коммутатор выполняет небольшую часть работы, и в результате получается более высокая производительность, чем если бы эту же работу выполнял один из коммутаторов.