- •1 Задачи анализа;

- •2 Задачи синтеза;

- •3 Задачи идентификации.

- •Основные задачи теории кс

- •1. Задачи анализа;

- •2. Задачи синтеза;

- •3. Задачи идентификации.

- •2. Высокой интенсивностью взаимодействия и вытекающим отсюда требованием уменьшения времени ответа.

- •Функционирование кс

- •Основные задачи теории вычислительных систем

- •Общая характеристика методов теории вычислительных систем

- •3. Классификация вычислительных систем

- •Характеристики производительности и надежности кс

- •Характеристики надежности кс

- •1 Холодное резервирование. Работает только основной канал.

- •2 Нагруженный резерв. Включены оба канала (резервный канал занимается посторонними задачами). Время перехода на основную задачу меньше чем в холодном резерве.

- •Общая характеристика методов теории вычислительных систем

- •Характеристики производительности кс

- •1. Номинальная производительность ;

- •2. Комплексная производительность ;

- •3. Пакеты тестовых программ spec XX

- •Характеристики надежности кс

- •1 Холодное резервирование. Работает только основной канал.

- •2 Нагруженный резерв. Включены оба канала (резервный канал занимается посторонними задачами). Время перехода на основную задачу меньше чем в холодном резерве.

- •4) Указывается начальное состояние системы;

- •8) Находятся показатели качества вс на основе найденных вероятностей состояния системы.

- •Анализ надежности кс со сложной структурой

- •2.Расчет надежности кс

- •2. Для каждой вершины можно вычислить среднее количество попаданий вычислительного процесса в эту вершину по формуле

- •1. Разбить множество операторов на классы:

- •Модели вычислительных систем как систем массового обслуживания

- •1 Общие понятия и определения

- •Например m/m/1

- •2 Параметры систем массового обслуживания

- •Модели массового обслуживания вычислительных систем|

- •1. Представление вычислительной системы в виде стохастической сети

- •2. Потоки заявок

- •3. Длительность обслуживания заявок

- •Характеристики одноканальных смо

- •Многопроцессорные системы

- •5. Характеристики бесприоритетных дисциплин обслуживания

- •1) В порядке поступления (первой обслуживается заявка, поступившая раньше других);

- •2) В порядке, обратном порядку поступления заявок (первой обслуживается заявка, поступившая позже других);

- •3) Наугад, т. Е. Путем случайного выбора из очереди.

- •6. Характеристики дисциплины обслуживания с относительными приоритетами заявок

- •3.8. Характеристики дисциплин обслуживания со смешанными приоритетами

- •§ 3.9. Обслуживание заявок в групповом режиме

- •§ 3.10. Смешанный режим обслуживания заявок

- •§ 3.11. Диспетчирование на основе динамических приоритетов

- •§ 3.12. Оценка затрат на диспетчирование

- •1.Определяется интенсивность потока заявок I в смо Si из системы алгебраических уравнений

- •2.Вычисляются коэффициенты передач для каждой смо

- •3.Определяется среднее время обслуживания Ui заявки в смо Si :

- •6.Для моделирующей сети в целом характеристики п.5 определяются как

- •2.Расчет характеристик мультипроцессорной системы

- •1) Имеет доступ к общей памяти;

- •1.Средняя длина очереди заявок, ожидающих обслуживания в системе:

- •3. Среднее время пребывания заявок в системе :

- •Основные задачи теории кс

- •1. Задачи анализа;

- •2. Задачи синтеза;

- •3. Задачи идентификации.

- •1) С неограниченным временем пребывания заявок;

- •2) С относительными ограничениями на время пребывания заявок;

- •3) С абсолютными ограничениями на время пребывания заявок;

- •2.4. Контроллеры и сетевые комплексы ge Fanuc

- •Модели 311,313/323, 331

- •Коммуникационные возможности серии 90-30

- •2.4.3. Контроллеры VersaMax

- •2.4.4. Программное обеспечение

- •Общая характеристика протоколов и интерфейсов асу тп

- •2. Протоколы и интерфейсы нижнего уровня.

- •2. Основные технические характеристики контроллеров и программно-технических комплексов

- •Требования к корпоративной сети

- •2) Одновременное решение различных задач или частей одной задачи;

- •3) Конвейерная обработка информации.

- •1. Суть проблемы и основные понятия

- •1.1 Главные этапы распараллеливания задач

- •1.2 Сведения о вычислительных процессах

- •1.3 Распределенная обработка данных

- •1. Классификации архитектур параллельных вычислительных систем

- •1.1 Классификация Флинна

- •1. Процессоры

- •Память компьютерных систем

- •Простые коммутаторы

- •Простые коммутаторы с пространственным разделением

- •Составные коммутаторы

- •Коммутатор Клоза

- •Баньян-сети

- •Распределенные составные коммутаторы

- •Коммутация

- •Алгоритмы выбора маршрута

- •Граф межмодульных связей Convex Exemplar spp1000

- •Граф межмодульных связей мвс-100

- •3. Граф межмодульных связей мвс-1000

- •1. Построения коммуникационных сред на основе масштабируемого когерентного интерфейса sci

- •2. Коммуникационная среда myrinet

- •3. Коммуникационная среда Raceway

- •4. Коммуникационные среды на базе транспьютероподобных процессоров

- •1. Структура узла

- •2. Пакеты и свободные символы

- •3. Прием пакетов

- •4. Передача пакетов

- •5. Управление потоком

- •1. Структура адресного пространства

- •2. Регистры управления и состояния

- •3. Форматы пакетов

- •Когерентность кэш-памятей

- •1. Организация распределенной директории

- •2. Протокол когерентности

- •3. Алгоритм кэширования.

- •1 . Основные характеристики

- •1.2. Происхождение

- •1.3. Механизм когерентности

- •1. 4. Предназначение

- •1. 5. Структура коммуникационных сред на базе sci

- •1. 6. Физическая реализация

- •1. 7. Обозначение каналов

- •2. Реализация коммуникационной среды

- •2.1. На структурном уровне коммуникационная среда состоит из трех компонентов, как показано на рис. 2.1:

- •Масштабируемый когерентный интерфейс sci

- •Сетевая технология Myrinet

- •Коммуникационная среда Raceway

- •Коммуникационные среды на базе транспьютероподобных процессоров

- •1.Информационные модели

- •1.2. Мультипроцессоры

- •1.3. Мультикомпьютеры

- •Сравнительный анализ архитектур кс параллельного действия.

- •Архитектура вычислительных систем

- •Smp архитектура

- •Симметричные мультипроцессорные системы (smp)

- •Mpp архитектура

- •Массивно-параллельные системы (mpp)

- •Гибридная архитектура (numa)

- •Системы с неоднородным доступом к памяти (numa)

- •Pvp архитектура

- •Параллельные векторные системы (pvp)

- •1. Системы с конвейерной обработкой информации

- •1.2 Мультипроцессоры uma с много- ступенчатыми сетями

- •Мультипроцессоры numa

- •Мультипроцессор Sequent numa-q

- •Мультикомпьютеры с передачей сообщений

- •1. Общая характеристика кластерных систем.

- •2.Особенности построения кластерных систем.

- •Планирование работ в cow.

- •Без блокировки начала очереди (б); заполнение прямоугольника «процессоры-время» (в). Серым цветом показаны свободные процессоры

- •Общие сведения

- •Общие сведения

- •Логическая структура кластера

- •Логические функции физического узла.

- •Устройства памяти

- •Программное обеспечение

- •Элементы кластерных систем

- •1.1. Характеристики процессоров

- •Рассмотрим в начале процессор amd Opteron/Athlon 64.

- •Примеры промышленых разработок

- •Кластерные решения компании ibm

- •Диаграмма большого Linux-кластера.

- •Аппаратное обеспечение

- •Вычислительные узлы, выполняющие основные вычислительные задачи, для которых спроектирована система.

- •Программное обеспечение

- •Кластерные решения компании hp

- •Кластерные решения компании sgi

- •Производительность операций с плавающей точкой

- •Производительность памяти

- •Производительность системы ввода/вывода Linux

- •Масштабируемость технических приложений

- •Системное программное обеспечение

- •Архитектура san

- •Компоненты san

- •Примеры решений на основе san

- •San начального уровня

- •San между основным и резервным центром

- •Практические рекомендации

- •Построение san

- •Заключение

- •Принципы построения кластерных архитектур.

- •Оценки производительности параллельных систем

- •1) Имеет доступ к общей памяти;

- •2) Имеет общий доступ к устройствам ввода-вывода;

- •3) Управляется общей операционной системой, которая обеспечивает требуемое взаимодействие между процессорами и выполняемыми им программами как на аппаратном, так и на программном уровне.

- •4 Вероятность того, что в момент поступления очередной заявки все n процессоров заняты обслуживанием

- •Выбор коммутационного компонента.

- •Проблема сетевой перегрузки.

- •1. Обзор современных сетевых решении для построения кластеров.

- •1000-Мега битный вариант Ethernet

- •Организация внешней памяти

- •Эффективные кластерные решения

- •Концепция кластерных систем

- •Разделение на High Avalibility и High Performance системы

- •3. Проблематика High Performance кластеров

- •Проблематика High Availability кластерных систем

- •Смешанные архитектуры

- •6.Средства реализации High Performance кластеров

- •7.Средства распараллеливания

- •8.Средства реализации High Availability кластеров

- •9.Примеры проверенных решений

- •Архитектура san

- •Компоненты san

- •Примеры решений на основе san

- •San начального уровня

- •San между основным и резервным центром

- •Практические рекомендации

- •Построение san

- •Заключение

- •Symmetrix десять лет спустя

- •Матричная архитектура

- •Средства защиты данных

- •Ревизионизм и фон-неймановская архитектура

- •Литература

- •Связное программное обеспечение для мультикомпьютеров

- •1. Синхронная передача сообщений.

- •2. Буферная передача сообщений.

- •Планирование работ в cow

- •Средства распараллеливания

- •7.Средства распараллеливания

- •2. Кластерн ый вычислительн ый комплекс на основе интерфейса передачи сообщений

- •2.2 Программная реализация интерфейса передачи сообщений

- •2.3 Структура каталога mpich

- •2.4 «Устройства» mpich

- •2.5 Выполнение параллельной программы

- •2.6 Особенности выполнения программ на кластерах рабочих станций

- •2.7 Тестирование кластерного комплекса

- •Параллельная виртуальная машина

- •3 Кластерн ый вычислительн ый комплекс на основе пАраллельной виртуальной машины

- •3.1 Параллельная виртуальная машина

- •3.1.1 Общая характеристика

- •3.1.2 Гетерогенные вычислительные системы

- •3.1.3 Архитектура параллельной виртуальной машины

- •3.2 Настройка и запуск параллельной виртуальной машины

- •3.3 Структура каталога pvm

- •3.4 Тестирование параллельной виртуальной машины

- •На рисунке 3.2 представлена диаграмма, отображающая сравнение производительности коммуникационных библиотек mpi и pvm.

- •3.5 Сходства и различия pvm и mpi

- •4 . Кластерн ый вычислительн ый комплекса на основе программного пакета openMosix

- •4.1 Роль openMosix

- •4.2 Компоненты openMosix

- •4.2.1 Миграция процессов

- •4.2.2 Файловая система openMosix (oMfs)

- •4.3 Планирование кластера

- •4.4 Простая конфигурация

- •4.4.1 Синтаксис файла /etc/openmosix.Map

- •4.4.2 Автообнаружение

- •4. 5. Пользовательские утилиты администрирования openMosix

- •4. 6. Графические средства администрирования openMosix

- •4. 6.1 Использование openMosixView

- •4. 6.1.2 Окно конфигурации. Это окно появится после нажатия кнопки “cluster-node”.

- •4. 6.1.3 Окно advanced-execution. Если нужно запустить задания в кластере, то диалог "advanced execution" может сильно упростить эту задачу.

- •4.6.1.4 Командная строка. Можно указать дополнительные аргументы командной строки в поле ввода вверху окна. Аргументы приведены в таблице 9.2.

- •4. 6.2.2 Окно migrator. Этот диалог появляется, если кликнуть на каком-либо процессе из окна списка процессов.

- •4. 6.2.3 Управление удалёнными процессами. Этот диалог появляется при нажатии кнопки “manage procs from remote”

- •4.5.3 Использование openMosixcollector

- •4. 6.4 Использование openMosixanalyzer

- •4. 6.4. 1 Окно load-overview. Здесь отображается хронология нагрузки openMosix.

- •4. 6.4. 2 Статистическая информация об узле

- •4.5.4.3 Окно memory-overview. Здесь представляется обзор использования памяти (Memory-overview) в openMosixanalyzer.

- •4. 6.4.4 Окно openMosixhistory

- •4. 6.5 Использование openMosixmigmon

- •4.6 Список условных сокращений

- •Перечень ссылок

- •Общие сведения

- •2. Создание Windows-кластера

- •Суперкомпьютерная Программа "скиф"

- •Описание технических решений

- •Направления работ

- •Основные результаты

- •Кластер мгиу

- •Содержание

- •Понятие о кластере

- •Аппаратное обеспечение

- •Пропускная способность и латентность

- •1. Определение распределенной системы

- •2.1. Соединение пользователей с ресурсами

- •2.2. Прозрачность

- •Прозрачность в распределенных системах

- •2.3. Открытость

- •2.4. Масштабируемость

- •3.1. Мультипроцессоры

- •3.2. Гомогенные мультикомпьютерные системы

- •3.3. Гетерогенные мультикомпьютерные системы

- •4. Концепции программных решений рс

- •4.1. Распределенные операционные системы

- •4.2. Сетевые операционные системы

- •4.3. Программное обеспечение промежуточного уровня

- •5. Модель клиент-сервер рс

- •5.1. Клиенты и серверы

- •5.2. Разделение приложений по уровням

- •5.3. Варианты архитектуры клиент-сервер

- •Формы метакомпьютера

- •Настольный суперкомпьютер.

- •2. Интеллектуальный инструментальный комплекс.

- •Сетевой суперкомпьютер.

- •Проблемы создания метакомпьютера

- •Сегодняшняя архитектура метакомпьютерной среды

- •Взаимосвязь метакомпьютинга с общими проблемами развития системного по

- •5. Модель клиент-сервер рс

- •5.1. Клиенты и серверы

- •5.2. Разделение приложений по уровням

- •5.3. Варианты архитектуры клиент-сервер

- •Symmetrix десять лет спустя

- •Матричная архитектура

- •Средства защиты данных

- •Ревизионизм и фон-неймановская архитектура

- •Однородные вычислительные среды

- •Однокристальный ассоциативный процессор сам2000

- •Модели нейронных сетей

- •Модели инс

- •Оптимизационные системы.

- •Неуправляемые системы распознавания образов.

- •Системы feed forward.

- •Элементы нейрологики с позиции аппаратной реализации

- •Реализация нейронных сетей

- •Программные нейрокомпьютеры

- •Программно-аппаратные нейрокомпьютеры

- •Практическое использование инс

Память компьютерных систем

В современных КС используются следующие разновидности памяти.

Оперативная память

Разделяемая память

Чередуемая память

Оперативная память

Характеристики оперативной памяти и особенности ее устройства являются важнейшим фактором, от которого зависит быстродействие компьютера. Ведь даже при наличии быстрого процессора скорость выборки данных из памяти может оказаться невысокой, и именно эта невысокая скорость работы с оперативной памятью будет определять быстродействие компьютера.

Время

цикла работы с памятью

обычно

заметно больше, чем время цикла

центрального процессора

обычно

заметно больше, чем время цикла

центрального процессора

.

.

Если процессор

инициализирует обращение к памяти, она

будет занята в течение времени

и в

течение этого промежутка времени ни

одно другое устройство, в том числе и

сам процессор, не смогут работать с

оперативной памятью.

и в

течение этого промежутка времени ни

одно другое устройство, в том числе и

сам процессор, не смогут работать с

оперативной памятью.

Таким образом, возникает проблема доступа к памяти.

Эта проблема решается специальной организацией оперативной памяти. Принята следующая классификация параллельных компьютеров по архитектуре подсистем оперативной памяти:

- системы с разделяемой памятью, у которых есть одна большая виртуальная память, и все процессоры имеют одинаковый доступ к данным и командам, хранящимся в этой памяти;

- системы с распределенной памятью, у которых каждый процессор имеет свою локальную оперативную память, и к этой памяти у других процессоров нет доступа.

Различие между разделяемой и распределенной памятью заключается в способе интерпретации адреса. Это различие можно пояснить на следующем примере. Пусть один из процессоров выполняет команду load r1, i (загрузить в регистр r1 данные из ячейки памяти i).

Если команда выполняется на компьютере с разделяемой памятью, номер ячейки i имеет одинаковый смысл для всех процессоров, т. е. i является глобальным адресом.

В системе с распределенной памятью ячейка i разная для различных процессоров и в регистры r1 по этой команде будут загружены разные значения.

Разделяемая память

Простейший способ создать многопроцессорный вычислительный комплекс с разделяемой памятью - взять несколько процессоров, соединить их общей шиной между собой и с оперативной памятью. Это - простой, но не самый лучший способ, поскольку, если один процессор принимает команду или передает данные, все остальные процессоры вынуждены переходить в режим ожидания.

Это приводит к тому, что, начиная с некоторого числа процессоров, быстродействие такой системы перестает увеличиваться при добавлении нового процессора.

В многопроцессорных вычислительных системах возникает проблема кэш-когерентности. Она заключается в том, что если двум или более процессорам понадобилось значение одной и той же переменной, оно будет храниться в виде нескольких копий в кэш-памяти всех процессоров. Один из процессоров может изменить это значение в результате выполнения своей команды и оно будет передано в оперативную память компьютера. Но в кэш-памяти остальных процессоров все еще хранится старое значение. Следовательно, необходимо обеспечить своевременное обновление данных в кэш-памяти всех процессоров компьютера.

Проблема кэш-когерентности может решаться программным путем - на уровне транслятора и операционной системы. Транслятор, например, может определять моменты безопасной синхронизации кэш-памяти при выполнении программы.

Другой подход основан на аппаратном решении проблемы кэш-когерентности. В этом случае применяются специальные протоколы, кэш-память используется более эффективно, все происходит "прозрачно" для программиста.

Протоколы каталогов реализуют сбор и учет информации о копиях данных в кэш-памяти. Эта информация хранится в специальной области оперативной памяти - каталоге.

Запросы проверяются с помощью каталога, затем выполняются необходимые пересылки данных. Использование данного подхода эффективно в больших системах со сложными схемами коммуникации.

Протоколы слежения распределяют "ответственность" за когерентность кэшей между контроллерами кэш-памяти. Контроллер определяет изменение содержания кэш-памяти и передает информацию об этом другим модулям кэш-памяти. Очевидно, в этом случае возрастает объем передаваемых данных. В некоторых системах используется адаптивная смесь обоих подходов.

Имеются различные реализации разделяемой памяти. Это, например, разделяемая память с дискретными модулями памяти.

Физическая память состоит из нескольких модулей, хотя виртуальное адресное пространство остается общим. Вместо общей шины в этом случае используется коммутатор, направляющий запросы от процессора к памяти. Такой коммутатор может одновременно обрабатывать несколько запросов к памяти, поэтому, если все процессоры обращаются к разным модулям памяти, быстродействие возрастает.

Чередуемая память

Чередуемая память разделяется на банки памяти. Принято соглашение о том, что ячейка памяти с номером i находится в банке памяти с номером i mod n, где n - количество банков памяти, a mod - операция вычисления остатка от деления. Таким образом, если имеется 8 банков памяти, то первому банку памяти будут принадлежать ячейки памяти с номерами 0, 8, 16, ..., второму - 1, 9, 17, ... и т. д. Запросы к различным банкам памяти могут обрабатываться одновременно. При достаточном количестве банков памяти скорость обмена данными между памятью и процессором может быть близка к идеальному значению - одно машинное слово за один такт работы процессора.

Ячейки памяти могут быть перенумерованы и непрерывным образом, т. е., скажем, в первом банке находятся ячейки с номерами от 0 до 255, во втором от 256 до 511 и т. д.

В векторных компьютерах обычно используется первый способ адресации, а в многопроцессорных комплексах с разделяемой памятью - второй.

Сети межсоединений в параллельных КС и их характеристики

Мультикомпьютеры связываются через сети межсоединений. Интересно отметить, что мультикомпьютеры и мультипроцессоры очень сходны в этом отношении, поскольку мультипроцессоры часто содержат несколько модулей памяти, которые также должны быть связаны друг с другом и с процессорами. Следовательно, многое из того, о чем мы будем говорить в этом разделе, применимо к обоим типам систем.

Основная причина сходства коммуникационных связей в мультипроцессоре и мультикомпьютере заключается в том, что в обоих случаях применяется передача сообщений. Даже в однопроцессорной машине, когда процессору нужно считать или записать слово, он устанавливает определенные линии на шине и ждет ответа.

Это действие представляет собой то же самое, что и передача сообщений: инициатор посылает запрос и ждет ответа.

В больших мультипроцессорах взаимодействие между процессорами и удаленной памятью почти всегда состоит в том, что процессор посылает в память сообщение, так называемый пакет, который запрашивает определенные данные, а память посылает процессору ответный пакет.

Сети межсоединений могут состоять максимум из пяти компонентов:

1. Центральные процессоры.

2. Модули памяти.

3. Интерфейсы.

4. Каналы связи.

5. Коммутаторы.

Процессоры и модули памяти мы уже рассматривали больше не будем к этому возвращаться.

Интерфейсы — это устройства, которые вводят и выводят сообщения из центральных процессоров и модулей памяти. Во многих разработках интерфейс представляет собой микросхему или плату, к которой подсоединяется локальная шина каждого процессора и которая может передавать сигналы процессору и локальной памяти (если таковая есть).

Часто внутри интерфейса содержится программируемый процессор со своим собственным ПЗУ, которое принадлежит только этому процессору. Обычно интерфейс способен считывать и записывать информацию в различные модули памяти, что позволяет ему перемещать блоки данных.

Каналы связи — это каналы, по которым перемещаются биты. Каналы могут быть электрическими или оптико-волоконными, последовательными (шириной 1 бит) или параллельными (шириной более 1 бита). Каждый канал связи характеризуется максимальной пропускной способностью (это максимальное число битов, которое он способен передавать в секунду). Каналы могут быть симплексными (передавать биты только в одном направлении), полудуплексными (передавать информацию в обоих направлениях, но не одновременно) и дуплексными (передавать биты в обоих направлениях одновременно).

Коммутаторы — это устройства с несколькими входными и несколькими выходными может быть с односторонним и двусторонним движением, она характеризуется определенной «скоростью передачи данных» (имеется в виду ограничение скорости движения) и имеет определенную ширину (число рядов). Перекрестки похожи на порты. Когда на входной порт приходит пакет, некоторые биты в этом пакете используются для выбора выходного порта, в который посылается пакет.

Размер пакета может составлять 2 или 4 байта, но может быть и значительно больше (например, 8 Кбайт).

Еще одно важное свойство сети межсоединений — это ее пропускная способность, то есть количество данных, которое она способна передавать в секунду.

Очень важная характеристика — бисекционная пропускная способность. Чтобы вычислить это число, нужно мысленно разделить сеть межсоединений на две равные (с точки зрения числа узлов) несвязанные части путем удаления ряда дуг из графа. Затем нужно вычислить общую пропускную способность дуг, которые мы удалили.

Существует множество способов разделения сети межсоединений на две равные части. Бисекционная пропускная способность — минимальная из всех возможных. Предположим, что бисекционная пропускная способность составляет 800 бит/с. Тогда если между двумя частями много взаимодействий, то общую пропускную способность в худшем случае можно сократить до 800 бит/с.

По мнению многих разработчиков, бисекционная пропускная способность — это самая важная характеристика сети межсоединений. Часто основная цель при разработке сета межсоединений — сделать бисекционную пропускную способность максимальной

Сети межсоединений можно характеризовать по их размерности.

Размерность определяется по числу возможных вариантов перехода из исходного пункта в пункт назначения.

Если выбора нет (то есть существует только один путь из каждого исходного пункта в каждый конечный пункт), то сеть нульмерная.

Если есть два возможных варианта (например, если можно пойти либо направо, либо налево),то сеть одномерна. Если есть две оси и пакет может направиться направо или налево либо вверх или вниз, то такая сеть двумерна и т. д.

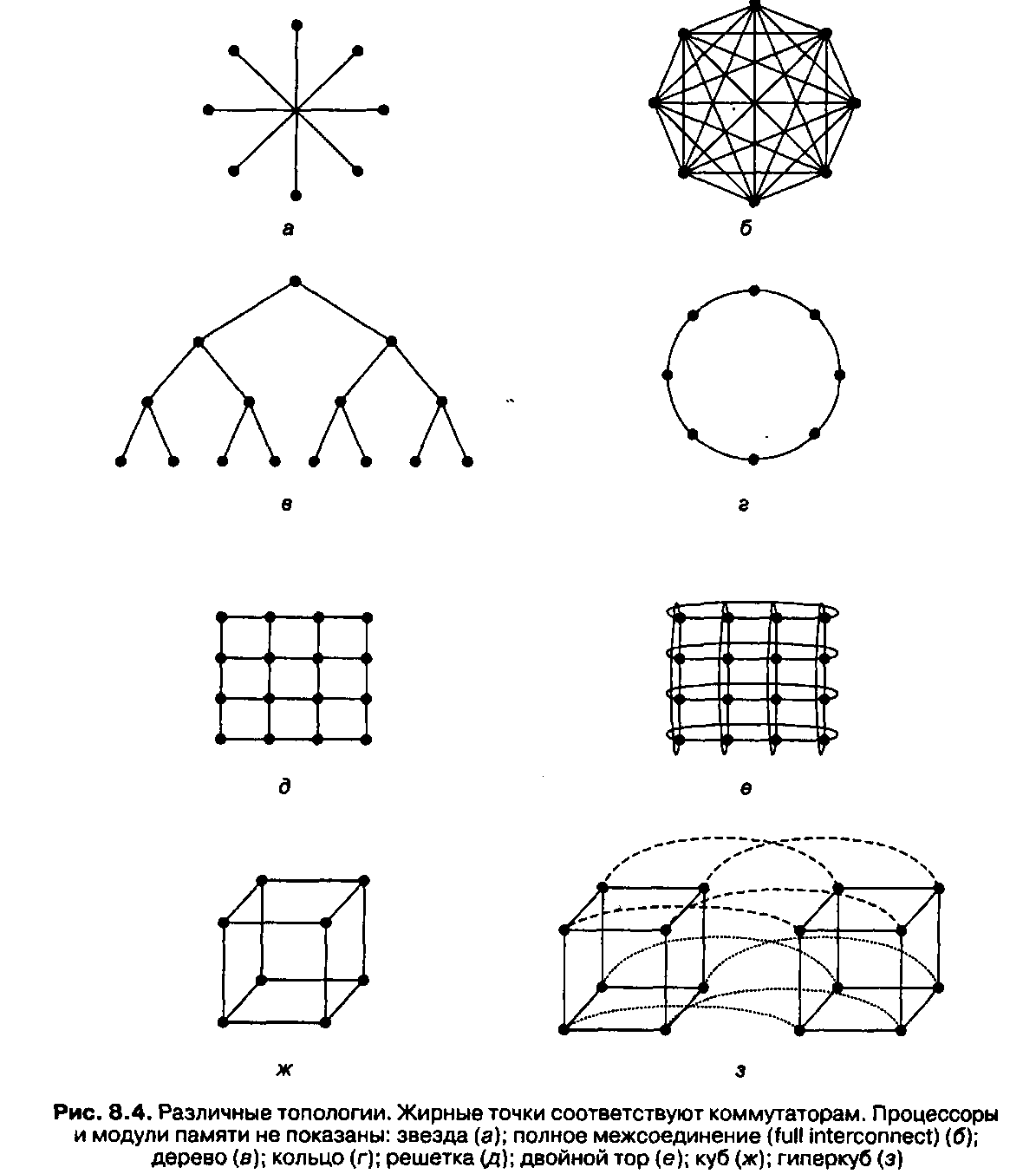

На рис. 8.4 показано несколько топологий. Здесь изображены только каналы связи (это линии) и коммутаторы (это точки). Модули памяти и процессоры (они на рисунке не показаны) подсоединяются к коммутаторам через интерфейсы.

На рис. 8.4, а изображена нульмерная конфигурация звезда, где процессоры и модули памяти прикрепляются к внешним узлам, а переключение совершает центральный узел. Такая схема очень проста, но в большой системе центральный коммутатор будет главным критическим параметром, который ограничивает производительность системы. И с точки зрения отказоустойчивости это очень неудачная разработка, поскольку одна ошибка в центральном коммутаторе может разрушить всю систему.

На рис. 8.4, б изображена другая нульмерная топология — полное межсоединение (full interconnect). Здесь каждый узел непосредственно связан с каждым имеющимся узлом. В такой разработке пропускная способность между двумя секциями максимальна, диаметр минимален, а отказоустойчивость очень высока (даже при утрате шести каналов связи система все равно будет полностью взаимосвязана). Однако для k узлов требуется k(k-1 )/2 каналов, а это совершенно неприемлемо для больших значений k.

На рис. 8.4, в изображена третья нульмерная топология — дерево. Здеь оновная проблема состоит в том, что пропускная способность между секциями равна пропускной способности каналов. Обычно у верхушки дерева наблюдается очень большой поток обмена информации, поэтому верхние узлы становятся препятствием для повышения производительности. Можно разрешить эту проблему, увеличив пропускную способность верхних каналов. Например, самые нижние каналы будут иметь пропускную способность Ь, следующий уровень — пропускную способность 2Ь, а каждый канал верхнего уровня — пропускную способность 4Ь.

Такая схема называется толстым деревом (fat tree). Она применялась в коммерческих мультикомпьютерах Thinking Machines' CM-5.

Кольцо (рис. 8.4, г) — это одномерная топология, поскольку каждый отправленный пакет может пойти направо или налево.

Решетка или сетка (рис. 8.4, д) — это двумерная топология, которая применяется во многих коммерческих системах. Она отличается регулярностью и применима к системам большого размера, а диаметр составляет квадратный корень от числа узлов (то есть при расширении системы диаметр увеличивается незначительно).

Двойной тор (рис. 8.4, е) является разновидностью решетки. Это решетка, у которой соединены края. Она характеризуется большей отказоустойчивостью и меньшим диаметром, чем обычная решетка, поскольку теперь между двумя противоположными узлами всего два транзитных участка.

Куб (рис. 8.4, ж) — это правильная трехмерная топология. На рисунке изображен куб 2х2х2, но в общем случае он может быть kxkxk.

На рис. 8.4, з показан четырехмерный куб, полученный из двух трехмерных кубов, которые связаны между собой. Можно сделать пятимерный куб, соединив вместе 4 четырехмерных куба. Чтобы получить 6 измерений, нужно продублировать блок из 4 кубов и соединить соответствующие узлы и т. д.; п-мерный куб называется гиперкубом. Эта топология используется во многих компьютерах параллельного действия, поскольку ее диаметр находится в линейной зависимости от размерности.

Другими словами, диаметр — это логарифм по основанию 2 от числа узлов, поэтому 10-мерный гиперкуб имеет 1024 узла, но диаметр равен всего 10, что дает очень незначительные задержки при передаче данных. Отметим, что решетка 32х32, которая также содержит 1024 узла, имеет диаметр 62, что более чем в шесть раз превышает диаметр гиперкуба. Однако чем меньше диаметр гиперкуба, тем больше разветвление и число каналов (и следовательно, тем выше стоимость). Тем не менее в системах с высокой производительностью чаще всего используется именно гиперкуб.

Характеристики графов межсоединений.

Коммутаторы для многопроцессорных вычислительных систем

Коммуникационные среды вычислительных систем (ВС) состоят из адаптеров вычислительных модулей (ВМ) и коммутаторов, обеспечивающих соединения между ними.

Используются как простые коммутаторы, так и составные, компонуемые из набора простых.

Простые коммутаторы могут соединять лишь малое число ВМ в силу физических ограничений, однако обеспечивают при этом минимальную задержку при установлении соединения.

Составные коммутаторы, обычно строящиеся из простых в виде многокаскадных схем с помощью линий «точка-точка», преодолевают ограничение на малое количество соединений, однако увеличивают и задержки.