- •Предисловие

- •Глава 1. Общие сведения о микропроцессорах

- •1.1 Классификация микропроцессоров

- •1.2 Характеристики микропроцессоров

- •1.2.1 Тактовая частота

- •1.2.2 Архитектура процессора

- •1.2.3 Технологический процесс производства

- •1.2.4 Частота системной шины

- •1.2.5 Размер кэша

- •1.3 Типы архитектур микропроцессоров

- •1.4 Структурная схема микропроцессоров

- •1.4.1 Микропроцессор Фон-Неймана

- •1.4.2 Конвейер

- •1.4.3 Зависимость между частотой и количеством ступеней конвейера

- •1.5 Представление информации в эвм

- •1.5.1 Двоичное представление целых чисел

- •1.5.2 Представление символьной информации

- •Глава 2. Архитектура микропроцессоров ia-32

- •2.1 Состав и функции регистров

- •2.1.1 Основные регистры

- •2.1.2 Регистры дополнительных функциональных модулей

- •2.2 Типы адресации

- •2.3 Система команд

- •2.3.1 Классификация команд

- •2.3.2 Формат команды

- •2.3.3 Однобайтовые команды

- •2.3.4 Непосредственно заданные операнды

- •2.3.5 Команды с регистровыми операндами

- •2.3.7 Команды с операндами, расположенными в памяти

- •Глава 3. Организация многоуровневой памяти

- •3.1 Принцип построения многоуровневой памяти

- •3.2 Организация кэш-памяти

- •3.3 Протоколы когерентности памяти микропроцессоров

- •3.4 Страничная организация памяти

- •Глава 4. Режимы работы процессоров ia-32

- •4.1 Обзор режимов работы

- •4.2 Реальный режим адресации

- •4.3 Защищённый режим

- •4.3.1 Дескрипторные таблицы

- •4.3.2 Дескрипторные регистры

- •4.3.3 Дескриптор

- •4.3.4 Односегментная модель памяти

- •4.3.5 Многосегментная модель памяти

- •Глава 5. Страничная организация памяти в процессорах ia‑32

- •5.1 Каталог страниц

- •5.2 Таблица страниц

- •5.3 Страничная переадресация

- •5.4 Диспетчер виртуальных машин системы Microsoft Windows

- •Глава 6. Архитектура процессоров с параллелизмом уровня команд

- •6.1 Подходы к использованию ресурса транзисторов в микропроцессорах

- •6.2 Суперскалярные процессоры и процессоры с длинным командным словом

- •6.3 Зависимости между командами, препятствующие их параллельному исполнению

- •6.4 Предварительная выборка команд и предсказание переходов

- •6.5 Условное выполнение команд в vliw-процессорах

- •6.6 Декодирование команд, переименование ресурсов и диспетчеризация

- •6.7 Исполнение команд

- •6.8 Завершение выполнения команды

- •6.9 Направления развития архитектуры процессоров с параллелизмом уровня команд

- •Глава 7. Мультитредовые микропроцессоры

- •7.1 Основы мультитредовой архитектуры

- •7.2 Выявление тредов

- •7.3 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков управления программы

- •7.3.1 Мультитредовая модель выполнения программы

- •7.3.2 Мультитредовые программы

- •7.3.3 Аппаратные средства мультитредовой архитектуры

- •7.3.4 Преимущества мультитредовой архитектуры

- •7.4 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков данных программы

- •7.5 Специфика мультитредовых моделей распараллеливания

- •Глава 8. Модуль обработки вещественных чисел

- •8.1 Представление чисел с плавающей запятой

- •8.2 Состав модуля fpu

- •Глава 9. Основы 64-разрядной архитектуры

- •9.1 Состав и назначение регистров микропроцессора ia-64

- •9.2 Особенности архитектуры epic

- •9.3 Архитектура x86-64

- •9.4 Структура одноядерного процессора

- •9.5 Многоядерные процессоры

- •9.6 Зачем нужны “лишние” разряды?

- •Глава 10. Современные 64-разрядные микропроцессоры корпораций Intel и amd

- •10.1 Архитектура Intel Core 2

- •10.1.1 Intel Wide Dynamic Execution

- •10.1.2 Intel Intelligent Power Capability

- •10.1.3 Intel Advanced Smart Cache

- •10.1.4 Intel Smart Memory Access

- •10.1.5 Intel Advanced Digital Media Boost

- •10.1.6 Логическая схема процессора

- •10.2 Архитектура Intel Core i7

- •10.2.1 Технология Hyper-Threading в архитектуре Nehalem

- •10.2.2 Иерархия кэш-памяти в архитектуре Nehalem

- •10.3 Хронология развития семейств микропроцессоров с архитектурой Nehalem

- •10.4 Архитектура amd Athlon 64

- •10.4.1 Ядро процессора

- •10.4.3 Контроллер памяти

- •10.4.4 Контроллер HyperTransport

- •10.5 Архитектура amd k10

- •10.4.1 Технология amd Memory Optimizer Technology

- •10.5.2 Ядро процессора

- •10.5.3 Предвыборка данных и инструкций

- •10.5.4 Выборка из кэша

- •10.5.5 Предсказание переходов и ветвлений

- •10.5.6 Процесс декодирования

- •10.5.7 Диспетчеризация и переупорядочение микроопераций

- •10.5.8 Выполнение микроопераций

- •10.5.9 Технологии энергосбережения

- •10.5.10 Шина HyperTransport 3.0

- •10.5.11 Семейство процессоров Barcelona

- •10.5.12 Семейство процессоров Phenom

- •Глава 11. Технологии, поддерживаемые современными микропроцессорами

- •11.1 Технологии тепловой защиты

- •11.1.1 Технология Thermal Monitor

- •11.1.2 Технология Thermal Monitor 2

- •11.1.3 Режим аварийного отключения

- •11.2 Технологии энергосбережения

- •11.2.1 Технология Enhanced Intel SpeedStep

- •11.2.2 Технология Cool'n'Quiet

- •11.3 Технология расширенной памяти

- •11.4 Технология антивирусной защиты

- •11.5 Технология виртуализации

- •11.6 Реализация технологий в современных микроархитектурах

- •11.6.2 Em64t – NetBurst

- •11.6.3 Intel Core

- •11.6.4 Intel Atom

- •11.6.5 Nehalem

- •11.6.6 Xeon

- •Глава 12. Графические микропроцессоры

- •12.1 Основные термины и определения

- •12.2 Технологии построения трёхмерного изображения

- •12.2.1 Технологии повышения реалистичности трехмерного изображения

- •12.3 Шейдерный процессор

- •12.4 Особенности современных графических процессоров

- •Глава 13. Однокристальные микроконтроллеры

- •13.1 Общая характеристика микроконтроллеров

- •13.2 Микроконтроллеры семейства avr

- •Почему именно avr?

- •13.3 Общие сведения об омк avr

- •13.4 Характеристики avr-микроконтроллеров

- •Глава 14. Технология производства микропроцессоров

- •14.1 Особенности производства процессоров

- •14.2 Новые технологические решения

- •14.3 Технология производства сверхбольших интегральных схем

- •I. Выращивание кристалла кремния

- •II. Создание проводящих областей

- •III. Тестирование

- •IV. Изготовление корпуса

- •V. Доставка

- •14.4 Перспективы производства сбис

- •Англо-русский словарь терминов и аббревиатур

- •Библиографический список

- •Интернет-ссылки

- •350072. Краснодар, ул. Московская, 2, кор. А.

1.2.3 Технологический процесс производства

Казалось бы, технологический процесс производства никак не отражается на производительности процессора. Действительно, прямой зависимости между проектной нормой процессора и его производительностью нет, однако от технологии производства процессоров, определяющей минимальные размеры используемых транзисторов, их быстродействие и время задержки передачи сигнала в межуровневых соединениях, зависит и его тактовая частота и размер кэша. Увеличение тактовой частоты просто невозможно без изменения технологического процесса производства процессора. То есть в пределах одного семейства процессоров, определяемого технологическим процессом производства, потенциальный запас по наращиванию тактовой частоты ограничен и дальнейшее увеличение тактовой частоты возможно только при уменьшении проектной нормы производства процессоров.

В 2009 году основным в процессорной индустрии является 45-нанометровый техпроцесс. Технологическая норма 32 нм освоена в 2010 г. Более тонкие технологические нормы (28 нм) планируется осваивать в 2011 году.

1.2.4 Частота системной шины

Частота системной шины определяет пропускную способность шины, связывающей процессор с набором микросхем системной платы (чипсетом). Естественно, что чем выше частота системной шины, тем выше и производительность процессора. Если говорить о процессорах Intel, то частоту системной шины называют частотой FSB (frequency system bus). К примеру, если частота FSB составляет 800 МГц, то ее пропускная способность (с учетом 64-битной или восьмибайтной шины) составляет 6,4 Гбайт/с. Для шины FSB с частотой 1066 МГц пропускная способность составит уже 8,5 Гбайт/с. Для процессоров Intel частота FSB может быть равной 400, 533, 800 и 1066 МГц.

В случае процессоров AMD системная шина называется HyperTransport. Частота этой шины для современных процессоров AMD может быть равной единицам гигагерц.

1.2.5 Размер кэша

Как уже отмечалось, современный процессор имеет несколько типов кэша, интегрированных в кристалл процессора: кэш первого уровня (L1) и кэш второго уровня (L2). Кэш L1, который делится на кэш команд и кэш данных, используется непосредственно ядром процессора. Кэш L2 представляет собой своеобразный буфер между оперативной памятью (кэшем третьего уровня, размещённым на системной плате) и кэшем L1. В пределах одного семейства процессоры могут различаться размером кэша L2. Непосредственного влияния на производительность процессора размер кэша не оказывает, однако при недостаточном размере кэша увеличивается время простоя процессора, в течение которого в кэш загружаются данные из оперативной памяти. Это, в свою очередь, отражается и на производительности процессора. Поэтому чем больше размер кэша L2, тем лучше.

1.3 Типы архитектур микропроцессоров

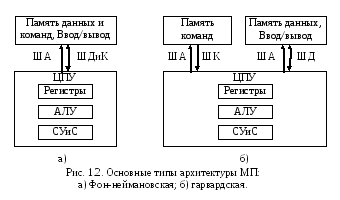

Существует два основных типа архитектуры – фоннеймановская (принстонская) и гарвардская.

Фоннеймановскую архитектуру предложил в 1945 году американский математик Джон фон Нейман, работавший в то время в университете Принстона. Особенностью этой архитектуры является то, что программа, данные и область ввода/вывода находятся в общей памяти, доступ к которой осуществляется по шине данных и команд ШДиК (Data and Command Bus). Такая шина данных и команд, как правило, мультиплексируется с шиной адреса ША (Address Bus).

Мультиплексирование – это способ передачи разнородных данных по одной шине посредством разделения времени передачи между разнородными данными с использованием переключателя (мультиплексора). В один квант времени по шине передаются, например адреса для записи данных в ОЗУ. В следующий квант времени, который наступает после переключения шины с адресных контактов на контакты данных, по ней передаются данные для записи в ОЗУ. Это замедляет процесс обращения к ОЗУ по записи/чтению, но упрощает исполнение шины в кристалле. Кроме этого в случае сбоя в мультиплексированной шине возможно чтение из ОЗУ данных вместо команд, что ведёт к попытке исполнения данных как команд и как следствие ‑ зависанию выполняемого приложения.

Достоинствами фоннеймановской архитектуры является простота реализации и дешевизна, недостатками – низкое быстродействие и надёжность по сравнению с гарвардской архитектурой.

Гарвардская архитектура впервые была реализована в 1944 году в релейной вычислительной машине Гарвардского университета (США). Особенностью этой архитектуры является то, что память данных, память программ и область ввода/вывода разделены и имеют отдельную шину данных ШД (Data Bus) и шину команд ШК (Command Bus). Достоинствами гарвардской архитектуры является высокое быстродействие и надёжность функционирования, т.к. сбои, присущие фоннеймановской архитектуре и связанные с попыткой исполнения данных, невозможны. Недостатками являются более сложные схемы управления и высокая стоимость.

На рисунке 1.2 изображены структурные схемы двух типов архитектуры МП. Центральное процессорное устройство ЦПУ (CPU ‑ Central Processing Unit) содержит регистры для хранения данных, АЛУ и схему управления и синхронизации СУиС (control unit).