- •Логические функции и логические элементы.

- •Основные понятия

- •Представление информации физическими сигналами.

- •Логические функции.

- •Законы алгебры логики

- •Произвольные функции и логические схемы

- •Минимизация функций

- •Интегральные логические элементы.

- •Характеристики лэ.

- •Серии лэ.

- •Правила схемного включения лэ.

- •Лэ с тремя состояниями выхода

- •Этапы построения (синтеза) комбинационной схемы.

- •Типовые комбинационные устройства

- •Преобразователи кодов (пк)

- •3.1.1 Дешифраторы.

- •3.1.2. Шифраторы

- •3.1.3. Преобразование произвольных кодов.

- •Коммутаторы.

- •Мультиплексоры.

- •Демультиплексоры.

- •Арифметические устройства.

- •Сумматоры.

- •Цифровые компараторы.

- •Контроль четности

- •Постоянные запоминающие устройства.

- •Параметры пзу.

- •Построение блоков памяти на бис пзу.

- •Применение пзу для реализации произвольных логических функций.

- •Программируемые логические матрицы.

- •Последовательностные схемы

- •Триггеры

- •4.1.1 Rs-триггер

- •4.1.2. D - триггер типа «защелка»

- •4.1.3. Двухступенчатые триггеры

- •4.1.4. Асинхронные входы триггеров

- •4.2. Регистры

- •4.2.1. Параллельные регистры

- •4.2.2. Регистровая память

- •4.2.3. Сдвигающие регистры

- •4.3. Счетчики

- •4.3.1. Общие понятия

- •4.3.2. Асинхронные счетчики

- •4.3.3. Синхронные счетчики

- •4.3.4. Интегральные счетчики.

- •4.3.5. Счетчики с различными коэффициентами пересчета.

- •4.3.6. Применение счетчиков

- •Оперативные запоминающие устройства (озу)

- •4.4.1. Разновидности оперативной памяти

- •4.4.2. Построение блоков озу

- •Содержание

4.1.2. D - триггер типа «защелка»

D-триггеромназывают синхронный триггер, имеющий два входа: вход данныхDи вход синхронизацииС.Этот тип триггера исключительно широко используется в цифровых устройствах. Другие его названия:прозрачная защелка (transparent latch), D-триггер, управляемый уровнем синхросигнала. D-триггер переключается только по сигналу на С-входе и притом в состояние, предписываемое D-входом. Условное обозначениеD-триггера показано на рис. 4.3, а.

а) б)

Рис.4.3. D– триггер

На рис. 4.3, бпоказан универсальный способ построенияD-триггера из синхронногоRS-триггера: с помощью инвертора 1 однофазный вход данныхDпревращается в парафазный и подается наS- иR-входы.

Изменения D-входа при С= 0 никак не влияют на состояние выхода Q: триггер заперт по С-входу и находится врежиме хранения.Фронт С-сигнала вызывает переключение триггера в то состояние, которое было к этому моменту на входе D. При С=1 защелка прозрачна: любое изменение D-входа вызывает изменение выхода Q. По спаду синхросигнала триггер – защелкафиксируетна выходе то состояние, которое было на D-входе непосредственно перед этим моментом. Следующее изменение Q будет возможно только по фронту следующего синхроимпульса. Если на С-вход подать постоянный единичный уровень, то свойство запоминания у защелки проявляться никак не будет и она будет выполнять функции обычного буферного усилителя мощности в тракте передачи данных.

Чтобы процесс фиксации состояния D-входа прошел без сбоев, т. е. был бы однозначно предсказуемым, переходной процесс в схеме защелки, вызванный срезом С-сигнала, не должен накладываться на переходной процесс, вызванный переключением D-входа. Это значит, что всякие изменения состояния D-входа должны прекратиться за некоторое время до среза С-сигнала, называемое временем подготовки (setup time), и могут снова начинаться после среза С-сигнала не ранее чем черезвремя выдержки (удержания) (hold time).

Необходимость введения и нормирования интервалов подготовки и выдержки характерна не только для защелки, но и для всех функциональных узлов, имеющих вход синхронизации. Кроме того, для защелки, как и для любого синхронного узла, существует минимально допустимая длительность синхроимпульса,обеспечивающая отсутствие сбоев из-за наложения переходных процессов от фронта и среза этого импульса.

Для триггеров-защелок, выпускаемых в виде микросхем, временные характеристики приводятся в справочниках. Примерами выпускаемых промышленностью D-триггеров-защелок могут служить интегральные микросхемы (ИМС) К155ТМ5, К155ТМ7, К561ТМЗ, которые содержат по четыре триггера с объединенными С-входами.

4.1.3. Двухступенчатые триггеры

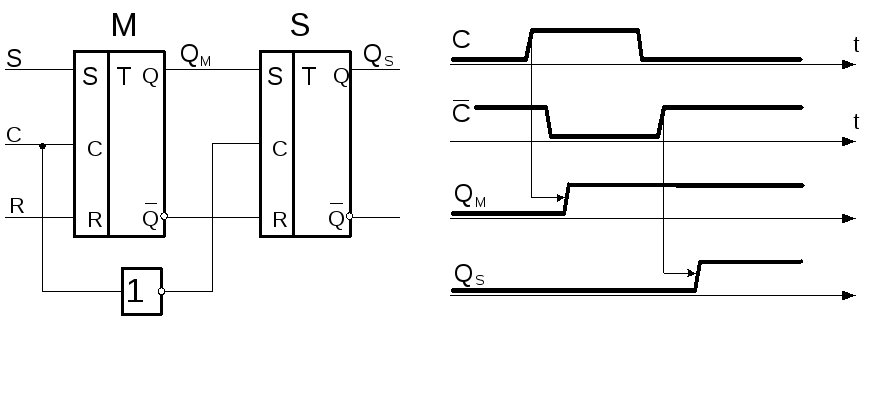

На рис. 4.4, апоказана схема, состоящая из двух последовательно включенных синхронныхRS-триггеров, первый из которых называетсяведущимилиМ-триггером(отmaster -хозяин), а второй—ведомымилиS-триггером (отslave - раб). Благодаря общему синхросигналу С вся схема функционирует как единое целое и называетсядвухступенчатымилиMS-триггером . Из временной диаграммы (рис. 4.4,б)видно, что информация, задаваемая уровнями на входахSиR,по фронту С-сигнала принимается в М-триггер, но в течение всего •времени, пока С-сигнал равен 1, не проходит в S-триггер, поскольку его входные конъюнкторы 5 и 6 в это время перекрыты инверсией С-сигнала. Они откроются лишь при С==1, т.е. на спаде С-сигнала, и только тогдаS-триггер примет состояние М-триггера. Сказанное иллюстрирует очень важное отличиеMS-триггера от триггера-защелки:MS-триггер, собранный по схеме рис.4.4,а,непрозраченпо управляющимRиSвходам ни при С=0, ни при С=1. Каждая ступень его сама по себе прозрачна, но включены ступени последовательно, и какая-нибудь одна из них всегда оказывается запертой - или синхросигналом, или его отсутствием. Таким образом, в этом MS-триггере при С=1 (и тем более при С=0) никакое изменение на управляющем входе не может само по себе, без переключения С-сигнала, проникнуть на выход. Триггер может изменить состояние выхода только по спаду С-сигнала. В зарубежной литературе непрозрачные триггеры называют flip-flop в отличие от прозрачных D-триггеров, за которыми укрепился терминlatch.

а) б)

а) б)

Рис. 4.4; Двухступенчатый RS-триггер

Управляющие S- и R-сигналы могут обновляться по спаду того же синхроимпульса, который управляет триггером, и триггер при этом всегда будет воспринимать лишь предыдущее, еще не обновленное состояние S иRсигналов. На этом свойстве держится вся идеология однофазной синхронизации.

Свойство непрозрачности MS-триггера использовано для построения широко применяемогоJK-триггера,схема которого показана на рис.4.5,а

Рис.4.5. JK– триггер

JK-триггер-это непрозрачный триггер, выходы которого петлями обратных связей накрест заведены на входные конъюнкторы 1 и 2. Внешние входы самого триггера при этом принято называть уже не S и R,аJи К.

При J=K=0 С-сигнал не может открыть входные элементы 1 и 2,и триггер находится в режиме хранения. ПриJ=1, К=0синхросигналом может быть открыт лишь элемент 1 и только при условии, что перед поступлением С-сигнала на выходе триггера был 0 (Q=0). Тогда по спаду синхросигнала триггер переключится в «1». Если же триггер до синхросигнала был в «1», то он так и останется в «1». Таким образом, J-вход выполняет функции синхронизированного S-входа. В силу симметрии схемы легко показать, что K-вход выполняет функции синхронизированногоR-входа, переводя триггер в «0». Таким образом, при разных уровнях наJ- и К-входахJK-триггер ведет себя как синхронный непрозрачныйRS-триггер.

Существенно отличным от RS-триггера является поведение JK-триггера приJ=K=1. ДляRS-триггера такое сотояние входов запрещено. Диаграмма работыJK-триггера в этом режиме показана на рис. 4.5,б. При любом состоянии триггера сигналы обратной связи открывают для С-сигнала именно тот входной конъюнктор, пройдя через который, С-сигнал переведет триггер в противоположное состояние. Таким образом, приJ=K=1 по спаду каждого С-сигналаJK-триггер меняет состояние своих выходов на противоположное. Это так называемыйсчетныйрежим, или Т-режим работы триггера (отtoggle—кувыркаться).

Кратко функционирование JK-триггера описывается табл. 4.1. Новым символом в таблице является символ спада синхроимпульса, который изображается направленной вниз стрелкой. Таблица отражает тот факт, что дляJK-триггера переключающей сущностью синхроимпульса является не уровень его, а перепад уровня.

Таблица 4.1.

|

Режим |

С |

Jt |

Kt |

Qt+1 |

|

Хранение |

X |

0 |

0 |

|

|

Сброс |

|

0 |

1 |

0 |

|

Установка |

|

1 |

0 |

1 |

|

Инверсия предыдущего состояния |

|

1 |

1 |

|

С

Счетный