Физические основы микроэлектроники (ФОМ)

.pdf

71

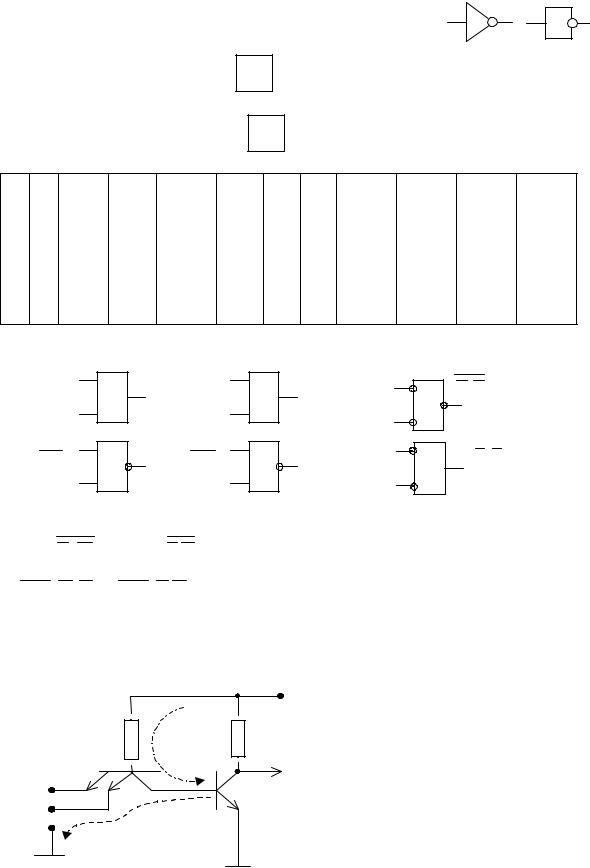

Логические элементы в цифровых устройствах

Транзисторный ключ выполняет операцию логического НЕ. (на входе “1”, а на выходе ”0”)

Логическое умножение “И” &

Логическое сложение “ИЛИ” 1

ИИЛИ

A |

B |

A*B |

A*B |

|

A+B |

A+B |

|

|

|

|

|

|

|

* |

|

|

|

|

* |

|

|

|

|

+ |

|

|

|

|

+ |

|

|

|

|

A |

|

B |

A |

B |

A |

B |

A |

B |

A |

B |

|||||||||||||||||||||

1 |

2 |

3 |

4 |

|

5 |

6 |

|

7 |

8 |

9 |

|

|

|

10 |

|

|

11 |

|

12 |

|

|

|

||||||||||

0 |

0 |

0 |

1 |

|

0 |

1 |

|

1 |

1 |

1 |

|

|

|

0 |

|

|

|

1 |

|

|

0 |

|

|

|

|

|||||||

0 |

1 |

0 |

1 |

|

1 |

0 |

|

1 |

0 |

0 |

|

|

|

1 |

|

|

|

1 |

|

|

0 |

|

|

|

|

|||||||

1 |

0 |

0 |

1 |

|

1 |

0 |

|

0 |

1 |

0 |

|

|

|

1 |

|

|

|

1 |

|

|

0 |

|

|

|

|

|||||||

1 |

1 |

1 |

0 |

|

1 |

0 |

|

0 |

0 |

0 |

|

|

|

1 |

|

|

|

0 |

|

|

1 |

|

|

|

|

|||||||

|

Прямая логика |

|

Обратная логика. |

||

Y=A*B |

& |

Y=A+B |

1 |

& A*B |

|

|

|

||||

Y=A*B |

& |

Y=A+B |

1 |

1 |

A+B |

|

|

|

|||

Теоремы Моргана |

|

|

|

||

A*B=A+B |

|

A+B=A*B |

Выполняют преобразование из одного базиса в другой |

||

|

|

|

Можно реализовать любую функцию, только имея |

||

A*B=A+B |

A+B=A*B |

“ИЛИ-НЕ” и ”И-НЕ”. |

|

|

|

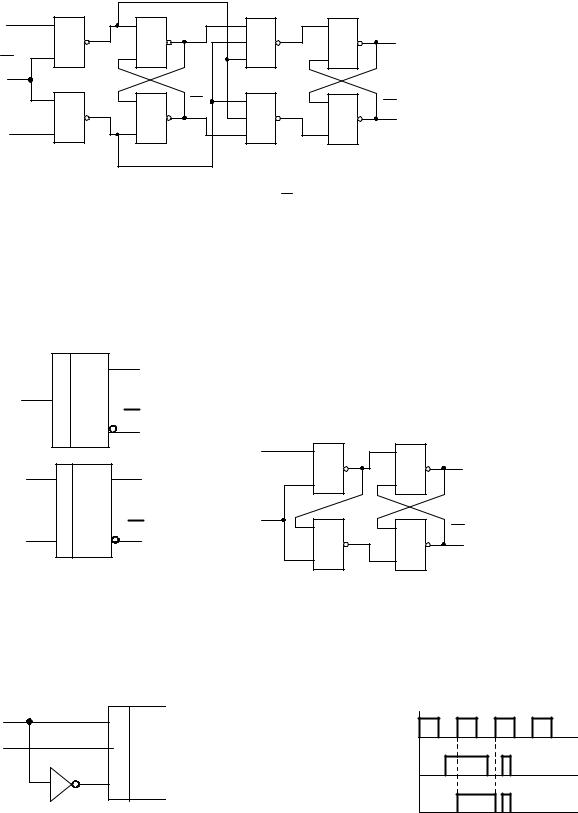

Интегральная транзисторно-транзисторная логика (ТТЛ).

Реализация “И-НЕ”

|

|

|

+Eп |

|

Rб |

|

Rк |

|

|

i1 |

Uвых |

|

|

|

|

A |

VT2 |

|

VT1 |

B |

|

|

|

i2 |

|

|

|

|

|

|

VT1многоэмиттерный транзистор (существует только в интегральном исполнении).

Если на оба входа VT1 подать ”+” (логическая “1”), то коллектор VT1 смещается в прямом направлении, а эмиттер в обратном. Протекает ток i1, на базу VT2 поступает положительный потенциал VT2 открывается, а на выходе 0. Если хотя бы один вход заземлить (логический “0”), то эммитер-

72

ный переход VT1 смещается в прямом направлении. VT1 открывается и ток i2 течет из базы VT2, закрывая его. На выходе VT2 появляется высокий потенциал (логическая “1”). Работа схемы соответствует функции “И-НЕ”.

Реализация “ИЛИ-НЕ” |

|

|

|

|

|

|

+ E п |

R 1 |

R 2 |

R 3 |

R 4 |

A |

|

V T 1 |

|

V T 01 |

|

|

|

B |

V T 02 |

|

U вых |

|

V T 2 |

||

|

|

||

|

|

V T 3 |

|

|

|

|

|

Транзисторы VT1 и VT2 включены параллельно. Если A=B=0 (заземлены), то VT01 и VT02 открыты, а VT1 и VT2 закрыты на базе VT3 отрицательный потенциал, VT3 тоже закрыт на выходе логическая 1.

Если на любой из входов подать “+” (логическая единица), то соответствующий VT (VT01 или VT02) открывается, тогда открывается VT1 или VT2 и на базу VT3 поступает положительный потенциал VT3 открывается и на выходе 0. Схема выполняет функцию ”ИЛИ-НЕ”

73

Триггеры

Триггер – одно из наиболее распространенных импульсных устройств, относящийся к базовым элементам цифровой техники.

Триггером называют устройство, обладающие двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала.

Сигнал управления подается по определенному алгоритму, который определяет работу триггера. Типы триггеров RS, D, T, JK.

Классификация:

1)По алгоритму функционирования - RS, D, T, JK.

2)По способу синхронизации а) Асинхронные б) Синхронизируемые

По уровню: |

синхронизируемые ”1” |

C |

|

|

синхронизируемые ”0” |

C |

|

|

|

|

|

По фронту: |

синхронизируемые положительным фронтом |

C |

|

|

синхронизируемые отрицательным фронтом |

C |

|

|

|

|

|

Асинхронный RS триггер

Являются основным элементом триггеров всех типов, т. к. выполняют функцию бистабильной ячейки. Реализуется на двух элементах “ИЛИ-НЕ”.

R |

|

|

|

1 |

Q |

T |

Q |

|

R |

|

|

|

S |

|

Q |

1 |

|

|

|

Q |

|

|

|

S |

|

|

|

Допустим, что на входах R и S сигналы равны ”0” (R=0, S=0), а на прямом выходе Q сигнал равен “1” (Q=1).Тогда на инверсном выходе Q сигнал равен “0”так как на одном из входов (соединенном с Q) сигнал равен “1”. Очевидно, при R=0, S=0 возможно и второе устойчивое состояние, при котором Q=0, Q =1. Нетрудно видеть, что при S=1, R=0 триггер оказывается в первом устойчивом состоянии (Q=1, Q =0), а при S=0, R=1 – во

втором устойчивом состоянии (Q=0, Q =1). Комбинация S=1, R=1 ( × ) запрещенное со-

стояние, выходному сигналу верить нельзя.

Рассмотренный триггер называется RS –триггером. Вход S называется устойчивым (от англ. setустанавливать), а вход R–входом сброса (от англ. reset–вновь устанавливать).

При S=1 триггер устанавливается в состояние ”1” (Q=1, Q =0), при R=1 – сбрасывается в состояние ”0” ( Q=0, Q =1).

|

|

|

|

|

74 |

|

S |

S |

R |

Qn Qn+1 |

хранение |

||

|

0 |

0 |

0 |

0 |

||

R |

информации |

|||||

0 |

0 |

1 |

1 |

|||

Q |

0 |

1 |

0 |

0 |

установка0 |

|

0 |

1 |

1 |

0 |

|||

Q |

1 |

0 |

0 |

1 |

установка1 |

|

1 |

0 |

1 |

1 |

запрещенный |

||

|

1 |

1 |

0 |

* |

||

|

1 |

1 |

1 |

* |

режим |

|

Аналогично работает RSтриггер на элементах И-НЕ с той разницей, что он должен иметь инверсные входы, т. е. В состояние “1” при S=0 и сбрасывается в состояние ”0” при R=0. Запрещенная комбинация входных сигналов для этой схемы - ”0”, “0”.

S |

|

|

|

& |

Q |

T |

Q |

|

S |

|

|

|

R |

|

Q |

& |

|

|

|

Q |

|

|

|

R |

|

|

|

S |

S |

R |

Qn |

Qn+1 |

запрещенный |

|

|

0 |

0 |

0 |

* |

||

R |

0 |

0 |

1 |

* |

режим |

|

0 |

1 |

0 |

1 |

установка1 |

||

|

||||||

Q |

0 |

1 |

1 |

1 |

||

|

||||||

1 |

0 |

0 |

0 |

установка0 |

||

|

||||||

Q |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

0 |

хранение |

||

|

||||||

|

1 |

1 |

1 |

1 |

информации |

Рассмотренный RSтриггер относится к асинхронным, так как переход из одного состояния в другое происходит в темпе поступления сигналов на информационные (R,S) входы и не связан с тактовыми сигналами.

|

|

|

RS – триггер, синхронизируемый по уровню |

|||

S |

& |

S |

& |

Q |

S T Q |

|

|

|

|

||||

C |

|

|

|

|

C |

Q |

|

& |

R |

& |

Q |

R |

|

R |

|

|||||

|

|

|

|

|

|

|

75

В синхронных триггерах помимо информационных имеется вход тактовых (синхронизирующих) сигналов и переключения триггера происходит только при наличии тактового сигнала.

Отличие от асинхронного триггера наличие двух дополнительных элементов И-НЕ,

благодаря которым управляющие сигналы проходят на входы R и S только при воздействии на синхронизирующий вход сигнала “1” (C=1).

C |

|

C |

S |

R |

Qn+1 |

S |

хранение |

|

0 |

0 |

|

0 |

0 |

1 |

|

||

|

Qn |

||||

R |

информации |

|

1 |

0 |

|

|

|

1 |

1 |

Qn |

|

Q |

установка0 |

|

0 |

0 |

|

|

0 |

1 |

0 |

||

Q |

установка1 |

1 |

1 |

0 |

1 |

запрещенный |

|

1 |

1 |

* |

|

|

режим |

|

|

|

|

|

RS – триггер на ИЛИ-НЕ |

|

|

|

|

S |

1 |

1 |

Q |

|

R T |

Q |

|

|

|

||||||

С |

|

|

|

|

|

||

|

|

|

|

C |

|

|

|

|

1 |

|

|

|

|

Q |

|

R |

1 |

Q |

|

S |

|

||

|

|

|

|

||||

|

|

|

|

|

|

|

|

C |

|

|

C |

S |

R |

Qn+1 |

|

|

|

|

|

||||

S |

|

|

|

0 |

0 |

* |

|

|

|

|

0 |

0 |

1 |

1 |

|

R |

|

|

|

1 |

0 |

0 |

|

|

|

|

1 |

1 |

Qn |

|

|

Q |

|

|

|

0 |

0 |

Qn |

|

|

|

1 |

0 |

1 |

|

||

Q |

|

|

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

|

|

76

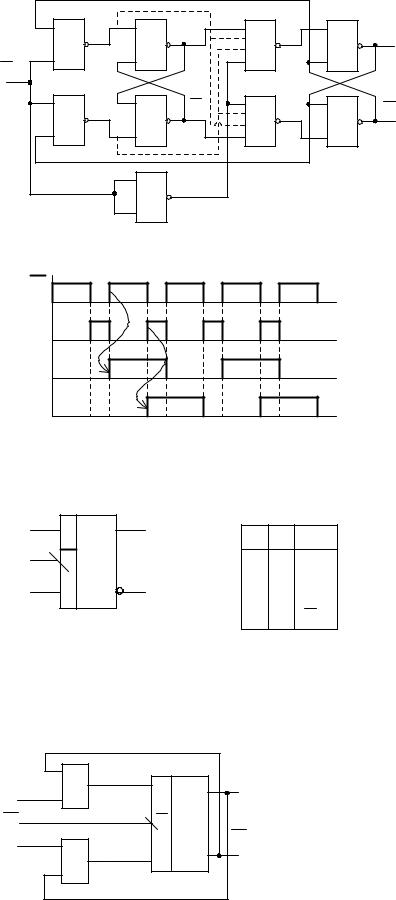

RS – триггер синхронизируемый по фронту.

R T Q  C

C

S Q

Таблица состояний аналогична таблице RS-триггера, синхронизированного по уровню.

Реализуется при помощи схемы MS (Master-Slave – начальникподчиненный):

1.С инвертором

2.С запрещающими связями

Содержит два синхронизируемых по уровню RS триггера, один из которых управляется импульсом синхронизации, а второй – паузой.

MS-схема с инвертором |

|

|

|

|||

|

|

M |

S |

Q |

|

|

S |

S T Q1 |

S T |

R TT Q |

|||

C |

C |

|

C |

|

C |

|

R |

Q1 |

Q |

|

|||

R |

R |

S |

Q |

|||

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

C

C

C

S

S

R

Q1

Q

S |

|

M |

|

& |

& |

||

|

|||

C |

DD 1 |

DD 3 |

|

|

|

||

|

& |

& |

|

R |

DD 2 |

DD 4 |

|

|

|||

|

|

& |

DD 9

Q1

Q1

М- триггер запускается под действием С и управляется S и R, а S-триггер подтверждает состояние M-триггера с приходом импульса С, т.е. происходит перезапись информации из М-триггера в S-триггер по заднему фронту синхронизации.

|

S |

|

& |

& |

Q |

DD 5 |

DD 7 |

|

& |

& |

Q |

DD 6 |

DD 8 |

|

77

В реальных схемах исключают инвертор. Инверсию схемы можно взять на схемах DD1 и DD2 тогда такой триггер будет с запрещающими связями.

S |

& |

& |

Q1 |

|

|||

C |

DD 1 |

DD 3 |

|

|

|

|

|

R |

& |

& |

Q1 |

DD 2 |

DD 4 |

|

|

|

|

& |

& |

Q |

DD 5 |

DD 7 |

|

& |

& |

Q |

DD 6 |

DD 8 |

|

Если сигнал S заканчивается раньше, чем С , то (т.е. на входе S DD1 или R DD2 формируется 0), Тогда на выходах DD1(DD2) формируется 1, которая отпирает схемы DD5, DD6, обеспечивая переброс DD7, DD8.

D – триггер

Для приема информации по одному входу используется D-триггер.

T |

Q |

Асинхронный D-триггер не используют, а используют синхрони- |

||

|

зируемый по уровню или по фронту. |

|

||

D |

|

D-триггер на И-НЕ –упрощают, в качестве инвертора использует- |

||

Q |

ся DD1. |

|

|

|

|

D |

|

|

|

|

|

|

Q |

|

D T |

Q |

& |

& |

|

DD 1 |

DD 3 |

|

||

|

|

|||

|

|

C |

|

|

С |

Q |

& |

& |

Q |

|

|

|

|

|

|

|

DD 2 |

DD 4 |

|

D-триггер переходит в состояние “1” (Q=1), если в момент синхронизирующего сигнала (С=1) на его информационном входе сигнал ”1” (D=1). В этом состоянии триггер остается и после окончания сигнала на входе D до прихода очередного синхронизирующего сигнала, возвращающего триггер в состояние “0”. Таким образом, D-триггер “задерживает” поступившую на его вход информацию на время, равное периоду синхронизирующих сигналов. D-триггер можно получить из RS-триггера.

D |

S |

T |

|

C |

|||

C |

|

||

|

|

||

|

R |

|

|

Q |

|

|

|

|

|||

|

|

|

|

|

||||

|

|

n+1 |

|

|||||

|

|

|

|

|

C |

D |

Q |

C |

|

|

|

|

|

||||

|

|

|

|

|

0 |

0 |

Qn |

D |

|

|

|

|

|

0 |

1 |

|

|

|

Q |

|

|

|

||||

|

|

|

1 |

0 |

0 |

|

||

|

|

|

|

|||||

|

|

|

|

|

1 |

1 |

1 |

Q |

|

|

|

|

|

||||

Недостаток: Если на вход D пройдет помеха, то она появится и на выходе.

78

D-триггер синхронизируемый по фронту на MS-схеме

D |

|

Q1 |

& |

& |

|

& |

& |

Q |

|||

DD 1 |

DD 3 |

|

DD 5 |

DD 7 |

|

& |

& |

Q1 |

& |

& |

Q |

C |

|

|

|

|

|

DD 2 |

DD 4 |

|

DD 6 |

DD 8 |

|

|

& |

|

|

|

|

|

DD 9 |

|

|

|

|

М-триггер реализован по схеме D-триггера с синхронизацией по уровню. S - триггер - обычная схема с инвертором (DD9), либо по схеме с запрещающими связями. Перезапись информации из D->S происходит по заднему фронту импульса синхронизации. D-триггер синхронизированный по фронту и по уровню называют триггером задержки – запись происходит по импульсу синхронизации, т.е. это либо регистр памяти, либо регистр сдвига.

D |

TT |

Q |

C |

|

|||

|

D |

||

|

|

|

|

С |

|

Q |

Q1 |

|

|

|

Q |

Т-триггер

В режиме двоичного счета при наличии импульса управления меняет свое состояние на обратное. Может быть реализован на любом другом триггере с использованием внутренних обратных связей.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Т |

Qn |

Qn+1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

TT |

|

|

|||||

0 |

0 |

0 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||||

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

||

|

T |

|

|

|

|

|

|

||||||

|

C |

|

|

|

|||||||||

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||||||

1 |

1 |

0 |

|

|

|

|

|

R |

|

|

|

||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

79

|

Т-триггер на RS по MS-схеме |

|

|

|||

|

& |

& |

Q1 |

& |

& |

Q |

T |

DD 1 |

DD 3 |

|

DD 5 |

DD 7 |

|

|

|

|

|

|

|

|

|

& |

& |

Q1 |

& |

& |

Q |

|

DD 2 |

DD 4 |

|

DD 6 |

DD 8 |

|

|

|

& |

|

|

|

|

|

|

DD 9 |

|

|

|

|

Вместо инвертора используют запрещающие связи. |

T |

T |

Q1 |

Q |

Т-триггер делит входную частоту пополам. |

JK-триггер

J TT |

J |

K |

Qn+1 |

С |

0 |

0 |

Qn |

K |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

1 |

1 |

Q n |

Вход J выполняет установку 1, а вход К установку 0.

Если J*K≠ 1, то JK-триггер аналогичен RS-триггеру, где R≡ S, а K≡ R. Если J*K=1, то JK-триггер работает, как Т-триггер.

|

JK-триггер на MS-схеме |

|

||

J |

& |

S |

TT |

Q |

|

|

|||

|

СC |

|

|

|

C |

|

|

Q |

|

K |

& |

S |

|

|

|

|

R |

|

|

S |

|

|

|

|

|

|

J |

& |

& |

Q1 |

& |

& |

Q |

C |

DD 1 |

DD 3 |

|

DD 5 |

DD 7 |

|

|

|

|

|

|

|

|

K |

& |

& |

Q1 |

& |

& |

Q |

|

DD 2 |

DD 4 |

|

DD 6 |

DD 8 |

|

R |

|

|

|

|

|

|

80

|

|

|

|

|

Q |

|

S |

|

TT |

||

|

|

|

|

|

|

& |

|

|

|

|

|

|

J |

|

|

|

|

C

C

&K Q

&K Q

R

S и R - установка начального состояния триггера.

JK-триггер является универсальным на нем можно реализовать любую функцию.

|

|

|

Из JK→ |

|

RS |

|

|

|

|

Из JK → |

T |

|

|

|

|

|

|

Из JK→ D |

|||||||||||||||||||||||

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

J |

|

TT |

|

|

|

|

|

|

|

|

J |

TT |

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

TT |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

R |

|

|

|

|

|

|

|

|

|

|

"1" |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

Из D → |

|

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

D |

TT |

|

|

|

|

|

Словарь переходов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

|

RS |

|

JK |

|

|

D |

T |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

|

R |

J |

|

K |

|

|

|

|

|

||||||

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

|

* |

0 |

|

* |

0 |

0 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

∆ |

|

1 |

|

|

0 |

1 |

|

* |

1 |

1 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

* |

|

|

0 |

* |

|

0 |

1 |

0 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

* |

|

1 |

0 |

1 |

|

|

|

|

|||