Физические основы микроэлектроники (ФОМ)

.pdf

91

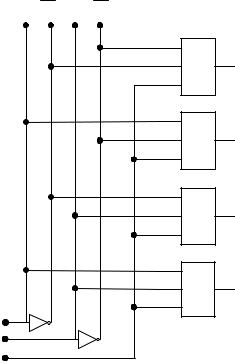

Демультиплексор

S0 |

S0 S1 S1 |

|

& |

|

Y0 |

|

& |

|

Y1 |

|

& |

|

Y2 |

|

& |

|

Y3 |

S0 |

|

S1 |

|

DI |

|

Выполняет коммутацию одного входа DI на несколько выходов. Управление выполняется комбинацией сигналов S0 и S1.

|

DI |

DMS |

DO |

|

|

|

|||

|

S0 |

|

Y0 |

|

|

|

|

||

|

|

Y0 |

|

|

|

|

|

||

|

S1 |

|

|

|

|

|

Y0 |

|

|

|

|

|

|

|

|

|

|

Y0 |

|

|

|

|

|

|

|

|

|

|

|

Мультиплексор – Демультиплексор

|

|

|

|

Работает |

|

|

|

DMS |

DI/O |

||

|

|

как MS |

|||

|

|

|

0 |

|

|

|

|

|

|

|

|

|

S 0 |

|

1 |

|

|

|

|

|

|

||

|

|

|

2 |

|

|

|

|

|

|

|

|

|

S 1 |

|

3 |

|

|

|

|

|

|

||

|

|

|

4 |

|

|

|

|

|

|

|

|

|

S2 |

|

5 |

|

|

|

|

|

|

||

|

|

|

|

||

|

|

|

6 |

|

|

|

|

|

|

|

|

|

EI |

|

7 |

|

|

|

|

|

|

||

|

|

DO/I |

|

|

|

|

|

|

|

||

|

|

Работает |

|||

|

|

|

|

||

|

|

|

|

||

|

|

|

|

как DMS |

|

92

|

|

|

|

|

Комбинатор (Шифратор) |

|

||

Комбинатор – устройство, преобразующее число в код. |

|

|||||||

0 |

1 2 3 4 5 6 7 |

|

|

|

|

|

||

|

|

|

|

|

1 |

|

|

CD |

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

2 |

1 |

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

4 |

2 |

|

|

|

|

|

|

2 |

5 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

6 |

4 |

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

8 |

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

Декомбинатор (Дешифратор) |

|

|||

|

|

& |

|

1 |

|

|

|

|

|

|

|

|

|

1 |

DC |

1 |

|

|

|

& |

|

|

|

|

2 |

|

|

|

|

2 |

2 |

|

3 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

4 |

|

|

|

& |

|

|

4 |

|

. |

|

|

|

|

3 |

|

|

. |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

8 |

|

. |

|

|

|

|

|

|

|

|

|

||

|

|

& |

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

Преобразователь кода |

|

||

|

1 |

|

|

|

|

a |

|

|

|

X/Y |

a |

|

g |

|

b |

|

|

|

|

|

|

|

|

|||

|

|

|

b |

|

|

|

||

|

2 |

|

|

|

|

|

|

|

|

|

c |

|

|

|

c |

|

|

|

|

|

|

|

|

|

||

|

4 |

|

d |

|

|

|

d |

|

|

|

e |

|

f |

|

|

||

|

|

|

|

|

|

|||

|

8 |

|

f |

|

|

|

|

|

|

|

g |

|

|

|

e |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

93

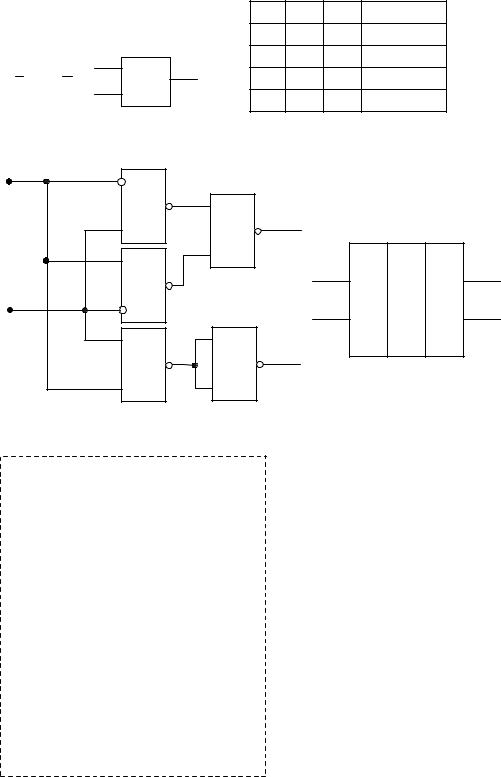

Сумматор

Сумматор - АЛУ, выполняющее функцию арифметического сложения. Простейший сумматор (полусумматор) выполняет сложение по модулю 2. Полусумматор формирует сумму двух чисел (А и В) и единицу переноса, которая подается в более старший разряд Сi. Следовательно, полный сумматор содержит вход для получения единицы переноса с младшего разряда, то есть происходит суммирование А и В с учетом Сi . Полный реализуется на двух сумматорах.

|

|

Сложение по |

А |

B |

S |

C i |

|

|

|

|

0 |

0 |

0 |

0 |

|

||

|

|

модулю 2 |

|

|||||

|

A |

m 2 |

S |

0 |

1 |

1 |

0 |

|

S = AB + AB |

B |

1 |

0 |

1 |

0 |

|

||

|

|

|

||||||

|

|

1 |

1 |

0 |

1 |

|

||

|

|

|

|

|

||||

|

Полусумматор |

|

|

|

Ci = A B |

|

||

A |

|

& |

|

|

|

|

|

|

|

|

|

|

& |

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

SM |

|

|

|

|

|

|

|

A |

S |

|

|

|

|

|

|

|

|

||

B |

|

|

|

|

|

|

B |

Ci+1 |

|

|

& |

|

& |

Ci + 1 |

|

||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Полный сумматор |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SM |

|

|

|

|

|

|

|

|

A |

|

|

SM |

|

S ' |

|

|

|

|

|

A |

S |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

A |

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

B |

|

|

|

|

|

|

|

|

|

B |

|

|

Ci+1 |

|

|

|

|

|

||||

B |

|

Cn+1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

C i |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C i |

A |

|

B |

S i |

C i+1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

||

|

|

|

|

SM |

|

|

|

|

|

|

S |

|

0 |

|

0 |

1 |

1 |

0 |

||||

|

|

|

A |

|

S |

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

1 |

1 |

0 |

1 |

|||||

C i |

|

|

|

|

Cn+1 |

S ' C |

|

1 |

|

i+1 |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

B |

|

|

|

|

0 |

0 |

1 |

0 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

1 |

|

0 |

1 |

0 |

1 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

||

94

Параллельный сумматор

B3 |

|

A3 |

|

B2 |

|

A2 |

|

B1 |

|

A1 |

|

B0 |

|

A0 |

|

|

|

|

|

|

|

C4 |

|

|

SM |

|

C3 |

|||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

S M |

|

|

|

|||

|

|

|

A 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

A1 |

|

|

|

S 0 |

|

|

|||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

A 2 |

|

|

|

S1 |

|

|

|||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

A 3 |

|

|

|

S 2 |

|

|

|||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

B |

0 |

|

|

|

S3 |

|

|

||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B1 |

|

|

|

C i+ 1 |

|

|

|||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

B2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

B 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

С i |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

SM |

|

C2 |

SM |

|

C1 |

SM |

|

C0 |

|||||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S2 |

|

|

S1 |

|

|

S0 |

||||||

|

|

|

|||||||||||

Параллельный сумматор обладает высоким быстродействием. Тактовые импульсы отсутствуют. При подаче данных на вход, на выходе с небольшой задержкой возникает сумма.

При суммировании большого количества разрядов целесообразно использовать последовательный сумматор.

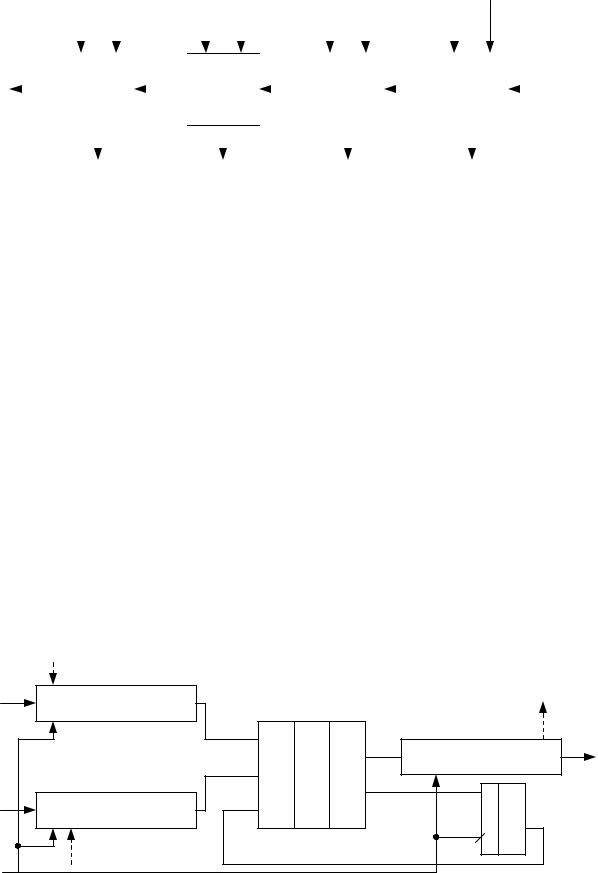

Последовательный сумматор

В таком устройстве происходит поразрядное суммирование от младшего к старшему разряду по переднему фронту синхроимпульса С. Ввод чисел А и В осуществляется в приёмные регистры сдвига (А, В) либо последовательно, либо параллельно.

Для каждого разряда сумма двух чисел записывается в регистр суммы, а единица переноса – в D – триггер, единица поступает на вход С i при суммировании каждого последующего разряда двух чисел происходит суммирование чисел А и В и единицы переноса от суммирования предыдущих разрядов. Для выполнения полного суммирования требуется m – тактовых импульсов синхронизации (m – число разрядов). Достоинство последовательного сумматора заключается в том, что его просто реализовать, он имеет мало входов, однако его быстродействие низко по сравнению с параллельным.

|

A |

|

|

|

|

|

A |

Регистр А |

|

|

|

|

|

|

|

|

|

S |

||

|

|

|

SM |

|

||

|

|

A |

|

S |

||

|

|

B |

S |

Регистр S |

||

|

|

C |

D |

T |

||

B |

|

C i |

||||

Регистр В |

i + 1 |

|||||

|

Q |

|||||

|

|

|

|

|

||

|

B |

|

|

C |

|

|

C |

|

|

|

|

||

|

|

|

|

|

||

95

Цифровой компаратор

Сравнивает два числа (А и В) представленных в двоичном коде.

А |

0 |

= = |

|

|

А |

1 |

|

|

|

А2 |

|

А>B |

|

|

|

||||

А3 |

|

|

|

|

В0 |

|

A=B |

|

|

|

||||

В |

1 |

|

|

|

В |

2 |

|

A<B |

|

В3 |

|

|

||

|

||||

А>B |

|

|

|

|

A=B |

|

|

|

|

A<B |

|

|

|

|

|

|

|

|

|

Функциональная схема сравнения одного разряда:

А 0110 |

|

& |

А>B |

|

|

|

0010 |

|

& |

1011 |

1 A=B |

|

|

1100 |

|

|

|

& |

|

|

|

A<B |

|

В 0101 |

|

|

0001 |

|

|

|

|

Построение многоразрядных компараторов |

|

||||

A>B |

Аn |

|

|

Аn-1 |

1 |

A>B |

|

|

|

|

|

||

|

& |

|

|

|

DD7 |

|

|

|

|

& |

|

||

|

A |

|

A |

|

||

|

DD2 |

A>B |

DD5 |

|

||

|

|

A>B |

|

|||

|

|

|

|

|

|

|

|

1 |

|

A=B |

1 |

A=B |

|

|

|

|

|

|||

|

DD1 |

|

DD4 |

|

||

|

|

|

|

|

||

|

|

|

|

A<B |

|

|

|

& |

|

A<B |

& |

|

|

|

B |

B |

|

|||

A<B |

|

|

DD6 |

|

||

DD3 |

|

|

1 |

A<B |

||

|

|

|

||||

|

|

|

|

|

DD8 |

|

|

|

|

|

|

|

|

|

Bn |

|

|

Bn-1 |

& |

A=B |

|

|

|

DD9 |

|||

|

|

|

|

|

|

|

Сравниваются вначале более старшие разряды. Если они неравны, то последующие разряды через схемы DD1-DD5 блокируются и в выходных схемах “ИЛИ” DD7-DD9 появляется соответствующий знак неравенства. Если старшие разряды равны, то блокировка снимается, и сравнение будет происходить до того более младшего неравенства, в котором эти неравенства выполняются.

В выходном устройстве DD7-DD9 формируется единица того знака неравенства, более старший разряд, которого больше.

Если А=В, то на выходах DD7, DD8 = 0, а на всех выходах А=В формируются единицы, которые собираются DD9.

96

Электронная память

Запоминающие устройства делят на оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ).

ОЗУ (основная память) выполняет запись, хранение и считывание произвольной двоичной информации. Обладает большим быстродействием. При снятии напряжения с микросхемы, информация, записанная в микросхему ОЗУ, теряется.

ПЗУ (микросхема постоянной памяти) осуществляет хранение и выдачу постоянно записанной информации, содержание которой в ходе работы системы не изменяется. Информация представляется в виде двоичных чисел, каждое из которых хранится в отдельной ячейке (ЯП). Микросхема ПЗУ имеет небольшой объём памяти, но однажды записанная в неё информация может храниться в ней достаточно долго. (Информация сохраняется при снятии напряжения питания с микросхемы ПЗУ). Периодически менять информацию позволяют РеПЗУ (репрограммируемые ПЗУ).

Основные параметры:

1.Информационная ёмкость (определяется числом ячеек памяти);

2.Структура МС памяти: поразрядная выборка (выборка одной ЯП), словарная выборка (байтовая) – за один такт считывается 4,8,16 ЯП. Ёмкость 4096 бит = 4 К: 4096 × 1, 1024 × 4, 256 × 16.

3.Быстродействие: время выборки равно разности

( t ВЫДАЧИ ИНФОРМ.- t СИГНАЛ ВЫБОРКИ АДР. ВХОД)

время цикла записи - считывания равно разности

( t СИГНАЛ ВЫБОРКИ ПРИ ЗАПИСИ - t СИГНАЛ ВЫБОРКИ ДЛЯ ЧТЕНИЯ).

4. Потребляемая мощность.

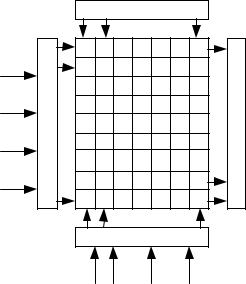

Структура памяти

Запись

А

д

ре А0 са А1

с А2 рт А3

о

к

А4 А5 А6 А7

Адреса столбцов

Накопитель (матрица ЯП размерностью n × m). Каждая ЯП подключена коллектор адресным (АШ) и разрядным (РШ) шинам. Шина – это системная магистраль

Спередачи данных. Выбор необходи-

ч |

мой ЯП представляет собой комби- |

|

и |

нацию A 0..7. |

|

т |

m – разрядность адреса ёмкость |

|

ы |

N = 2 m. Буферы записи и считыва- |

|

в |

ния – регистры. |

|

а |

Статические МС ОЗУ (на ос- |

|

н |

||

нове статической ЯП, которая реа- |

илизована на ТТЛ).е

Динамические МС ОЗУ (на основе динамической ЯП, реализована на МДП - транзистор, как и в электронной памяти паразитную емкость). Достоинство – занимает меньшую площадь на кристалле; недостаток – требование регенерации, так как емкость разряжается.

97

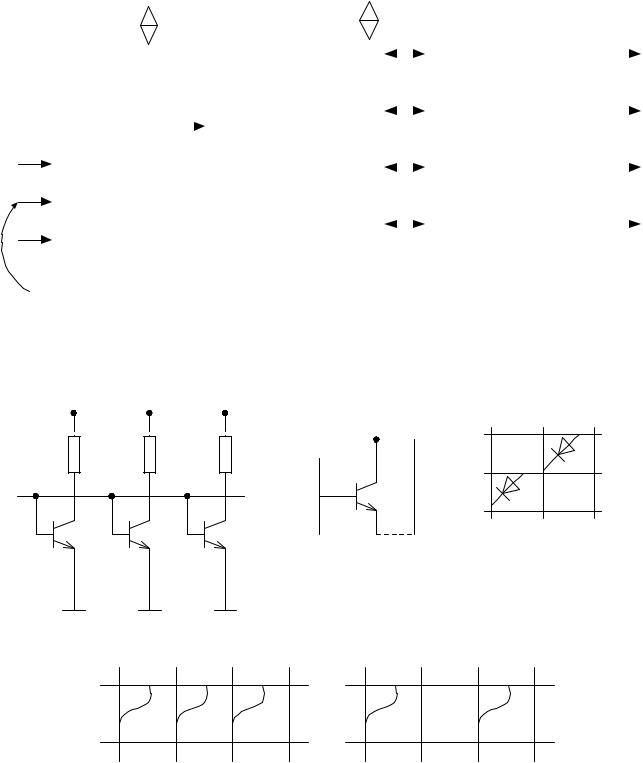

A0 |

RAM |

|

|

|

|

A0 |

RAM |

|

|

|

|

|

A0 |

PROM |

|

|

|||

A |

|

|

|

|

|

A |

|

|

|

|

|

|

A |

|

|

|

|

|

|

. 1 |

|

|

|

|

. 1 |

|

DIO |

|

|

|

. |

1 |

|

DO |

|

||||

. |

|

|

|

|

. |

|

|

|

0 |

|

. |

|

|

|

0 |

|

|||

. |

|

|

|

|

. |

|

|

DIO |

|

|

|

|

|

|

DO1 |

|

|||

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

||||||

A7 |

|

D0 |

|

|

|

A7 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

DIO |

|

|

|

|

A9 |

|

DO2 |

|

||

DI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

OE |

|

|

|

|

|||||||||||

|

|

|

|

|

2 |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

CS |

|

DIO |

|

|

CS1 |

|

DO3 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

WR/ |

|

|

|

|

WR/ |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

3 |

|

|

CS2 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

RD |

|

|

|

|

|

RD |

|

|

|

|

|

|

|

||||||

Выбор микросхем

Chip select

ПЗУ

Программируемые изготовителем: создается фотошаблон, на который затем напыляют диоды и транзисторы.

U n |

0 |

1 |

|

||

|

1 |

0 |

АШ РШ

Программируемые пользователем: (Используются плавкие перемычки.)

1 |

1 |

1 |

1 |

0 |

1 |

98

Репрограммируемые ПЗУ

|

|

|

|

|

|

|

|

SiO2 |

Используется структура Металл – |

|||||

|

|

|

|

|

|

|

|

нитрид – окисел – полупроводник (МНОП). |

||||||

|

С |

|

|

|

|

|

Программирование: U ИС ≈ 15..20 В, при ко- |

|||||||

|

|

Металл |

|

|

|

И |

||||||||

|

|

|

|

|

тором происходит пробой стокового p–n |

|||||||||

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

перехода. Электрическое поле в p - n пере- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ходе ускоряет дырки, которые через тонкий |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

слой диэлектрика (окисел SiO2) попадает на |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n + |

|

|

|

|

|

n+ |

|

|||||

|

|

|

|

p |

|

|

|

«плавающий» затвор (М). На нем накапли- |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

вается положительный заряд, который соз- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

дает n – канал. Так как затвор изолирован, |

|

|

|

|

|

подложка |

|||||||||

|

|

|

|

|

то заряд (и канал) существует долго. Сти- |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

рают ультрафиолетовыми лучами. В окисе- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ле (SiO2) образуются электронно - дыроч- |

ные пары. Электроны попадают на затвор и нейтрализуют заряд. Наличие затвора эквивалентно наличию перемычки.

99

Электронные генераторы

Электронные генераторы служат получения напряжения (тока) заданной формы, частоты, скважности и амплитуды.

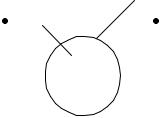

Генераторы

Синусоидальных (гармонических) колебаний Импульсные

К

К

X

K K X = 1 − XK

Электронные генераторы выполняют на базе усилителя с положительной обратной связью (П.О.С.)

Для самовозбуждения любого генератора необходимо выполнение двух условий: 1. баланс фаз

ϕ y + ϕ x = 2π n, n = 0,1,2...

ϕy − поворотфазысигнала усилителя;

ϕx − поворотфазыцепьюобратнойсвязи.

2. баланс амплитуд X K ≥ 1

Баланс фаз физически отражает П.О.С.

Баланс амплитуд показывает, что сигналы на входе и выходе усилителя соответствуют установившимся значениям.

XK > 1 |

|

Возбуждениегенратора |

XK = 1 |

100

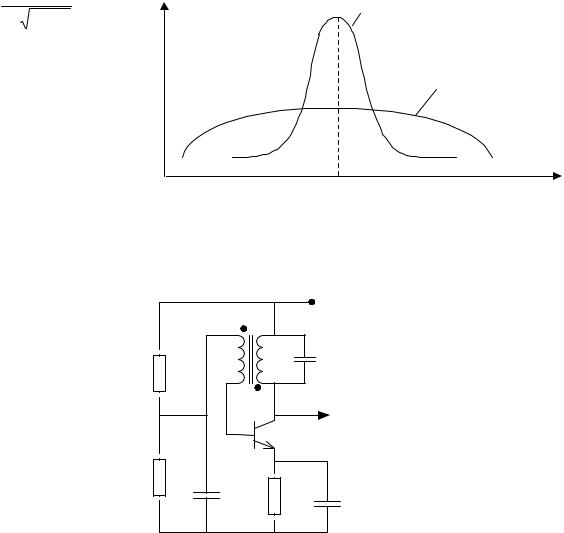

Генераторы синусоидальных (гармонических) колебаний

Для того, чтобы на выходе был сигнал определённой частоты ƒ0 , нужно сделать П.О.С. частотно – зависимой (избирательные RC – LС – цепи).

LC – высококачественные (ƒ0 >100 кГц), RC – низкокачественные (до единиц Гц).

LC – генераторы

Все LC – генераторы реализуются на резонансных усилителях, в которых выполняются условия баланса фаз и баланса амплитуд. В качестве избирательной цепи используется параллельный LC – контур.

Избирательный усилитель (LК CК - контур) пропускает только частоту

f0 = |

1 |

|

К |

|

К |

|

LKCK |

|

|

|

|||

2π |

|

|

|

|

||

Усилитель повора- |

|

|

|

|

|

|

чивает фазу на 180° |

|

|

|

X |

|

|

ϕ y = 180° . Обмотки |

|

|

|

|

|

|

LOC иLK включены |

|

|

|

|

|

|

встречно, следовательно, |

|

|

|

|

|

|

ϕ x = 180° , Σ |

=360°, то есть |

|

|

|

|

|

баланс фаз выполняется. X |

|

|

|

f 0 |

f |

|

определяется коэффициен- |

|

|

|

|||

|

|

|

|

|

||

том трансформации. KX > |

|

|

|

|

|

|

1 только на частоте ƒ0. СБЛОК – шунтирует сопротивление R2 по переменному току. Недос- |

||||||

татком такого генератора является то, что его структура содержит две обмотки. |

|

|||||

|

|

|

|

|

+ EП |

|

|

|

|

|

LOC |

CК |

|

|

|

R1 |

|

LK |

|

|

|

|

|

|

|

|

|

|

|

|

|

VT1 |

|

|

|

|

R2 |

CБ |

RЭ |

CЭ |

|

|

|

|

|

|||

|

|

|

|

|

||