- •2.1. Лабораторна робота №1

- •2.1.1.Мета роботи

- •2.1.2.Теоретичні відомості

- •2.1.3. Підготовка до роботи

- •2.1.4. Порядок виконання роботи

- •2.1.6. Контрольні запитання

- •2.2. Лабораторна робота № 2

- •2.2.1. Мета роботи

- •2.2.2.Теоретичні відомості

- •2.2.3. Підготовка до роботи.

- •2.2.4. Виконання роботи.

- •2.2.6. Контрольні запитання

- •2.3. Лабораторна робота № 3

- •2.3.1. Мета роботи

- •2.3.2. Теоретичні відомості

- •2.3.3. Підготовка до роботи.

- •2.3.4. Виконання роботи.

- •2.3.6. Контрольні запитання

- •2.4. Лабораторна робота № 4

- •2.4.1. Мета роботи

- •2.4.2. Теоретичні відомості

- •2.4.3. Підготовка до роботи.

- •2.4.4. Виконання роботи.

- •2.4.6. Контрольні запитання

- •2.5. Лабораторна робота № 5

- •2.5.1. Мета роботи

- •2.5.2. Теоретичні відомості

- •2.5.3. Підготовка до роботи.

- •2.5.4. Виконання роботи.

- •2.5.6. Контрольні запитання

- •2.6. Лабораторна робота № 6

- •2.6.1. Мета роботи

- •2.6.2. Теоретичні відомості

- •2.6.3. Підготовка до роботи

- •2.6.4. Виконання роботи

- •2.6.6. Контрольні запитання:

- •2.7. Лабораторна робота №7

- •2.7.1. Мета роботи

- •2.7.2. Теоретичні відомості

- •2.7.3. Підготовка до роботи

- •2.7.4. Виконання роботи

- •2.7..6. Контрольні запитання

- •2.8.Лабораторна робота №8

- •2.8.1. Мета роботи

- •2.8.2. Теоретичні відомості

- •2.8.3. Підготовка до роботи

- •2.8.4. Виконання роботи

- •2.8.6. Контрольні запитання

- •2.9. Лабораторна робота №9.

- •2.9.1. Мета роботи

- •2.9.2. Теоретичні відомості

- •2.9.3. Підготовка до роботи

- •2.9.4. Виконання роботи

- •2.9.6. Контрольні запитання

- •2.10. Лабораторна робота №10.

- •2.10.1. Мета роботи

- •2.10.2. Теоретичні відомості

- •2.10.3. Підготовка до роботи

- •2.10.4. Виконання роботи

- •2.10.6. Контрольні запитання

2.10. Лабораторна робота №10.

Дослідження послідовного порту ОМК MCS-51.

2.10.1. Мета роботи

Опанування основних принципів програмування послідовної передачі данихза допомогою прийомо-передавача MCS-51.

2.10.2. Теоретичні відомості

При синхронній послідовній передачі даних (наприклад, у випадку інтерфейсу SPI або шини I2С) синхронізується передача окремих бітів даних з допомогою одночасної передачі передавачем тактового сигналу. При цьому особливих вимог до такого тактового сигналу у відношенні синхронізації не висувають. Так, наприклад, при використанні декількох синхронних протоколів передачі такт для узгодження повільніших пристроїв, які підключені до шини, розтягується в часі.

Синхронна послідовна передача даних застосовується, головним чином, на рівні друкованих плат, в тому числі – для обміну даними між різними інтегрованими блоками у складі схеми мікроконтролера і різними периферійними пристроями (наприклад, для обробки відеосигналу або управління звуком через шину І2С телевізійного приймача).

На відміну синхронній передачі, при асинхронній передачі даних тактовий сигнал не передається. Це висуває жорсткі вимоги до розподілу інтервалів часу в каналах передачі і прийому. По цій причині часова розгортка для систем передачі даних, що працюють в асинхронному режимі, у більшості випадків містить кварцову стабілізацію.

Головною особливістю застосування асинхронної передачі даних, як правило, являється не обмін даними у складі схеми, а комунікація між блоками, які розділені у просторі і володіють ознаками власного інтелекту. В якості прикладу можна назвати зв’язок між персональним комп’ютером і принтером, модемом, програмованим пристроєм або реєстратором даних. Оскільки асинхронна передача даних може здійснюватися на великих відстанях аж до декількох сотень метрів, її протоколи не передбачають рівнів TTL, що є нестійкими до завад.

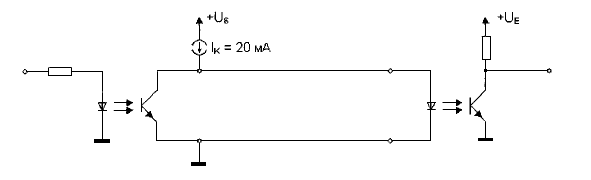

Серед поширених стандартів асинхронної передачі даних стійкістю до завад відрізняється струмовий інтерфейс з силою струму 20 мА, який може застосовуватися для асинхронної передачі даних зі швидкістю до 9600 бод. Цей інтерфейс не нормований, але завдяки простоті широко використовується протягом багатьох років.

З’єднання двох пристроїв здійснюється через замкнений прийомо-передаючий контур. На активній стороні протікає струм з силою 20 мА. Для передачі сигналів низького рівня підведення струму припиняється, а при передачі сигналу високого рівня контур залишається замкненим.

У випадку струмових інтерфейсів можливо легко реалізувати розподіл потенціалів між передаючою і приймаючою стороною через оптоелектронний пристрій, як зображено на рис. 2.36, тому вони придатні для передачі даних на відстань до 1000 м.

Рис.2.36. Приклад

передаючого контуру для струмового

інтерфейсу.

Рис.2.36. Приклад

передаючого контуру для струмового

інтерфейсу.

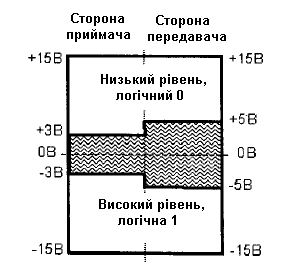

Широко розповсюджені інтерфейси RS232C або V.24 передають сигнали високого і низького рівня як значення напруги. При цьому на стороні приймача високому рівню TTL сигнала (+2 ÷ +5 В) виділений діапазон напруги -3В ÷ -15В, а низькому TTL сигналу (0 ÷ +0,8 В) – діапазон напруг +3 ÷ +15 В. На стороні передавача нижня границя для компенсації втрат напруги в лінії підтягнута до +5 В і відповідно -5 В. На рис.2.37 зображені рівні сигналу, що допускається нормами.

Для перетворення рівнів від стандарту TTL до стандартуіV.24 можна використати цілий ряд інтегральних схем. Найбільш поширеним драйверним модулем для цієї цілі являється мікросхема MAX232 компанії Maxim, яка завдяки вбудованим перетворювачам напруги використовує єдиний вид робочої напруги +5 В.

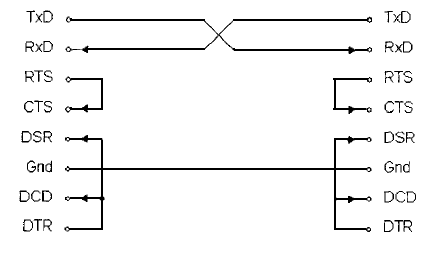

Для формування з’єднання з квитіруванням стандарт також передбачає деякі керуючі сигнали, які не є обов‛язковими. Разом з тим лінії цих сигналів не повинні залишатися не підключеними, оскільки це може привести до помилкової інтерпретації у протоколі.

Рис.2.37. Рівні напруг у відповідності до стандарту RS232C.

В найпростішому випадку для комунікації між двома пристроями достатньо мати просте з’єднання за допомогою трьох провідників: перехрещені передаючий і приймаючий провідники TxD і RxD, а також провідник заземлення. Не задіяні керуючі лінії інтерфейсу можуть бути замкнені у відповідності до рис.2.37.

На практиці, по інтерфейсу RS232C не можливо досягнути швидкості передачі даних вище 19200 бод. Внаслідок гальванічного з’єднання і виникаючих порушень у роботі, що обумовлені струмами перехідних процесів у проводі заземлення, передачу даних на відстані більше 15-20 метрів здійснити неможливо, хоча стандарт і визначає допустиму межу в 30,5 м.

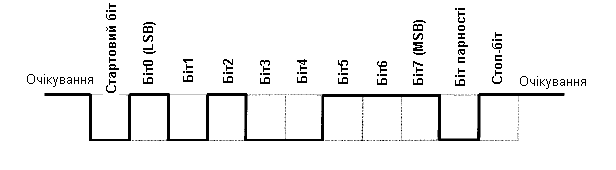

У відповідності до стандарту V.24, в лінії передачі даних у стані очікування встановлена логічна 1. Передача може бути розпочата у будь-який момент часу. Для того, щоб передати приймачу повідомлення про початок передачі, посилається стартовий біт з рівнем логічного 0. після цього слідують розряди даних (у більшості випадків 7 або 8, їх число призначається у протоколі передачі даних), при цьому спочатку передається молодший біт.

Для підвищення надійності передачі даних може бути добавлений біт парності. Біт парності доповнює розряди даних таким чином , що досягається пряма парність (сума усіх бітів, в тому числі біт

Рис.2.37. Просте три провідне з’єднання двох пристроїв.

парності, парна) або непряма парність (сума усіх бітів, в тому числі біт парності, непарна). Необхідний вид парності (відсутність, пряма, непряма) також повинен бути оголошений у протоколі передачі даних.

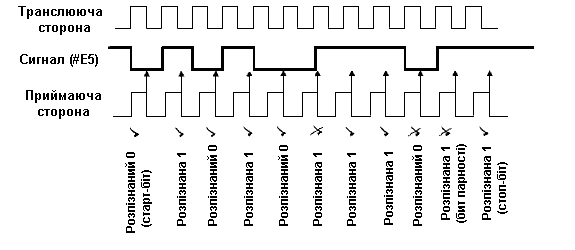

Передача закінчується стоп-бітом з рівнем логічної 1, який в деяких мікроконтролерах може бути запрограмований з тривалістю 1; 1,5 або 2 тривалості біта. Після відправлення стоп-біта лінія даних знову переходить у вихідний стан очікування і готова до наступної передачі. Часова діаграма передачі байта #Е5 (11100101b) з непрямою парністю і стоп-бітом через інтерфейс типу V.24 наведена на рис. 2.38.

Рис.2.38. Часова діаграма передачі байта #Е5 (11100101b) з непрямою парністю і стоп-бітом через інтерфейс типу V.24.

У зв’язку з тим, що тактовий імпульс для синхронізації передачі не пересилається, початок розряду може бути розпізнаний тільки за допомогою вимірювання часу, який пройшов з моменту появи спадаючого фронту стартового біта. Саме для цього потрібно встановлювати швидкість передачі даних, яка являється обов’язковою для передаючої і приймаючої сторони. Ці швидкості визначені в стандарті інтерфейсу RS232C і для уникнення помилок при розпізнаванні окремих розрядів їх необхідно дотримуватися.

Внаслідок суттєвої різниці між тактами передачі і прийому, а також у випадку, коли передача здійснюється по наростаючому фронту такту, а опитування на стороні приймача – по спадаючому, який може попадати в середину імпульсу даних наведені на рис.2.39.

На рис.2.39 зображений випадок, коли розряд 4 і розряд 7, а також біт парності розпізнані не правильно. Оскільки, в цьому прикладі оголошена непряма парність, то помилка може бути помічена за допомогою біта парності, так як байт розпізнаний як #75 і встановлений біт парності дають в результаті пряму парність, але при виникненні двох помилок біт парності про це не просигналізував би.

Відмінність у тактах на транслюючій та приймаючій стороні в розглянутому прикладі складає 20%, що не допускається. Для уникнення помилок і для забезпечення надійної передачі даних слід уникати відхилень, що перевищують 3%.

Послідовний порт може працювати в чотирьох режимах.

Режим 0. 8 бітів даних (LSD перший). Швидкість передачі фіксована (1/12 частоти генератора fosc).

Режим 1. 10 бітів передаються/приймаються: старт-біт (0), 8-бітів даних (LSB перший) і стоп-біт. При прийомі стоп-біт переміщується в RB8 регістра SCON. Швидкість передачі змінна.

Режим 2. Передача/прийом здійснюється 11-бітним словом: старт-біт (0), 8 бітів даних, програмований 9-ий біт (біт парності) і стоп-біт. При передачі 9-ий біт даних (TB8 в SCON) може містити „0” або „1”.

При прийомі, 9-ий біт прямує в RB8 регістра SCON. Швидкість передачі 1/32 або 1/64 частоти генератора.

Режим 3. Передача/прийом здійснюється 11-бітним словом. Режим 3 аналогічний режиму 2 лише швидкість передачі даних є зміна.

Рис.2.39.

Вплив різних тактів передачі на

транслюючій

Рис.2.39.

Вплив різних тактів передачі на

транслюючій

і приймаючій стороні.

Для роботи з послідовним портом виділено два регістри: SCON (Serial Port Control Register) – призначений для управління функціями прийомопередавача та регістр даних; SBUF (Serial Data Buffer) – регістр даних, фізично складається з двох регістрів (звернення до цих регістрів відбувається за однією адресою, причому один з них використовується для передачі, а інший – для прийому даних).

Мультипроцесорний зв’язок. Режим 2 і 3 має спеціальне забезпечення для мультипроцесорного зв’язку. В цьому режимі приймається 9 бітів даних, 9-ий біт надходить в RB8. Порт може бути запрограмований так, що коли отриманий стоп-біт, то переривання від послідовного порту буде активоване якщо RB8=1 (SM2=1). Цей режим надає можливість передачі

даних між декількома пристроями.

Прийом в режимі 0 призначається умовою RI=0 і REN=1, прийом, що уведений в інші режими прийнятим стартовим бітом якщо REN=1.

На рис.2.40 наведена структура регістра конфігурації послідовного порту, а в таблиці 2.20. – призначення його окремих бітів.

SM0 |

SM1 |

SM2 |

REN |

TB8 |

RB8 |

TI |

RI |

Рис.2.40. Регістр конфігурації SCON.

Таблиця 2.20. Призначення бітів послідовного порту MCS-51

Позначення |

Призначення |

SM0 |

Визначає режим роботи послідовного порту. |

SM1 |

Визначає режим роботи послідовного порту. |

SM2 |

Визначає режим мультипроцесорного зв’язку в режимі 2 і 3. В режимі 2 чи 3, якщо SM2 встановлений в 1, то RI не буде активований, якщо отриманий 9-ий біт даних (RB8) нульовий. В режимі 1, якщо SM2=1, то RI не буде активований, якщо не був отриманий коректний стоповий біт. В режимі 0, біт SM2 повинен бути встановлений в „0”. |

REN |

Встановлюється програмно для дозволу або заборони прийому. |

TB8 |

9-ий біт (біт парності), що може передаватися в режимах 2 і 3. встановлюється програмно. |

RB8 |

В режимах 2 і 3, 9-ий біт (біт парності), що може бути прийнятий. В режимі 1, якщо SM2=0, RB8 – стоповий біт, який був отриманий. |

TI |

Біт закінчення передачі. Встановлюється апаратно в кінці 8-го біта в режимі 0 чи на початку стоп-біта в інших режимах. Очищається програмно. |

RI |

Біт закінчення прийому. Встановлюється апаратно в кінці 8-го біта в режимі 0 чи на початку стоп-біта в інших режимах. Очищається програмно. |

Біти SM0 та SM1 визначають режими роботи інтерфейсу у відповідності з таблицею 2.21.

Таблиця 2.21. Вибір режимів роботи послідовного порту.

SM0 |

SM1 |

Режим |

Опис |

Швидкість пердачі (Бод рейт) |

0 |

0 |

0 |

Shift Register |

Фіксована (fosc/12) |

0 |

1 |

1 |

8-bit UART |

Змінна (встановлюється таймером) |

1 |

0 |

2 |

9-bit UART |

Фіксована (fosc/64 або fosc/32) |

1 |

1 |

3 |

9-bit UART |

Змінна (встановлюється таймером) |

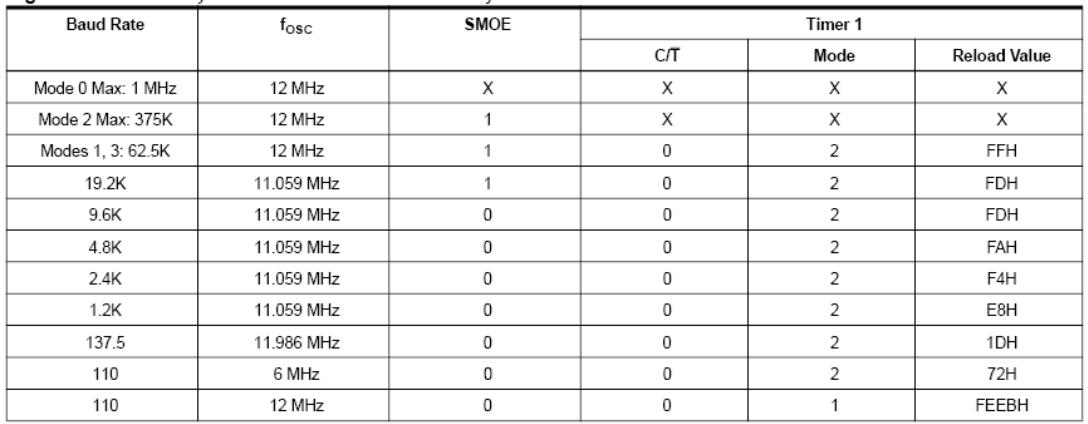

Бод рейт (Baud Rates)

В режимі 0 бод рейт фіксований і визначається наступною формулою

![]()

В режимі 2 бод рейт визначається бітом SMOD регістра РCON. Якщо SMOD=0 (значення за замовчуванням) бод рейт дорівнює 1/64 частоти генератора, як показано нижче

![]()

В AT89C51 переповнення таймера1 (Timer1) визначає бод рейт при використанні режимів 1 та 3.

Використання таймера1 для генерування бод рейту полягає в наступному. Коли таймер (Timer1) визначає (задає) бод рейт для режимів 1 та 3, то він визначається переповненням таймера і значенням SMOD:

![]()

Для цого режиму повинно бути встановлено переривання від таймера (Timer1). Для найбільш поширеного випадку (при наступних настроюваннях TMOD=0010b) швидкість передачі визначається наступною формулою

![]()

Таблиця 2.22. Значення бод-рейту, що формуються таймером.

За допомогою таймера1 можна досягти дуже низької швидкості передачі, якщо його сконфігурувати як 16-бітний (TMOD=0001b). В таблиці 2.22. наведені значення бод рейту і як вони можуть бути отримані за допомогою таймера.

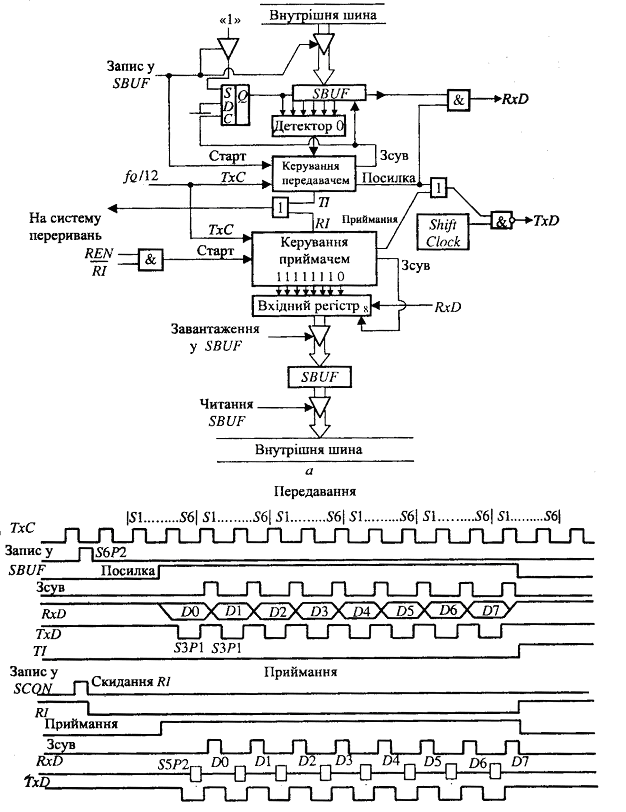

У режимі 0 послідовний порт являє собою 8-розрядний регістр зсуву. Байт інформації передається через вивід RxD, при цьому через вивід TxD видаються сигнали синхронізації зсуву. Приймання і видача байта починається з молодшого розряду і закінчується старшим. Швидкість обміну фіксована і дорівнює 1/12 частоти синхронізації ОМК.

Передавання починається з будь-якої команди, яка використовує буфер приймача-передавача SBUF як регістр призначення, наприклад MOV SBUF, A( Рис.2.41).

У фазі Р2 стану S6 (S6P2) пристрій керування за сигналом «Запис у SBUF» записує байт у peгicтp зсуву передавача, встановлює D-тригер дев'ятого біта в одиницю та ініціює роботу блока керування передавачем. Останній через один машинний цикл формує сигнал дозволу «Посилка», який дозволяє видачу вмісту регістра зсуву передавача на вивід RxD та сигналу «Синхронізація зсуву» на вивід TxD. За сигналом «Зсув» у момент S6P2 кожного машинного циклу вміст peгicтpa зсуву передавача зсувається праворуч на одну позицію молодшими бітами вперед і надходить на bивід RxD. У старші біти peгicтpa зсуву передавача, що звільняються, записуються нулі.

При отриманні від детектора нуля сигналу „Передавач звільнений” блок керування передавачем знімає сигнал «Посилка» i встановлює біт переривання передавача ТІ на початку інтервалу S1P1 десятого машинного циклу після надходження сигналу «Запис у SBUF».

Приймання починається при одночасному виконанні умов REN=1 і RI = 0. На початку інтервалу S6P2 наступного машинного циклу (рис. 7) блок керування приймачем формує сигнал дозволу «Приймання», за яким на вивід TxD передаються синхросигнали зсуву, i в peгістрі зсуву приймача починають формуватися значення бітів даних, які зчитуються з виводу RxD в інтервалі S5P2 кожного машинного циклу. В інтервалі S6P2 кожного машинного циклу за сигналом «Зсув» здійснюється зсув вмісту регістра зсуву приймача ліворуч на одну позицію, i прийнятий біт записується у крайній правий розряд. Після надходження восьмого імпульсу «Зсув» вміст

Рис.2.41. Послідовний порт в режимі 0: а) функціональна схема; б) часові діаграми обміну.

peгістрa приймача переписується у SBUF. В інтервалі S1P1 десятого машинного циклу блок керування приймачем переписує вміст регістра зсуву в буфер SBUF, знімає сигнал «Приймання» та встановлює біт переривання приймача RI в одиницю.

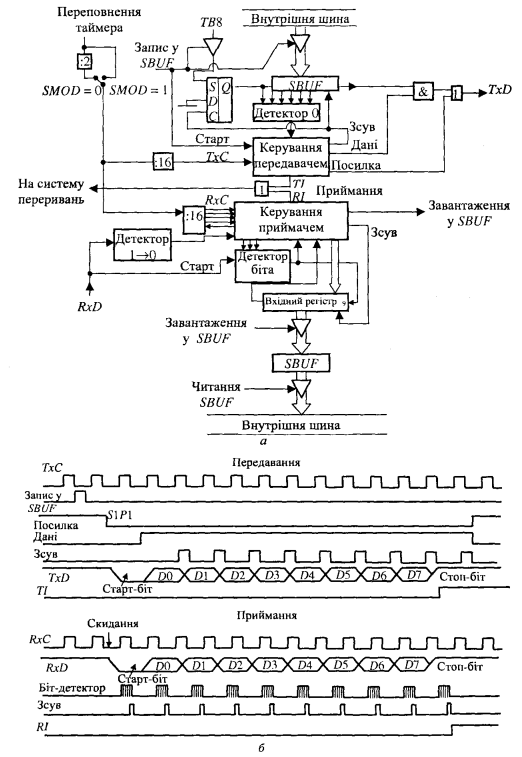

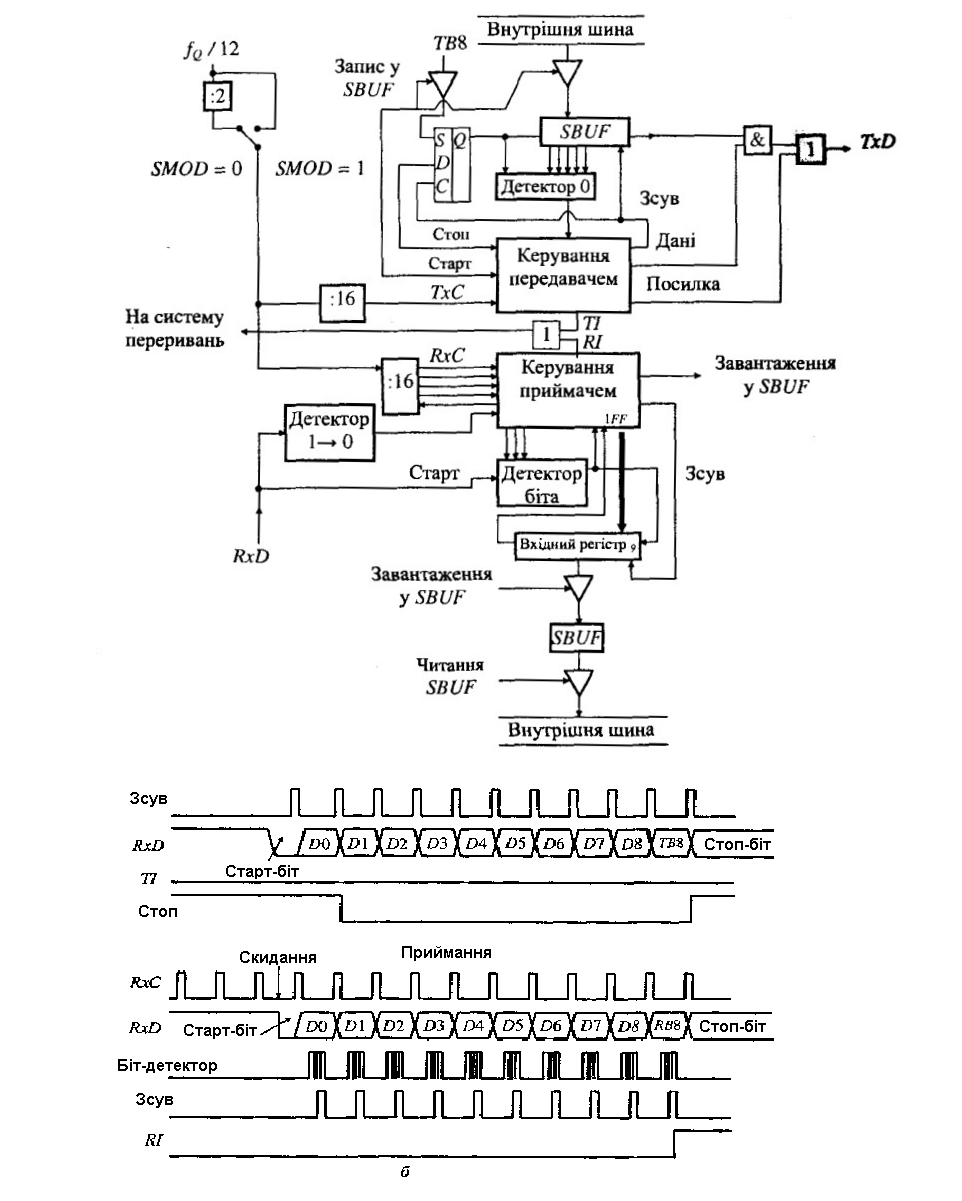

У режимі 1 послідовний порт являє собою 8-розрядний універсальний асинхронний приймач-передавач зі змінною швидкістю обміну. Через TxD передаються, а через RxD приймаються 10 біт: нульовий старт-біт, 8 біт інформації та одиничний стоп-біт. Швидкість обміну є змінною. Вона визначається частотою переповнення таймера 1 і бітом SMOD регістра PCON. На рис. 2.42 показано функціональну схему i діаграми послідовного порту в режимі 1.

Передавання починається з будь-якої команди, що використовує SBUF як peгicтp призначення, наприклад:

MOV SBUF, #25; переслати в SBUF число 25

Пристрій керування ОМК за сигналом «Запис у SBUF» завантажує 1 у дев'ятий біт регістра зсуву передавача, ініціює роботу блока керування передавачем i в інтервалі S1Р1 формує сигнал дозволу «Посилка» низького рівня. За цим сигналом на вивід TxD спочатку надходить старт-біт, а потам за сигналом дозволу «Дані» та імпульсами «Зсув» вміст регістра передавача зсувається на одну позицію, i на вивід TxD по черзі надходять 8 біт даних. За дев'ятим імпульсом «Зсув» формується одиничний стоп-біт, біт ТІ встановлюється в нуль, сигнали «Посилка» i «Дані» знімаються, i обмін закінчується.

Приймання починається при переході сигналу на вході RxD з одиниці в нуль, який виявляється за допомогою детектора спадання. Як тільки перехід з одиниці в нуль виявлений, у регістр зсуву приймача завантажується число 1FFH, тобто всі 9 розрядів регістра заповнюються одиницями. При переході сигналу на вході RxD з одиниці в нуль також скидається значення внутрішнього лічильника-подільника частота на 16, який формує сигнал «Синхронізація приймача». Внутрішній лічильник починає відраховувати імпульси синхронізації. Під час сьомого, восьмого та дев'ятого імпульсів здійснюється опитування сигналу на вході RxD для підтвердження нульового значення старт-біта. Отримані три значення прийнятого біта надходять на детектор біта, який визначає дійсне значення прийнятого біта за мажоритарним принципом «два з трьох». У тому випадку, якщо дійсне значення старт-біта дорівнює нулю, починається приймання по черзі 8 біт даних. Значення кожного біта даних також перевіряється детектором біта в сьомому, восьмому та дев'ятому імпульсах сигналу «Синхронізація приймача» i лише після цього заноситься в регістр зсуву приймача. Якщо значення старт-біта не дорівнює нулю, то блок керування прийманням знову починає пошук переходів сигналу на вході RxD з одиниці в нуль.

Р ис.2.42.

Послідовний порт в режимі 1: а)

функціональна схема;

ис.2.42.

Послідовний порт в режимі 1: а)

функціональна схема;

б) часові діаграми обміну.

Приймання старт-біта та 8 біт даних у кожному машинному циклі супроводжується зсувом вмісту регістра приймача на одну позицію за сигналом «Зсув». Після прийняття старт-біта та 8 біт даних приймається стоп-біт, значення якого обов'язково має бути одиничним. Отже, після десятого імпульсу «Зсув» у регістрі приймача знаходяться 8 біт інформації i стоп-біт. Блок керування прийманням формує сигнал «Завантаження буфера», за яким вісім інформаційних бітів надходять у SBUF, стоп-біт - у розряд RB8 регістра SCON. Біт переривання приймача RI встановлюється в нуль. Приймання закінчується, i послідовний порт знову починає процес виявлення переходу сигналу на вході RxD з одиниці в нуль.

У режимах 2 i 3 послідовний порт являє собою 9-розрядний універсальний синхронний приймач-передавач із фіксованою (для режиму 2) та змінною (для режиму 3) швидкістю обміну. У режимі 2 швидкість обміну дорівнює fOSC/32 при SMOD = 1 або fOSC/64 при SMOD = 0. У режимі 3 швидкість обміну визначається таймером 1, як i в режимі 1.

На рис. 2.42.а) показано функціональну схему, а на рис. 2.42.б) - діаграми послідовного порту в режимі 2. Функціональна схема послідовного порту в режимі 3 збігається зі схемою на рис.2.41.а), а діаграми - з діаграмами на рис. 2.42.б).

Через вивід TxD послідовний порт передає або з виходу RxD приймає 11 біт: нульовий старт-біт, 8 біт даних, програмований дев'ятий біт TB8 та одиничний стоп-біт. Режими 2 i 3 відрізняються від режиму 1 лише наявністю дев'ятого програмованого біта. Внаслідок цього змінюються умови закінчення циклу приймання: блок керування прийманням формує сигнал керування «Завантаження буфера», завантажує стоп-біт у розряд RB8 регістра SCON i встановлює біт переривання приймача RI в одиницю лише в тому разі, якщо в останньому такті зсуву виконуються дві умови: RI = 0 та SM2 = 0 або значення дев'ятого прийнятого біта даних дорівнює одиниці.

Для демонстрації принципу керування обміном через послідовний порт розглянемо Рис.2.44., де представлена підпрограма здіснення обміну даними, що виводяться на лінійку світлодіодів для індикації.

Рис.2.43. Послідовний порт в режимі 2: а) функціональна схема;

б) часові діаграми обміну.

Приклад програми до лабораторної роботи.

P3 data 0B0h ;оголошення символічних імен та адрес

SCON data 098h ;регістр конфігурації послідовного порту

SBUF data 099h ;буфер послідовного порту

IE data 0A8h ;регістр дозволу переривань

IP data 0B8h ; регістр пріоритетів переривань

PCON data 087h ;

TCON data 088h ;регістр контролю переривань

TMOD data 089h ;регістр керування таймерами

TR1 bit TCON.6 ;біти використаних регістрів

TF1 bit TCON.7 ;

TL1 data 8Bh

TH1 data 8Dh

TI bit SCON.1

TB8 bit SCON.3

ORG 0

jmp start

start:

mov IE, #010000000b ;налаштування регістрів переривань

mov IP, #000000000b

mov SCON, #001000000b ;налаштування передачі в режимі 1

mov TH1, #248

mov R0, #000111111b ;в R0 заноситься число 3FH для передачі

mov PCON, #00b

mov TMOD, #000010000b ;налаштування Timer1

;в режим Auto-reload

mov A, #000000010b ;

mov DPTR, #0C000h ;переключення мультиплексора на порт Х12

movx @DPTR,A ;

mov A, R0

setb TR1 ;запуск Timer1

mov SBUF, A ;помістити вміст акумулятора в послідовний буфер

loop:

mov A, R0

mov A, #011b

mov DPTR, #0A004h

movx @DPTR, A

mov A, R0

mov DPTR, #0A001h

movx @DPTR, A

inc A

mov R0, A

jbc TI, rec ;перехід на мітку rec якщо TI=1

jmp loop

rec:

clr TR1 ;зупинка роботи Timer1

mov A, R0 ;

mov DPTR, #0A006h ;виведення нової посилки на світлодіоди

movx @DPTR, A

call ZAD

mov A, #0h ;

mov DPTR, #0A006h ;погашення світлодіодів

movx @DPTR, A ;

call zad

setb TR1 ;запуск роботи Timer1

mov A,R0

mov SBUF,A ;відправлення нової посилки в SBUF

jmp loop

ZAD: ;підпрограма затримки

mov R1,#0FFh

C2: mov R2,#0FFh

C4: djnz R2, C4

djnz R1, C2

ret

end

Рис. 2.44. Підпрограма керування обміном через послідовний порт.