- •Стандартні розміри системних плат

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Контрольні запитання

- •Практична робота №4 Опис найпростіших логічних схем на мові vhdl. Тріггери. Регістри. Лічильники.

- •Теоретичні відомості.

- •Variable список змінних;

- •Завдання до практичної роботи

- •Практична робота №5 Опис найпростіших логічних схем на мові vhdl. Мультиплексори, суматори, помножувачі.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №6 Побудова схем з пам'яттю. Ramb, srl, rom, fifo.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №7 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №8 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

Завдання до практичної роботи

Завдання: ознайомитися з теоретичними відомостями про запам'ятовуючі пристрої комп'ютера, визначити типи досліджуваних модулів пам'яті DRAM, встановити їх характеристики та способи організації, скласти звіт про виконання роботи.

Контрольні запитання

1. КЕШ-пам’ять в сучасних персональних комп’ютерах.

2. Типи організації динамічної оперативної пам'яті.

3. Оперативна пам’ять FPM, EDO і BEDO.

4. Модулі SІММ, DІММ та RІММ, їх характеристики.

5. Пам’ять DDR SDRAM.

6. Пам’ять QDR та QBM.

Практична робота №4 Опис найпростіших логічних схем на мові vhdl. Тріггери. Регістри. Лічильники.

Мета: ознайомитися з особливостями опису на мові VHDL тригерів, регістрів та лічильників.

Теоретичні відомості.

Для прикладу створимо в нашій ПЛІС один елемент - 16ти-розрядний лічильник, який буде враховувати імпульси по передньому фронту та мати два керуючих сигналу: скид і дозвіл роботи.

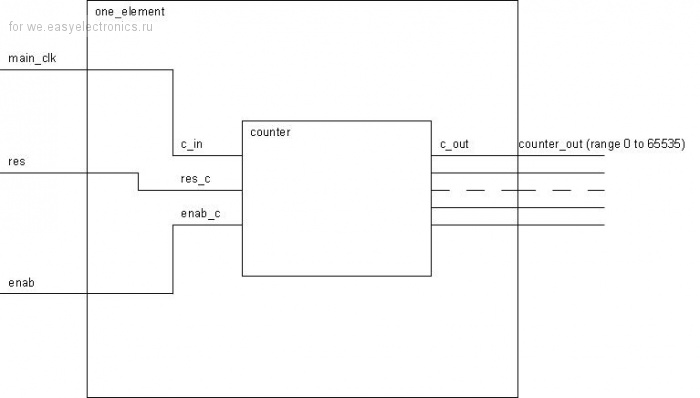

Щоб правильно описати наш елемент, треба добре уявляти його структуру. Для цього намалюємо таку картинку (рис. 4.1):

Рис. 4.1 Структура лічильника

Зовнішній квадрат (one_element) - це наша ПЛІС.

До неї зліва підходять 3 вхідних сигналу:

Main_clk - тактовий сигнал, за яким власне і працює наш лічильник,

Res - сигнал скидання лічильника в 0,

Enab - дозволяючий сигнал, наявність якого дозволяє роботу лічильника.

Праворуч вихідний сигнал розмірністю 16 біт (integer range 0 to 65535 дає нам 16 розрядів)

Це ті сигнали, які фізично приходитимуть безпосередньо на входи нашої ПЛІС.

Внутрішній квадрат (counter) це тіло нашого лічильника. До нього підходять ідентичні сигнали, але назви у них свої. Тому що в одній ПЛІС ми можемо створити безліч однакових лічильників, і щоб система знала, куди який зовнішній сигнал заводити, внутрішній елемент має власні назви сигналів.

Тепер, коли із загальною структурою елемента ясно запишемо все це за допомогою VHDL.

Крок 1. Включення в код використовуваних бібліотек.

Як і у всіх мовах програмування, в VHDL є стандартні бібліотеки.

library IEEE; use IEEE.std_logic_1164.all;

Дана бібліотека дає можливість привласнювати сигналам типу bit не тільки значення 0 і 1 але і ще 7 додаткових значень, включаючи Z-стан.

Крок 2. Опис точок входу і точок виходу пристрою.

В літературі це називається описом інтерфейсу.

Інтерфейс будь-якого елемента описується за допомогою ключового слова entity і являє собою наступну конструкцію:

entity им’я_елементу is

port (

список вхідних сигналів : in тип сигналів;

список вихідних сигналів : out тип сигналів

);

end им’я_елементу;

Так як, у відповідності зі структурою програми, в даному кроці ми описуємо інтерфейс всього пристрою, значить вхідними і вихідними сигналами у нас будуть всі лінії, що підходять до блоку «one_element» зображені на схемі. Запишемо їх на VHDL:

entity one_element is

port (

main_clk, res, enab: in bit;

counter_out: out integer range 0 to 65535

);

end one_element;

Крок 3. Опис точок входу і виходу елементів, що входять до пристрою.

Інтерфейс елементів входять до складу схеми описується аналогічно інтерфейсу всього пристрою.

ВАЖЛИВО: Якщо в схему входить кілька однотипних елементів (наприклад 2 однакових лічильника і 3 однакових регістра), то в даній частині програми ми описуємо по одному елементу кожного типу (в продовження прикладу - один лічильник і один регістр).

У нас в схемі лічильник тільки один, тому ми його і опишемо:

entity counter is

port (

c_in,enab_c,res_c:in bit;

c_out:out integer range 0 to 65535

);

end counter;

Крок 4. Опис архітектури елементів входять до пристрій.

Архітектура елементів описується за допомогою ключового слова «architecture» і являє собою конструкцію типу:

architecture им’я_архітектури of им’я_елементу is

begin

process(список запуску)