- •ТехничЕские требования

- •Содержание пояснительной записки

- •Анализ задания

- •1.1 Формирование кодовой таблицы и набора дискретных сигналов

- •1.2 Общая характеристика микроконтроллера ххххх

- •1.2.1 Организация памяти и программная модель

- •1.2.3 Таймеры/ счетчики

- •1.2.4 Система прерываний

- •1.3 Размещение кодовой таблицы сигналов в памяти

- •1.4 Порт вывода дискретных сигналов

- •1.5. Порядок работы генератора сигналов

- •Кодовая таблица символов

- •2 Разработка структурной схемы генератора сигналов

- •3 РазработкА функциональной схемы генератора сигналов

- •4 РазработкА принципиальной схемы генератора сигналов

- •Общие рекомендации

- •5 Разработка алгоритма работы и управляющей программы генератора

- •Загрузочный файл программы

- •Общие сведения

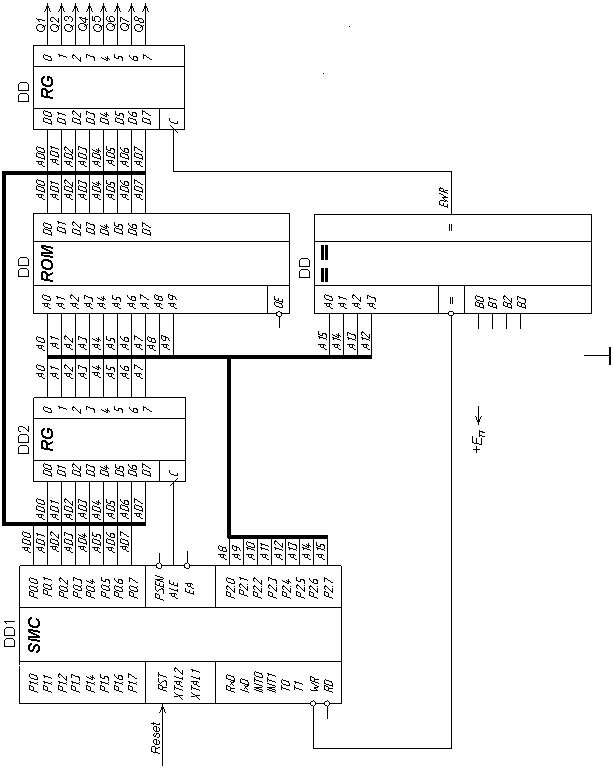

3 РазработкА функциональной схемы генератора сигналов

Схема электрическая функциональная выполняется на листе соответствующего формата в соответствии с требованиями ЕСКД.

Схема электрическая функциональная программируемого генератора сигналов приведена на чертеже ОМТ 10.ХХ.01 Э2.

Программируемый генератор сигналов разрабатывается на основе микроконтроллера Intel 80С31 (элемент DD1 функциональной схемы). Для индикации и управления режимами работы устройства используются внешние управляющие сигналы.

Перевод в режим «Сброс» производится сигналом «Reset», поступающим на вход RST микроконтроллера. Для индикации режима микроконтроллер формирует на линиях Р1.2 и Р1.3 сигналы «Сброс1» и «Сброс2» .

Для индикации режима «Ожидание» используется линия Р1.4.

По сигналу «Start» с логическим уровнем 0, подаваемому на линию Р1.1 микроконтроллера, начинается выдача дискретных сигналов Q1-Q8. Для индикации режима микроконтроллер формирует на линии Р1.5 сигнал «Пуск».

Восьмиразрядный параллельный регистр (элемент DD2) используется для демультиплексирования шины адреса/данных. Входы D0-D7 регистра подключены к выводам параллельного порта Р0. Запись в регистр младшего байта адреса внешней памяти AD0-ad7 производится по срезу сигнала ALE. Выходные линии А0-А7 регистра совместно с линиями А8-А15 параллельного порта Р2 образуют общую шестнадцатиразрядную шину адреса А0-А15.

В качестве внешней памяти используется параллельное ПЗУ объемом 64 Кбайта (элемент DD4). Для упрощения схемы генератора применяется способ совмещения ВПП и ВПД.

Адресное пространство младших адресов ПЗУ используется как память программ для размещения управляющей программы. Для разрешения обращения к ВПП на вывод EA^ микроконтроллера подается уровень логического нуля. Обращение к памяти программ сопровождается сигналом PSEN^.

Адреса с 9000h по 9007h используются как память данных и предназначены для хранения кодовой таблицы сигналов, чтение которой сопровождается сигналом RD^.

Формирование общего сигнала разрешения чтения внешней памяти производится логическим элементом DD3. На его входы подаются управляющие сигналы чтения внешней памяти данных RD^ и чтения внешней памяти программ PSEN^. С выхода элемента DD3 сигнал разрешения поступает на стробирующий вход OE^ элемента DD4.

Дешифрация адреса порта вывода дискретных сигналов производится при помощи устройства сравнения (элемент DD5). Поскольку любой адрес от AB00h до ABFFh является истинным, используется принцип частичной дешифрации.

Дешифратор производит сравнение сигналов на входах А и В по условию равенства. Восемь старших разрядов А8-А15 шины адреса подаются на входы А0-А7. На входах В0-В7 фиксируется число 1010 1011b. При совпадении сигналов на входах А и В и наличии на входе дешифратора сигнала WR^, схема сравнения формирует сигнал разрешения записи в порт вывода дискретных сигналов EWR.

Порт вывода дискретных сигналов реализован на основе восьмиразрядного параллельного регистра (элемент DD6). Входы D0-D7 регистра подключены к шине адреса/данных. По фронту сигнала EWR регистр считывает кодовые комбинации с шины и формирует выходные дискретные сигналы Q1-Q8.