- •ТехничЕские требования

- •Содержание пояснительной записки

- •Анализ задания

- •1.1 Формирование кодовой таблицы и набора дискретных сигналов

- •1.2 Общая характеристика микроконтроллера ххххх

- •1.2.1 Организация памяти и программная модель

- •1.2.3 Таймеры/ счетчики

- •1.2.4 Система прерываний

- •1.3 Размещение кодовой таблицы сигналов в памяти

- •1.4 Порт вывода дискретных сигналов

- •1.5. Порядок работы генератора сигналов

- •Кодовая таблица символов

- •2 Разработка структурной схемы генератора сигналов

- •3 РазработкА функциональной схемы генератора сигналов

- •4 РазработкА принципиальной схемы генератора сигналов

- •Общие рекомендации

- •5 Разработка алгоритма работы и управляющей программы генератора

- •Загрузочный файл программы

- •Общие сведения

2 Разработка структурной схемы генератора сигналов

В разделе «Разработка структурной схемы» необходимо привести подробное описание генератора сигналов на уровне структурных блоков и связей между ними.

Пример.

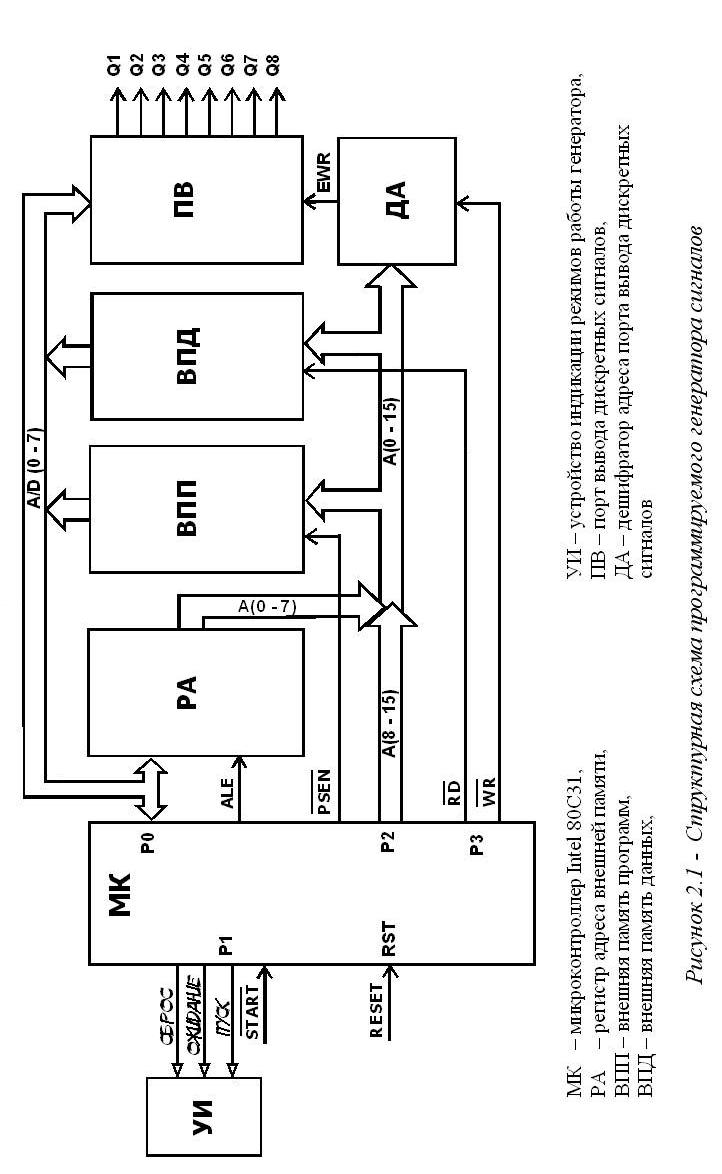

Структурная схема программируемого генератора сигналов приведена на рисунке 2.1.

Устройство разрабатывается на основе микроконтроллера Intel 80С31. При получении внешнего сигнала «Reset» генератор переводится в режим «Сброс». Микроконтроллер устанавливается в начальное состояние и начинает выполнять управляющую программу. Через 1,6 с генератор переходит в режим «Ожидание».

По внешнему сигналу «Start» с логическим уровнем 0 генератор переходит в режим «Пуск» и на выходах порта вывода дискретных сигналов начинается формирование сигналов Q1-Q8.

Отображение режимов работы генератора производится устройством индикации.

Внешняя память программ предназначена для хранения управляющей программы генератора. В зависимости от варианта задания ВПП также используется для хранения кодовой таблицы сигналов, формируемых генератором, или не используется.

Внешняя память данных предназначена для хранения по адресу 9000h кодовой таблицы сигналов, формируемых генератором. Или не используется (в зависимости от варианта задания).

В процессе работы микроконтроллер формирует следующие управляющие сигналы:

ALE (Address Latch Enable) – стробирование адреса внешней памяти,

WR^ (Write) – разрешение записи во внешнюю память данных,

PSEN^ (Program Store Enable) – разрешение чтения внешней памяти программ,

RD^ (Read) – разрешение чтения из внешней памяти данных.

Шина адреса А(0-15) используется для адресации внешней памяти и порта вывода дискретных сигналов.

Шина адреса/данных A/D(0-7) – используется при чтении внешней памяти и записи кодовых комбинаций в порт вывода дискретных сигналов.

Особенностью архитектуры микроконтроллера Intel 80С31 является использование мультиплексированной шины адреса/данных. Для её демультиплексирования предназначен регистр адреса внешней памяти.

В первой части машинного цикла на линии A/D(0-7) порта Р0 микроконтроллер выставляет младший байт адреса внешней памяти. Старший байт адреса внешней памяти выдается на линии А(8-15) порта Р2. По сигналу ALE младший байт адреса внешней памяти записывается в регистр, и хранится в течение всего машинного цикла. Сигналы А(0-7) с выхода регистра адреса и сигналы А(8-15) образуют общую шину адреса генератора А(0-15).

Во второй части машинного цикла микроконтроллер производит чтение внешней памяти или запись в порт вывода дискретных сигналов, что сопровождается соответствующими управляющими сигналами.

Дешифратор адреса порта вывода дискретных сигналов осуществляет выделение из адресного пространства диапазона AB00h-ABFFh. При наличии на входе дешифратора любого адреса из указанного диапазона, сопровождаемого сигналом записи WR^, формируется сигнал разрешения записи в порт вывода EWR.

Вывод: при разработке функциональной электрической схемы генератора сигналов, необходимо выбрать функциональную базу и технические решения для внешней памяти, порта вывода дискретных сигналов и дешифратора адреса, а так же схем индикации и управления режимами работы генератора.

Перед разработкой функциональной схемы генератора изучите архитектуру микроконтроллера, организацию его памяти и управляющие сигналы. Выберите место размещения управляющей программы, тип и объем внешней памяти, принцип дешифрации адреса порта вывода дискретного сигнала, определите линии параллельного порта Р1, использующиеся для управления режимами работы генератора и индикацией.

В таблице 3.1 приведены результаты, необходимые для разработки функциональной схемы (см. разделы 1 и 2 ПЗ). Таблица используется для текущей работы над схемой, и в пояснительной записке не приводится.

Исходные данные |

Результаты анализа |

Внешние управляющие сигналы Reset Start Сброс1 Сброс2 Ожидание Пуск |

п. 1.5 раздела 1 Выводы микроконтроллера: RST Р1.1 Р1.2 Р1.3 Р1.4 Р1.5 |

Место размещения управляющей программы, управляющий сигнал. |

п. 1.2 раздела 1 Микроконтроллер Intel 80С31 не имеет резидентной памяти программ, поэтому используется ВПП. Обращение к ВПП производится при условии, что на выводе EA^ микроконтроллера присутствует уровень логического 0. Управляющий сигнал - Psen^. |

Место размещения кодовой таблицы сигналов, тип и объем памяти, управляющий сигнал. |

п. 1.3. раздела 1 ВПД, всего 8 ячеек памяти, начиная с адреса 9000h по 9007h. Минимальный объем стандартного ПЗУ, содержащего указанный диапазон адресов – 64 Кбайта. Управляющий сигнал - RD^. |

Способ дешифрации адреса порта вывода дискретных сигналов, разрядность схемы сравнения, управляющие сигналы. |

п. 1.4. раздела 1 Адрес порта вывода задан от AB00h до ABFFh, что соответствует диапазону от 1010 1011 0000 0000b до 1010 1011 1111 1111b Следовательно, любой адрес, соответствующий маске 1010 1011 XXXX xxxxb принадлежит порту вывода. Поэтому восемь младших разрядов адреса, не имеющих определяющего значения, можно исключить и использовать принцип частичной дешифрации адреса по восьми старшим разрядам. Управляющие сигналы - WR^, EWR. |