3. Регистры

Регистрами называют функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации. В зависимости от способа записи информации (кода числа) различают параллельные, последовательные и параллельно - последовательные регистры.

Параллельные регистры.

В параллельных регистрах запись двоичного числа (слова) осуществляется параллельным кодом, т. е. во все разряды регистра одновременно. Их функция сводится только к приему, хранению и передаче информации (двоичного числа). В связи с этим параллельные регистры часто называют р е г истрами памяти.

Параллельный N-разрядный регистр состоит из N триггеров, каждый из которых имеет число входов, соответствующих количеству источников информации. Если источник цифровой информации один, то каждый триггер имеет один вход. При двух и трех параллельных каналах информации триггер разряда выполняется на два и три входа. Запись цифровой информации того или иного канала в регистр осуществляется по цепи управления регистром.

Принцип построения параллельных регистров иллюстрируется их структурной схемой (рис. 3.1) при одном канале четырехразрядной цифровой информации. Обозначения на рисунке: T1, — триггер младшего разряда; T4 — триггер старшего разряда; Э1 — Э4— элементы, предназначенные для управления записью информации в регистр; Э5 —Э8— элементы, служащие для управления считыванием информации из регистра.

Перед записью двоичного числа все триггеры устанавливают в состояние «0» подачей импульса по входу «Установка нуля». Для записи в регистр входной информации подают импульс записи, открывающий входные элементы И. Код входного числа записывается в регистр. Если, например, на входе присутствует код 1011, что соответствует числу 11, то это же число будет записано в регистр. По окончании операции записи информация, записанная в регистр, сохраняется, несмотря на то что входная информация (число) может изменяться.

Для считывания информации подают импульс по входу «Считывание». На выходные шины регистра передается код числа, записанный в регистр. При этом число, записанное в регистр, сохраняется.

Для

получения новой информации описанные

операции повторяются.При построении

параллельных регистров наибольшее

применение получили D-триггеры

(триггер-«за- щелка»), позволяющие

выполнять параллельные регистры на

малом количестве элементов.Н а

рис. 3.2, а

приведена схема n-разрядного

параллельного регистра на однофазных

D-триггерах

без элементов, управляющих процессом

считывания. Схема служит для записи

информации в регистр по двум каналам

(входы первого канала а1,

..., аn,

входы второго канала b1,

..., bn).

Установка нуля всех разрядов регистра

осуществляется по входу

а

рис. 3.2, а

приведена схема n-разрядного

параллельного регистра на однофазных

D-триггерах

без элементов, управляющих процессом

считывания. Схема служит для записи

информации в регистр по двум каналам

(входы первого канала а1,

..., аn,

входы второго канала b1,

..., bn).

Установка нуля всех разрядов регистра

осуществляется по входу

.

Запись числа по каналу

а

производится тактовым им-

пульсом Та

,а

по каналу

b-тактовым

импульсом Тb.

Принцип действия регистра достаточно

прост. Процесс записи первого разряда

числа а

иллюстрируют временные диаграммы на

рис. 3.2, б.

.

Запись числа по каналу

а

производится тактовым им-

пульсом Та

,а

по каналу

b-тактовым

импульсом Тb.

Принцип действия регистра достаточно

прост. Процесс записи первого разряда

числа а

иллюстрируют временные диаграммы на

рис. 3.2, б.

Последовательные регистры (регистры сдвига). Последовательные регистры (регистры сдвига) характеризуются записью числа последовательным кодом. Регистр состоит из последовательно соединенных двоичных ячеек памяти, состояния которых передаются (сдвигаются) на последующие ячейки под действием тактовых импульсов. Тактовые импульсы управляют работой регистра. Регистры сдвига могут управляться одной последовательностью тактовых импульсов. В этом случае регистры называют однотактными. При управлении двумя, тремя, четырьмя и т. д. последовательностями тактовых импульсов регистры соответственно относят к двух-, трех- и четырехтактным, а в общем случае — к многотактн ы м.

Частота

следования тактовых импульсов обычно

неизменна. В многотактных регистрах

последовательности тактовых импульсов

следуют с взаимным фазовым сдвигом 2 /m

эл. град, где 2

— период следования импульсов одной

из последовательностей, а т

— количество последовательностей

тактовых импульсов.

/m

эл. град, где 2

— период следования импульсов одной

из последовательностей, а т

— количество последовательностей

тактовых импульсов.

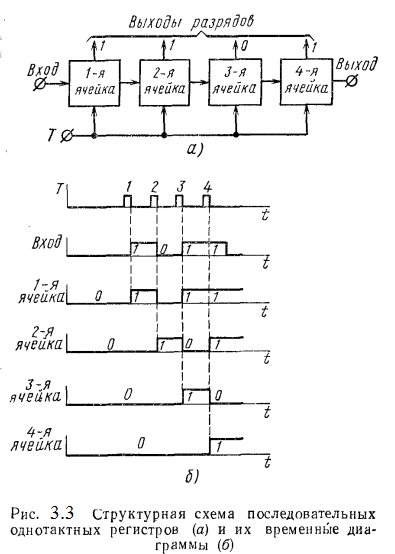

Однотактные регистры сдвига выполняют по структурной схеме рис. 3.3, а, показанной для четырех разрядов. Первая ячейка регистра относится к его младшему разряду, а четвертая — к старшему. При таком расположении разрядов запись числа в регистр производится начиная с его старшего разряда. При обратном расположении разрядов в регистре запись числа должна начинаться с его младшего разряда.

Тактовые импульсы подаются на все триггеры ячеек одновременно. Их воздействие направлено на переключение триггеров из состояния «1» в состояние «0» с записью единицы в триггер следующей ячейки.

На

рис. 3.3, б

приведены временные диаграммы,

иллюстрирующие процесс записи

информации в регистр.

На

рис. 3.3, б

приведены временные диаграммы,

иллюстрирующие процесс записи

информации в регистр.

В качестве примера взят код 1011, соответствующий числу 11. Перед записью информации регистр устанавливают в состояние «0».

Для этого в отсутствие сигнала на входе подается серия тактовых импульсов с числом импульсов, равным количеству разрядов в регистре. При записи информации одновременно с поступлением кода числа подаются тактовые импульсы. Тактовыми импульсами осуществляется продвижение информации от младшего разряда регистра к старшему. В результате после четвертого тактового импульса ячейки регистра принимают состояния, соответствующие коду принятого четырехразрядного числа.

Операция считывания информации из последовательного регистра может быть проведена в параллельном или последовательном коде. Для передачи информации в параллельном коде используют выходы разрядов регистра. Таким образом, последовательный регистр позволяет осуществить операцию преобразования последовательного кода в параллельный, Считывание информации в последовательном коде реализуется подачей серии тактовых импульсов.

В последовательном регистре записанное число может быть сдвинуто тактовыми импульсами на один или несколько (k) разрядов. Операции сдвига соответствуют умножению числа на 2k. Например, сдвиг кода 0010 числа 2 на один разряд дает код 0100 (число 4), на два разряда — код 1000 (число 8).

При реализации однотактных регистров сдвига необходимо учитывать следующее обстоятельство. В этих регистрах тактовые импульсы воздействуют на перевод в состояние «0» триггеров всех разрядов одновременно. Поэтому в однотактных регистрах должна быть решена задача разделения во времени (по меньшей мере на длительность тактовых импульсов tи) операций считывания единицы с триггера каждого разряда и ее переписи в триггер следующего разряда. В противном случае перепись единицы в следующий разряд не будет произведена.

Эта задача может быть решена включением в цепь передачи сигнала от одной ячейки к другой элемента задержки. Элемент задержки будет задерживать импульс записи единицы в последующую ячейку на время действия тактового импульса. Однако наличие элементов задержки обусловливает критичность работы схемы в отношении длительности тактовых импульсов. Кроме того, для элементов задержки, состоящих из реактивных элементов L, С, затруднено интегральное исполнение. В связи с указанным разнесение во времени операций считывания и переписи единицы осуществляют схемными средствами, например выполнением ячеек на триггерах с внутренней задержкой (R-St, J-Kt,Dt триггерах).

При использовании триггеров с внутренней задержкой разделение во времени операций считывания и переписи единицы выполняется автоматически, поскольку новое состояние таких триггеров формируется после окончания действия тактовых импульсов.

Другим методом построения однотактных регистров сдвига является использование двухтактного режима их работы. В каждую ячейку таких регистров входят два триггера (основной и дополнительный). Управление производится одной последовательностью тактовых импульсов. Разделение во времени операций считывания единицы из предыдущей ячейки и ее переписи в последующую ячейку достигается тем, что считывание единицы из основных триггеров осуществляется в момент поступления тактового импульса, а запись единицы в них — по окончании тактового импульса.

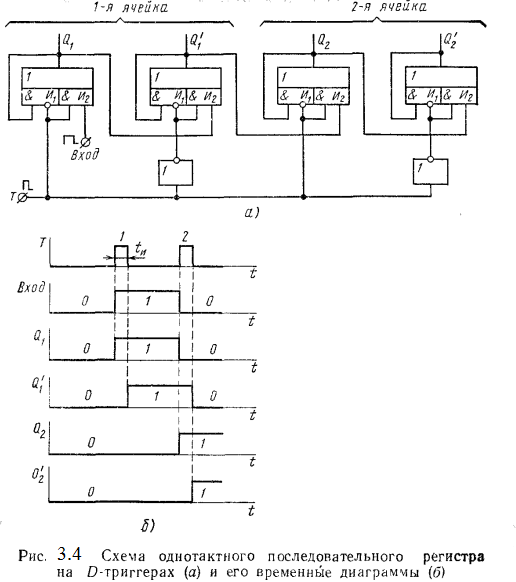

В схемном отношении рассматриваемый метод построения однотактных регистров сдвига наиболее просто реализуется с применением тактируемых D-триггеров. Схема двухразрядного регистра, выполненная на D-триггере, приведена на рис. 3.4, а. Временные диаграммы рис. 3.4, б иллюстрируют процесс продвижения единицы в регистре в сторону старшего разряда.

В отличие от триггера, а вход «Установка нуля» в триггере регистра является инверсным. Инверсный вход «Установка нуля» всех триггеров объединен с тактируемым входом и связан в основных триггерах ячеек регистра с шиной тактовых импульсов Т непосредственно, а в дополнительных триггерах — через элемент НЕ.

В

исходном состоянии все триггеры регистра

установлены в состояние «0» (рис, 3.4,

б).

При наличии сигнала на входе первым

тактовым импульсом через открытый

элемент И2

записывается единица в основной

триггер первого разряда (ячейки). Сигнал

Q1

= 1 передается на информационный вход

дополнительного триггера первой ячейки,

но поскольку на выходе ее инвертора

действует сигнал

=0,

элемент И2

закрыт и дополнительный триггер остается

в состоянии «0»(Q1

= 0).

=0,

элемент И2

закрыт и дополнительный триггер остается

в состоянии «0»(Q1

= 0).

По

окончании первого тактового импульса

на обоих входах элемента И2

дополнительного триггера первой ячейки

присутствует единица, он переключается

в состояние Q'

= 1. Таким образом, результатом

поступления первого тактового импульса

является запись единицы в оба триггера

первой ячейки. Состояние «1» основного

триггера сохраняется по входам

элемента И1(Q1

=1,

Т=0),

а дополнительного — по входам элемента

И2

(Q1=1, =1).

=1).

Если сигнал на входе регистра равен нулю, то поступление второго тактового импульса приводит к запиранию элементов И1 И2 основ-

ного триггера первой ячейки и переключению его в состояние «0». При этом основной триггер второй ячейки по входам элемента И2 (Q'1 = 1, Т = 1) переключается в состояние Q2 = 1.

На этапе действия второго тактового импульса дополнительный триггер первой ячейки поддерживается.В состоянии Q'1 = 1 по обоим входам элемента И1 а дополнительный триггер второй ячейки остается в состоянии Q'2= 0 по обоим входам его элемента И1.

После окончания второго тактового импульса элементы И1, И2 дополнительного триггера первой ячейки закрываются, что вызывает переключение этого триггера в состояние Q'1 = 0. Дополнительный триггер второй ячейки переводится в состояние Q'2 = 1 наличием единиц на входах его элемента И2. Таким образом, происходит перемещение входной информации во второй разряд регистра.

Каждая ячейка (разряда) многотактного регистра состоит в общем случае из m последовательно включенных триггеров.

Управление многотактным регистром производится т последовательностями тактовых импульсов, причем каждая из последовательностей предназначена для управления одноименными триггерами ячеек. Применение многотактного режима работы является еще одним методом разнесения во времени операций считывания и записи информации в разрядах регистра. Главное же преимущество много- тактных регистров — их высокая информативность, обусловленная большим числом выходов каждого разряда.

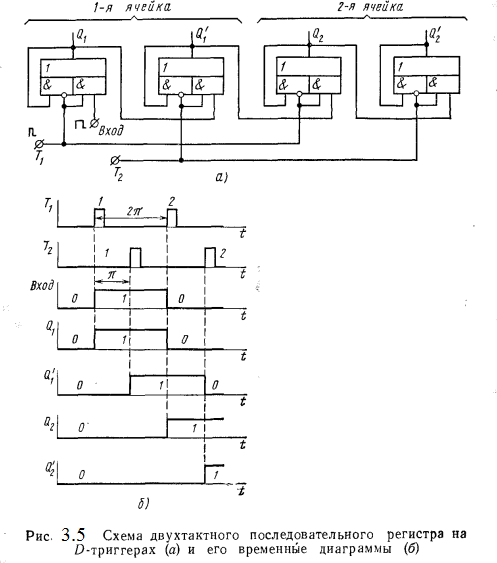

Построение двухтактных регистров сдвига показано на примере двухразрядного регистра (рис. 3.5, а). Каждая его ячейка состоит из двух D-триггеров предыдущей схемы. Управление основными триггерами ячеек осуществляется тактовыми импульсами Т1, а дополнительными — T2. Фазовый сдвиг второй последовательности тактовых импульсов относительно первой равен те (7/2).

Процесс

записи информации (при наличии единичного

сигнала на входе) иллюстрируют временные

диаграммы рис. 3.5, б.

Первым тактозым импульсом по каналу Т1

записывается единица в первый триггер

первой ячейки. Затем тактовым импульсом

по каналу T2

записывается единица во второй

триггер первой ячейки. Вторым тактовым

импульсом канала Т1

осуществляется считывание единицы с

первого триггера первой ячейки и запись

единицы в первый триггер второй ячейки.

Вторым тактовым импульсом по каналу T2

устанавливается в состояние «0» второй

триггер первой ячейки, а во второй

триггер второй ячейки записывается

единица.

Процесс

записи информации (при наличии единичного

сигнала на входе) иллюстрируют временные

диаграммы рис. 3.5, б.

Первым тактозым импульсом по каналу Т1

записывается единица в первый триггер

первой ячейки. Затем тактовым импульсом

по каналу T2

записывается единица во второй

триггер первой ячейки. Вторым тактовым

импульсом канала Т1

осуществляется считывание единицы с

первого триггера первой ячейки и запись

единицы в первый триггер второй ячейки.

Вторым тактовым импульсом по каналу T2

устанавливается в состояние «0» второй

триггер первой ячейки, а во второй

триггер второй ячейки записывается

единица.

Аналогично выполняются регистры сдвига на большее число тактов работы.

Параллельно-последовательные и реверсивные регистры. В параллельно-последовательных регистрах сочетаются свойства регистров параллельного и последовательного действия. Они позволяют осуществлять запись информации как в последовательном, так и параллельном коде, в связи с чем могут быть использованы для преобразования кодов из последовательного в параллельный и обратно. Эти регистры допускают однотактный (рис. 3.6) и многотактный принципы построения.

Для преобразования последовательного кода в параллельный серией тактовых импульсов в регистр записывается информация (число) последовательного кода. Выходы разрядов регистра при этом пред-

ставляют ту же информацию в параллельном коде. Для обратного преобразования информация в регистр вводится по входам параллельного кода. Посредством серии тактовых импульсов с выхода последнего разряда регистра информация считывается в последовательном коде.

Реверсивные регистры предназначены для осуществления сдвига кода числа в сторону как старшего, так и младшего разрядов. Регистр содержит связи последовательной передачи информации в направлении от младших разрядов к старшим, а также от старших разрядов к младшим. Прямой или обратный сдвиг кода осуществляют управляющим сигналом, вводящим в действие либо прямую, либо обратную связи между разрядами.