Генератор тактовых импульсов кр580гф24

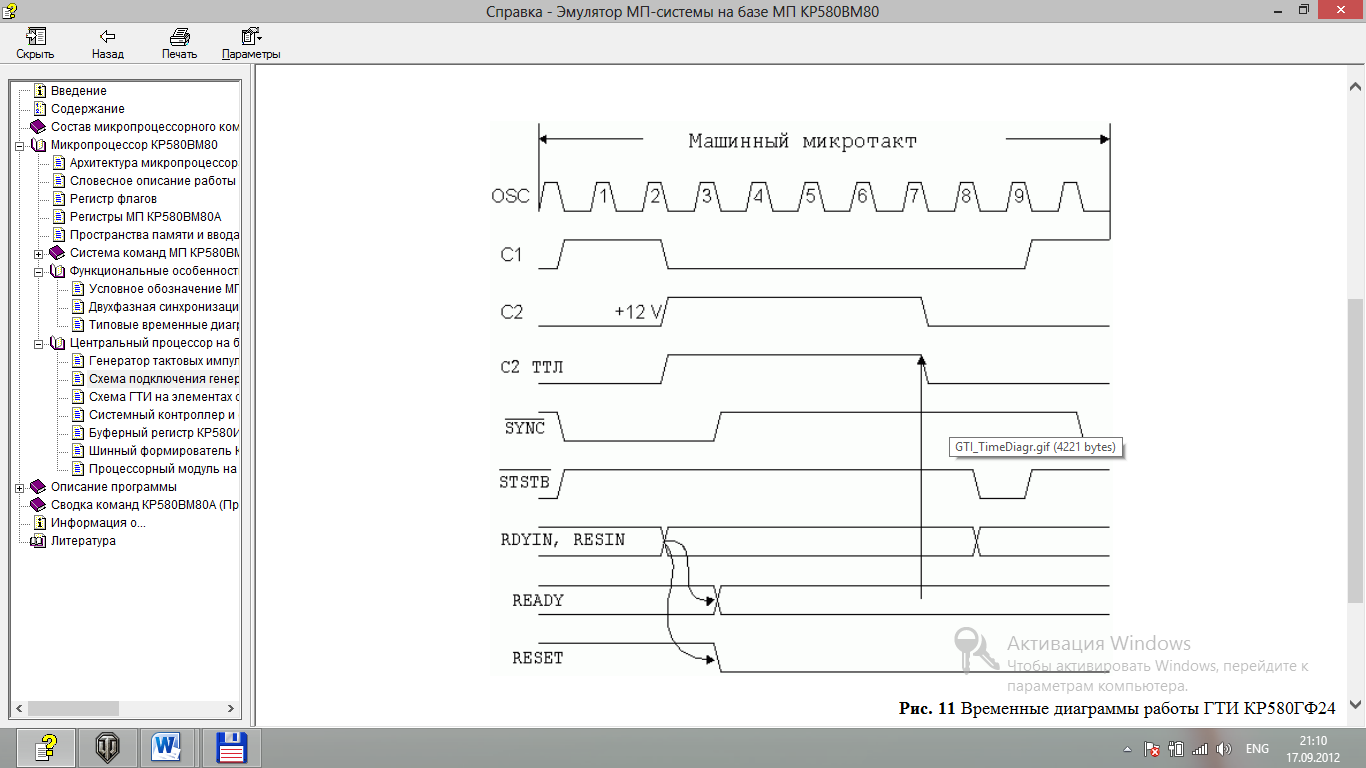

Генератор тактовых импульсов (ГТИ) формирует:

две фазы тактовых импульсов С1, С2 положительной полярности амплитудой 12 В с частотой 0.3-3 Мгц; тактовые сигналы опорной частоты с амплитудой напряжения ТТЛ-уровня;

стробирующий сигнал состояния #STSTB;

синхронизирует внешние сигналы системного сброса #RESIN и готовности #RDYIN.

ГТИ состоит из генератора опорной частоты CLK, счетчика - делителя на 9, формирователя сигналов С1, С2, триггеров фазировки сигналов #RESIN и #RDYIN и логических схем (рис. 9).

Схема подключения генератора КР580ГФ24 к МП ВМ80А

Выход генератора буферизован и выведен на линию OSC, чтобы другие устройства МПС могли его использовать (рис. 10).

Частота кварцевого резонатора должна быть в 9 раз больше тактовой частоты и лежит в пределах 4.5-22.5 МГц. При частоте резонатора большей 10 МГц необходимо последовательно в цепь резонатора подключить конденсатор емкостью 3..10 пф.

Вход TANK предназначен для подключения колебательного контура, работающего на высших гармониках резонатора (для дополнительной стабилизации тактовых сигналов опорной частоты). Стробирующий сигнал состояния #STSTB формируется при наличии на входе SYNC высокого уровня и используется для занесения информации о состоянии МП в системный контроллер КР580ВК28/38 или внешний регистр. Как отмечалось, эта информация используется для формирования управляющих сигналов на шине управления МПС.

Схема ГТИ на элементах средней степени интеграции

Схема ГТИ на элементах средней степени интеграции приведена на рис. 12. Частота опорного генератора должна быть в 4 раза больше тактовой частоты. На триггерах D2, управляемых отрицательными фронтами, изготовлен делитель частоты на 4. Фазированные сигналы С1, С2 формируются с помощью логических элементов D1.4, D3.1, D3.2.

Системный контроллер и формирователь шины данных КР580ВК28/38

Структурная схема ВК28/38 приведена на рис. 14.

Контроллер формирует базовый набор управляющих сигналов магистрали типа Microbus и обеспечивает двунаправленную буферизацию шины данных МПС.

В БИС использована ТТЛШ - технология. Выход контроллера со стороны системной магистрали обеспечивает токовую нагрузку до 10 мА с емкостью нагрузки до 100 пф. Задержка, вносимая шинным формирователем в шину данных, не превышает 40 нс. Формирователь выполнен по схеме с тремя состояниями.

В состав контроллера входит регистр-защелка, который по стробу #STSTB фиксирует слово состояния SW, выдаваемое МП в начале каждого машинного цикла. Это слово определяет тип текущего МЦ, в зависимости от которого логические схемы контроллера формируют один из пяти управляющих стробов системной магистрали: #MEMR, #MEMW, #IOR, #IOW, #INTA. В случае, когда МПС использует медленно работающие модули, длительность стробов могут оказаться недостаточными для правильного выполнения операций обмена, и ее продлевают, используя сигнал готовности RDYIN.

Строб #INTA обычно используется для выбора порта вектора прерывания, изолированного от пространства ВВ. В МПС, где требуется только один вектор прерываний, устройство ВК28/38 может автоматически в необходимый момент времени выдавать команду RST 7 на ШД без каких-либо дополнительных логических схем. Для этого выход #INTA нужно соединить с источником питания +12 В через резистор R=1 к.

Трехстабильные выходные буферы ШД и управляющих сигналов открываются асинхронно внешним входным сигналом #BUSEN. При #BUSEN=1 буферы и ШУ находятся в третьем состоянии.

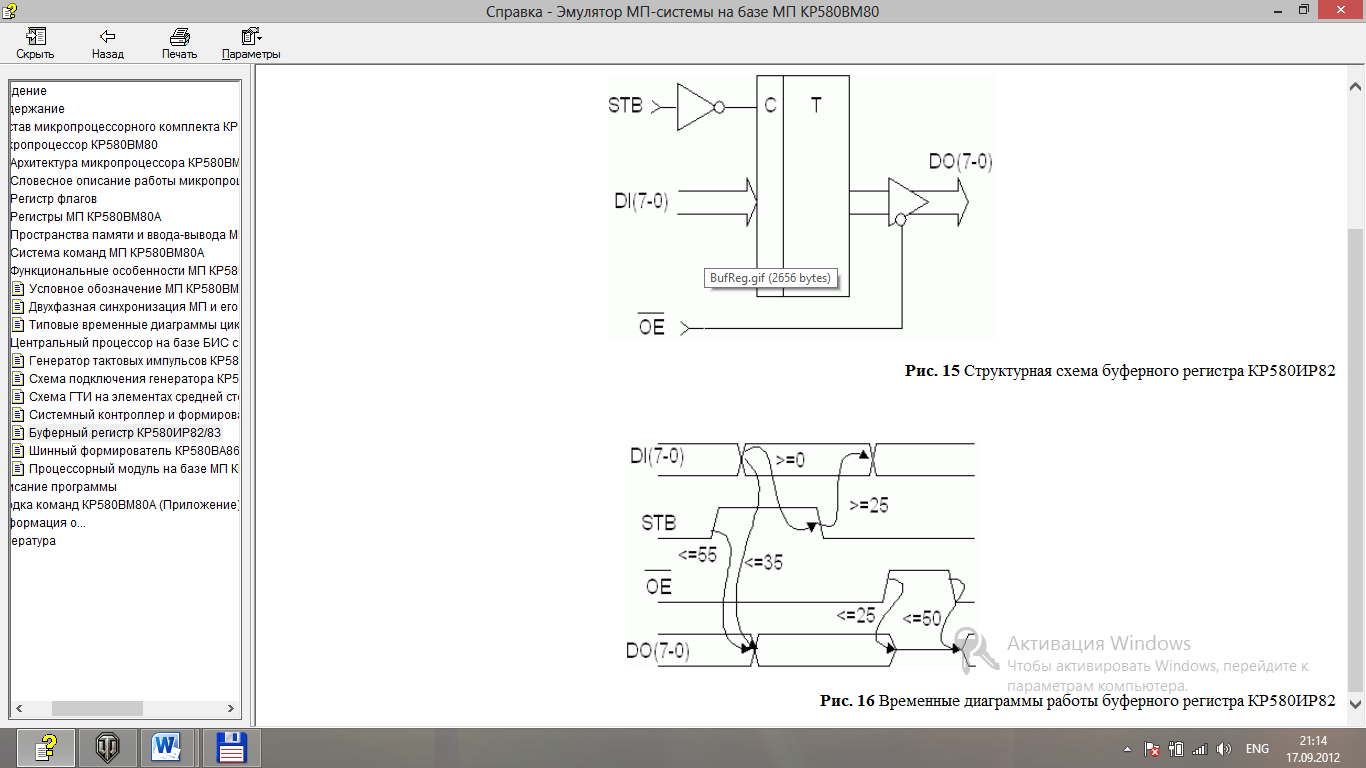

Буферный регистр КР580ИР82/83

Буферный регистр ИР83 в отличие от ИР82 имеет инверсную выходную шину. В остальном эти два регистра одинаковы.

Основой схемы является 8-разрядный регистр-защелка со статическим входом STB (рис. 15). Запись в регистр разрешена при STB=1, в противном случае регистр находится в режиме хранения. На выходе регистра имеется 3-стабильный буфер, управляемый сигналом OE (OE - Output Enable). Буфер обеспечивает выходной ток до 32 мА и емкостную нагрузку до 300 пф. При #OE=1 выходной буфер находится в высокоомном состоянии. Временные диаграммы работы буферного регистра приведены на рис. 16.

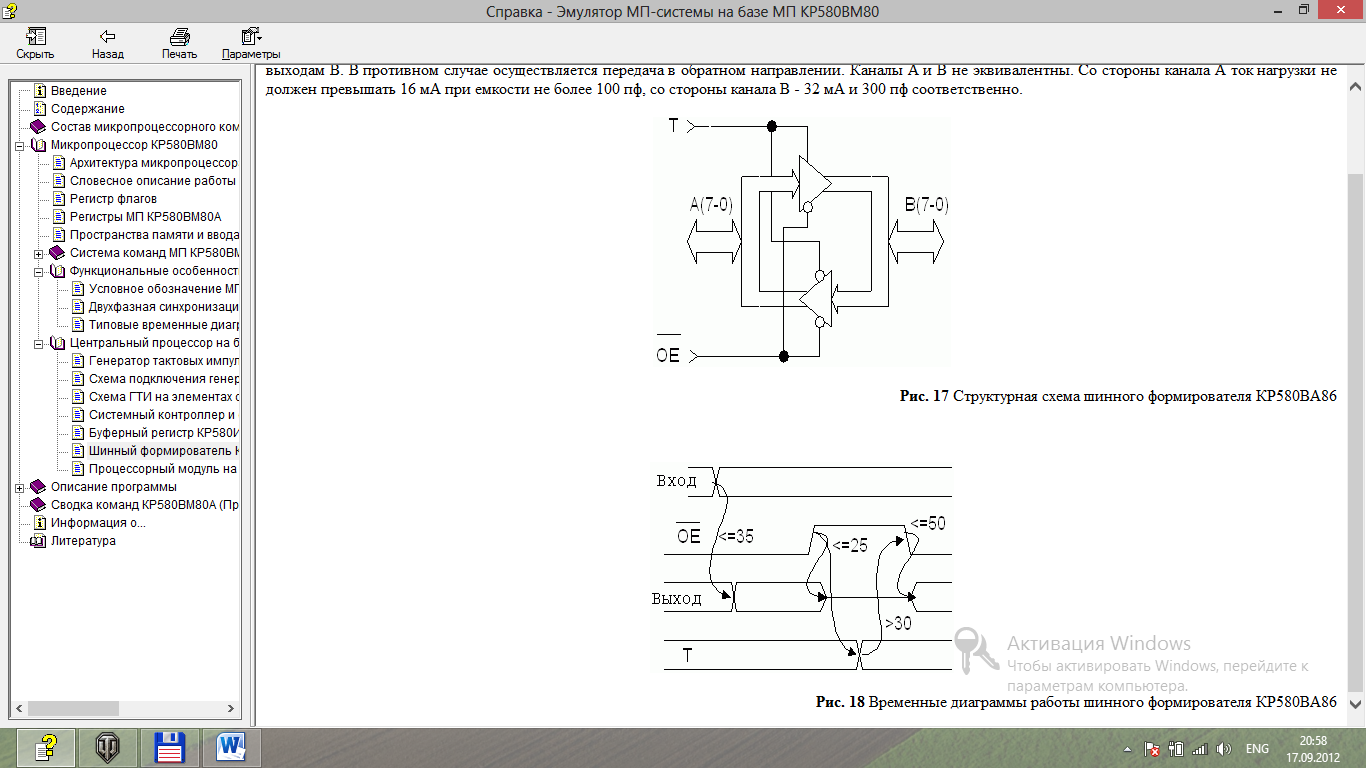

Шинный формирователь КР580ВА86/87

Шинный

формирователь ВА87 отличается от ВА86

тем, что имеет инвертирующие буферы.

Трехстабильные буферы выбираются по

условию #OE=0. При этом, если на входе T

(T-Trasmitter) присутствует высокий уровень

напряжения, то буфер открыт в направлении

передачи информации от входа А к выходам

В. В противном случае осуществляется

передача в обратном направлении. Каналы

А и В не эквивалентны. Со стороны канала

А ток нагрузки не должен превышать 16 мА

при емкости не более 100 пф, со стороны

канала В - 32 мА и 300 пф соответственно.

Рис. 17 Структурная схема шинного формирователя КР580ВА86

Рис. 18 Временные диаграммы работы шинного формирователя КР580ВА86

Процессорный модуль на базе МП КР580ВМ80А

Схема центрального процессора на базе МП КР580ВМ80А приведена на рис. 19. Помимо МП она включает тактовый генератор на ИМС КР580ГФ254, адресные буферные регистры КР580ИР82, системный контроллер КР580ВК38.

Чтобы выполнить функцию начальной установки МП, ко входу #RESIN тактового генератора необходимо подключить RC-цепочку. Постоянная времени RC-цепочки рассчитывается из требований к длительности импульса RESET. Период следования фазовых сигналов С1 и С2 определяется кварцевым резонатором ZQ1. Емкость С4 компенсирует индуктивную составляющую генератора ГФ24 со стороны входов XTAL1, XTAL2. Генератор формирует также системный сигнал CCLK (ток нагрузки низкого уровня не более 15 мА) и сигнал системного сброса INIT (ток нагрузки низкого уровня не более 15 мА), предназначенный для начальной установки устройств МПС. Он выдается при наличии сигнала, формируемого RC - цепочкой на входе #RESIN генератора. Для приведенных номиналов элементов на схеме рис. 19 длительность сигнала INIT равна 0.35 с.

Входы HOLD и INT микропроцессора должны быть подключены к общей шине, если МПС не использует прямой доступ к памяти и прерывания.

На рис. 20 приведена схемная реализация системного контроллера на ИМС средней степени интеграции.