Типовые временные диаграммы циклов чтения и записи

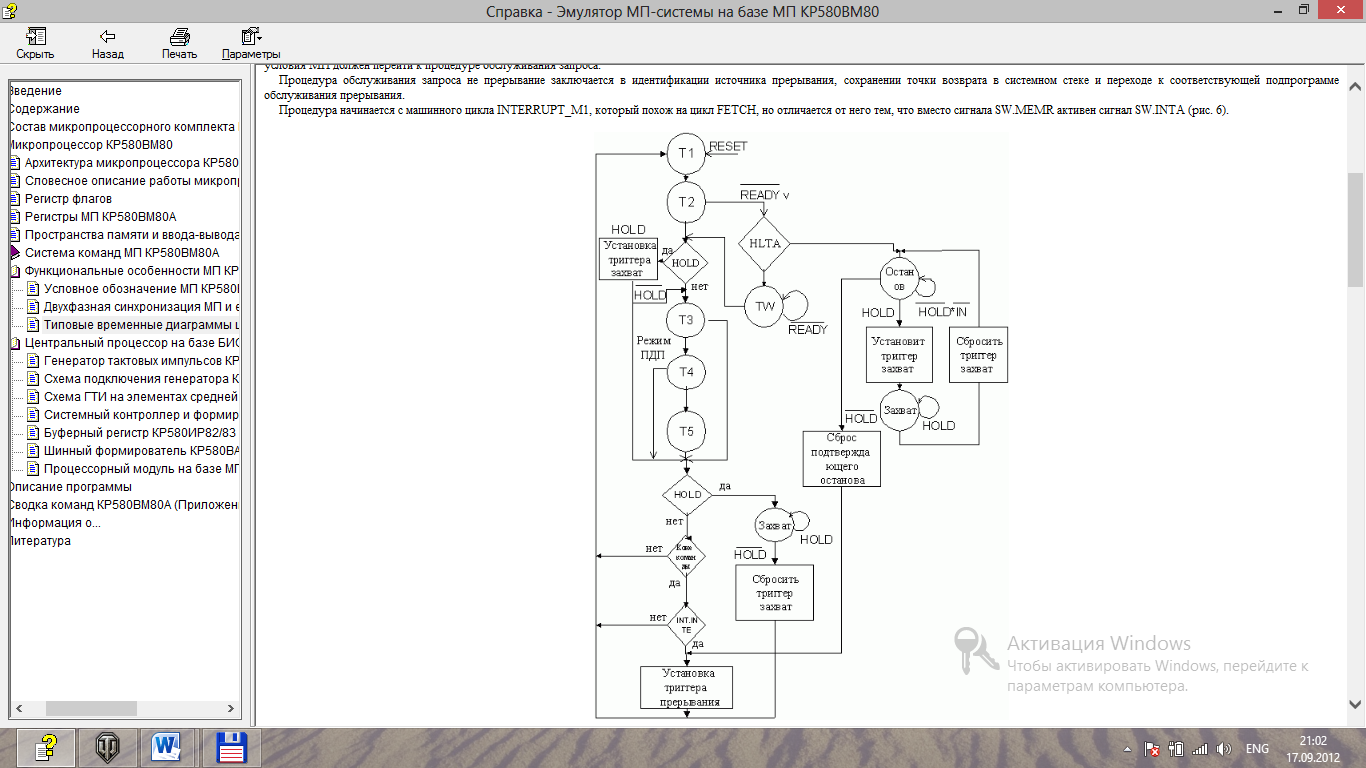

Диаграмма состояний МП (конечный автомат Мура) приведена на рис. 4. На диаграмме кружочками показаны состояния микропроцессора, а обозначениями на стрелках – условия перехода из одного состояния в другое.

Микропроцессор работает следующим образом:

Подача сигнала высокого Н-уровня на вход RESET длительностью не менее 3-х периодов тактовой частоты устанавливает микропроцессор в исходное состояние. При этом в программный счетчик РС заносятся нули, а схема управления начинает формировать такт Т1 машинного цикла М1;

В такте Т1 по шине данных выдается информация о типе машинного цикла SW, формируется высокий уровень сигнала SYNC и выдается адрес команды или операнда. Слово состояния SW должно быть зафиксировано во внешнем регистре по условию SYNC*C1 в начале второго такта;

В такте Т2 по срезу сигнала синхронизации С2 проверяются сигналы готовности READY и подтверждения останова HLTA, и в зависимости от состояния этих сигналов МП переходит в состояние ожидания, останова или к выполнению цикла Т3. Кроме того, в такте Т2 МП устанавливает высокий уровень сигнала DBIN и на шину данных поступает информация для чтения из ВУ или памяти (рис. 5). Если необходимо согласовать во времени работу ЗУ и МП, то можно увеличить длительность приема сигнала DBIN подачей сигнала READY низкого уровня. Тогда МП переходит в состояние ожидания, а шины адреса, данных и сигнал DBIN не изменяют своего состояния. Продолжительность сигнала WAIT определяется длительностью сигнала низкого уровня READY, который контролируется по срезу импульса С2 в каждом такте.

При обнаружении высокого уровня сигнала READY микропроцессор из такта Tw переходит к выполняющему обмен такту Т3. Такты Т4, Т5, если они присутствуют в данном машинном цикле, используются для завершения МЦ за счет внутренних операций МП. Если команда не завершилась, то МП переходит к такту Т1 следующего МЦ данной команды.

МП имеет несложные встроенные средства обслуживания запросов на прерывания с тремя управляющими сигналами:

INT - запрос на прерывание;

INTE - разрешение прерывания;

SW INTA - подтверждение прерывания.

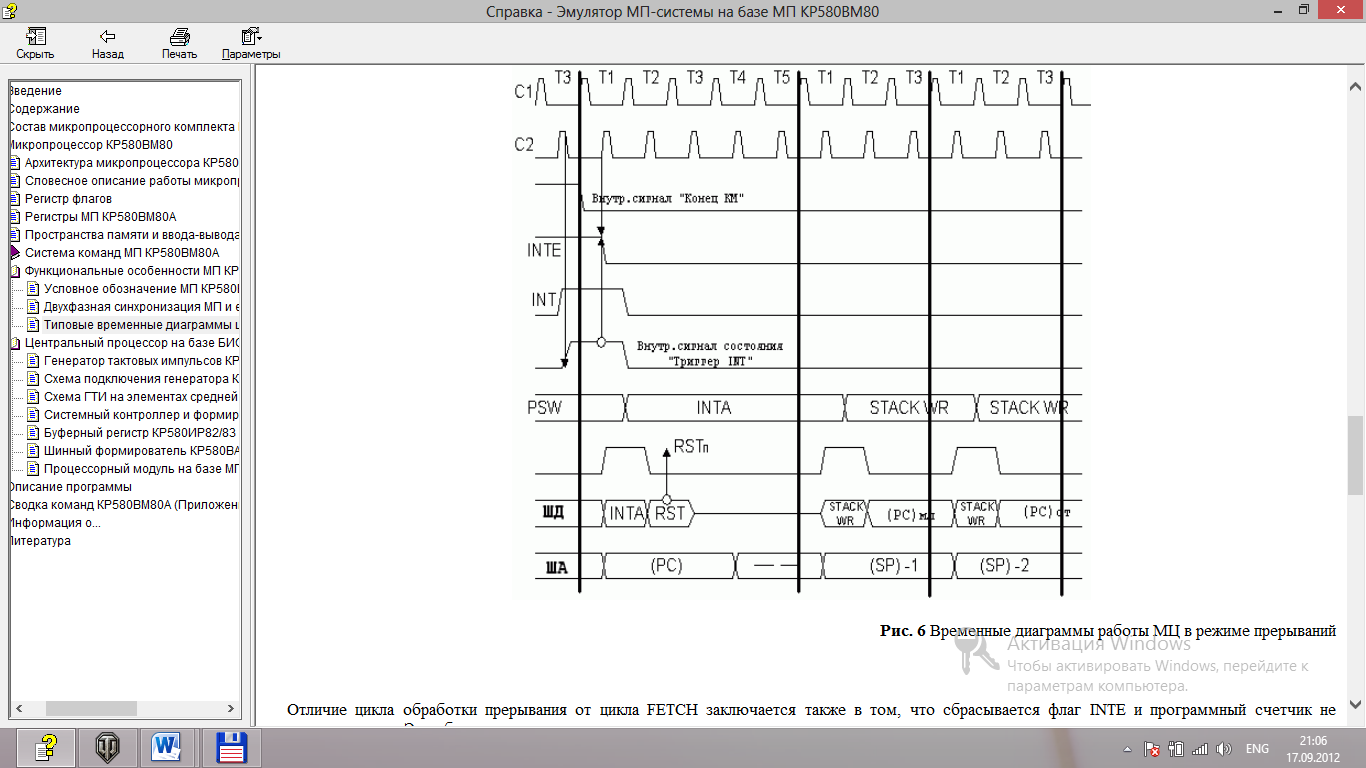

Сигнал разрешения прерывания INTE управляется программно с помощью команд EI (Enable Interrupt) и DI (Disable Interrupt), маскируя вход INT микропроцессора. Условие прерывания INT*INTE=1 проверяется в последнем такте каждого командного цикла (за исключением команды EI, что гарантирует завершение выполнения любой команды). При выполнении этого условия МП должен перейти к процедуре обслуживания запроса. Процедура обслуживания запроса не прерывание заключается в идентификации источника прерывания, сохранении точки возврата в системном стеке и переходе к соответствующей подпрограмме обслуживания прерывания. Процедура начинается с машинного цикла INTERRUPT_M1, который похож на цикл FETCH, но отличается от него тем, что вместо сигнала SW.MEMR активен сигнал SW.INTA (рис. 6).

Рис.

4 Диаграмма состояний микропроцессора

КР580ВМ80А при выполнении

типового

машинного цикла (конечный автомат Мура)

Рис.

4 Диаграмма состояний микропроцессора

КР580ВМ80А при выполнении

типового

машинного цикла (конечный автомат Мура)

Рис.

5 Временная диаграмма циклов чтения

и записи

Рис.

5 Временная диаграмма циклов чтения

и записи

Отличие цикла обработки прерывания от цикла FETCH заключается также в том, что сбрасывается флаг INTE и программный счетчик не инкрементируется. Это обеспечивает сохранность точки возврата. В такте Т1 этого цикла на шину адреса выдается содержимое программного счетчика, а на ШД - слово состояния процессора INTERRUPT_M1, сбрасывается сигнал разрешения прерывания INTE, что запрещает прием последующих запросов прерывания. В такте Т2 на ШД устанавливается код операции прерывания RST n с помощью ВУ, выставившего запрос. Использование команды RST n подразумевает резервирование первых 64-х (8*8) байтов памяти под таблицу входов в подпрограммы обслуживания прерываний. Обычно по адресам 8n, n=0..7 находятся команды JMP, передающие управление на подпрограммы обслуживания прерываний, или команды диспетчера прерываний, задающего косвенные адреса подпрограмм обслуживания прерываний в ОЗУ системы (инициализируются при загрузке системы). Возврат из подпрограммы обслуживания прерывания выполняется с помощью команд

EI ; разрешить прерывания INTE <--1 RET ; возврат

В такте Т2 сбрасывается также внутренний триггер прерывания, а содержимое РС не изменяется. В такте Т3 команда RST n с шины данных вводится в МП, а в тактах Т4, Т5 производится ее дешифрование. По команде RST n содержимое РС запоминается в стеке, а в РС заносится адрес первой команды подпрограммы обработки прерывания, равный 8*n. Запоминание адреса возврата из прерывания в стеке выполняется в циклах М2 и М3 - запись в стек. В состояние останова (рис. 7) МП переходит при наличии сигнала HLTA, формируемого во втором МЦ команды HLT. При этом ША и ШД переводятся в третье состояние, и формируется сигнал WAIT.

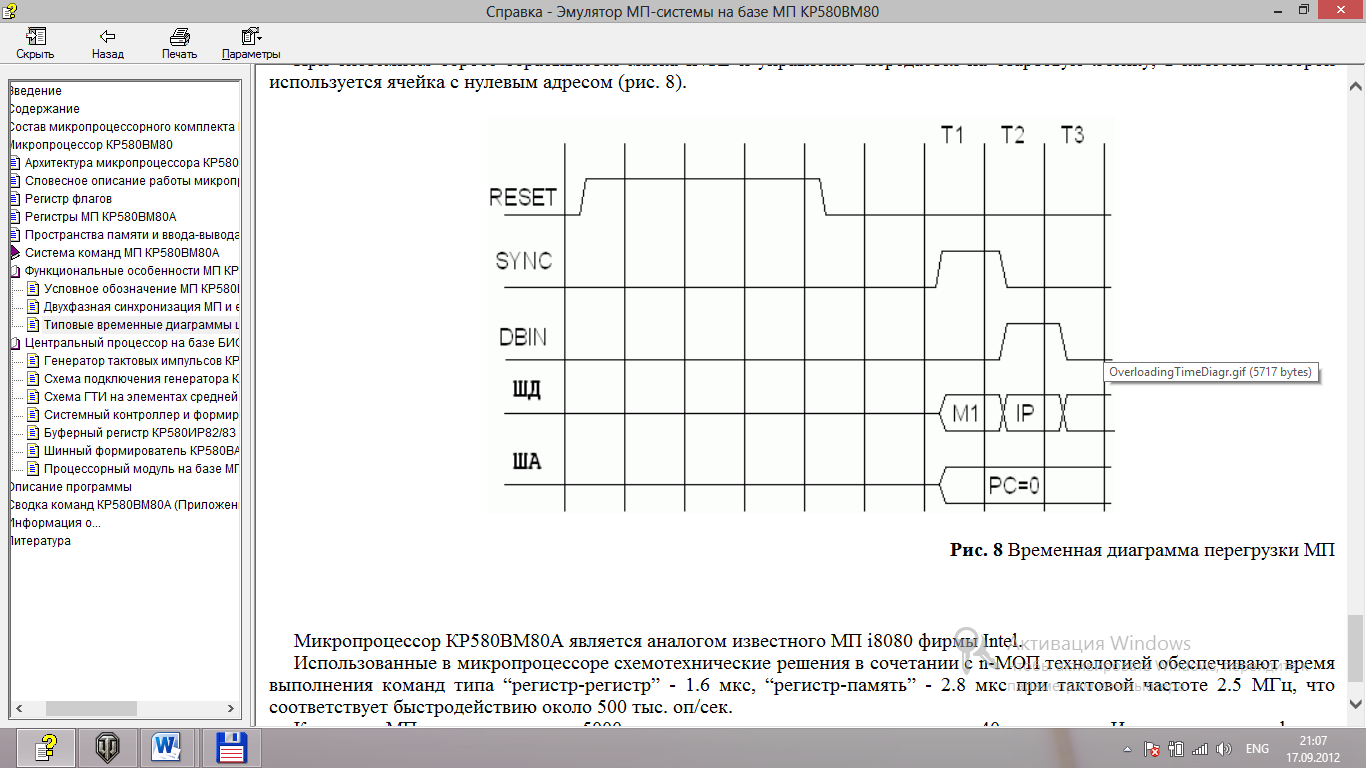

Из состояния останова МП выходит по сигналу системного сброса RESET или по сигналу запроса прерывания INT при установленном триггере разрешения прерывания (INTE=1). Находясь в состоянии останова, МП может временно переходить в режим захвата, если на него поступает высокий уровень сигнала HOLD. При наличии этого сигнала и READY=1 в такте Т2 производится установка внутреннего триггера захвата, однако переход к режиму захвата не разрешается, чтобы МП успел закончить обмен с ВУ в начале такта Т3. По окончании захвата МП всегда переходит к такту Т1 следующего машинного цикла. Если текущий МЦ содержит такты Т4, Т5, то они совмещаются с режимом захвата. При системном сбросе сбрасывается маска INTE и управление передается на стартовую ячейку, в качестве которой используется ячейка с нулевым адресом (рис. 8).

Микропроцессор КР580ВМ80А является аналогом известного МП i8080 фирмы Intel. Использованные в микропроцессоре схемотехнические решения в сочетании с n-МОП технологией обеспечивают время выполнения команд типа “регистр-регистр” - 1.6 мкс, “регистр-память” - 2.8 мкс при тактовой частоте 2.5 МГц, что соответствует быстродействию около 500 тыс. оп/сек. Кристалл МП содержит около 5000 транзисторов и помещен в корпус с 40 выводами. Используется двухфазная синхронизация импульсами 12 В. Выходные буферы МП обеспечивают токовую нагрузку для подключения одного стандартного TTЛ - входа и емкостную нагрузку до 100 пф. Микропроцессор питается от трех источников питания: - 5 В (< 1 мA), + 5 В (<70 мA), -12 В (<50 мА).