- •Предисловие

- •Порядок выполнения и оформления работы

- •Лабораторная работа № 1

- •1. Основные положения

- •Порядок выполнения работы

- •4. Содержание отчета

- •5. Контрольные вопросы

- •1. Основные положения

- •По моменту времени изменения состояния триггера:

- •2. Краткое описание триггера реализованного в quartus II.

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •5. Контрольные вопросы

- •1. Основные положения Регистры.

- •2. Краткое описание изучаемых регистров реализованных в quartus II.

- •3. Порядок выполнения работы

- •Исследование регистров с параллельной записью информации.

- •Исследование сдвигового регистра

- •4. Содержание отчета

- •5. Контрольные вопросы

- •1. Основные положения Счетчики.

- •2. Краткое описание изучаемых и счетчиков реализованных в quartus II.

- •3. Порядок выполнения работы

- •Исследование счетчика.

- •4. Содержание отчета

- •5. Контрольные вопросы

- •1. Основные положения

- •Преобразователи кодов (шифраторы и дешифраторы).

- •2. Краткое описание изучаемых комбинационных устройств реализованных в quartus II.

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •5. Контрольные вопросы

- •1. Основные положения

- •Мультиплексоры и демультиплексоры.

- •Компараторы.

- •2. Краткое описание изучаемых комбинационных устройств реализованных в quartus II.

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •5. Контрольные вопросы

- •1. Основные положения

- •2. Краткое описание изучаемых сумматоров реализованных в quartus II.

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •5. Контрольные вопросы

- •Литература

2. Краткое описание изучаемых сумматоров реализованных в quartus II.

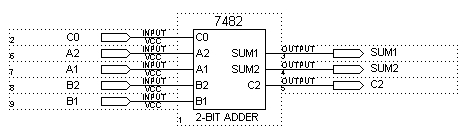

Модуль 7482 (рис. 3) – полный двухразрядный бинарный сумматор.

Рисунок 3 Полный двухразрядный бинарный сумматор 7482

Модуль содержит:

Две входных двухразрядных линии данных (А1, А2 и В1, В2), где индексы 1 – младший, а 2 – старший разряд доичного числа;

Вход переноса из младшего разряда С0;

Двухразрядный выход (SUM1 – младшй разряд, SUM2 – старший разряд);

Выход переноса в следующий разряд (С2).

Модуль 74385 (рис. 4) – четырехразрядный синхронный сумматор-вычитатель с очисткой.

Рисунок 4 Четырехразрядный синхронный сумматор-вычитатель с очисткой 74385.

Модуль содержит:

Вход синхронизации CLK;

Две входные четырехразрядные линии данных (А1, А2, А3, А4 и В1, В2, В3, В4), где индексы 1, 2, 3 и 4 разряды доичного числа, от младшего к старшему, соответственно;

4 входа выбора операции (S/AN), свой для каждого разряда;

Вход сброса CLRN;

Четырехразрядный выход S (S1, S2, S3, S4).

Режимы работы сумматора-вычитателя:

CLRN=0 – сумматор-вычитатель очищен (сброшен);

C LRN=1, CLK= , S/AN=0 – режим сумматора;

C LRN=1, CLK= , S/AN=1 – режим вычитателя.

3. Порядок выполнения работы

Исследование полного двухразрядного бинарного сумматора 7482.

Создание нового проекта. Смотри лаб.раб.1 п. 3.1.1.

Создание графического описания проектируемого устройства. Смотри лаб.раб.1 п. 3.1.2. На плоскости рисунка курсором следует указать место расположения исследуемого модуля. Затем выполнить действия по извлечению нужного элемента из библиотеки по цепочке Symbol – Enter Symbol- DISK:\maxplus2\ max2lib\mf извлечь элемент 7482 и проверить его таблицу истинности. Таблицу истинности необходимо извлечь из справочной системы САПР по цепочке HELP-Old-Style Macro function – Register-7482.

После установления связей между элементами присваиваем имена каждому входу и выходу ПЛИС.

Созданное графического описания проекта необходимо сохранить.

Компиляция проекта. Смотри лаб.раб.1 п. 3.1.3.

Тестирование проекта. Смотри лаб.раб.1 п.п. 3.1.4.1 3.1.4.3.

После ввода всех входов и выходов необходимо задать рисунок входных сигналов с помощью панели инструментов и проверить таблицу истинности.;

Смотри лаб.раб.1 п.п. 3.1.4.5 3.1.4.10.

Исследование четырехразрядного синхронного сумматора-вычитателя с очисткой 74385

Порядок выполнения смотри п. 3.1.

Примечание: извлечение нужного элемента из библиотеки по цепочке Symbol – Enter Symbol- DISK:\maxplus2\ max2lib\mf извлечь элемент 74385 и проверить его таблицу истинности. Таблицу истинности необходимо извлечь из справочной системы САПР по цепочке HELP-Old-Style Macro function – Register-74385.

4. Содержание отчета

Отчет по лабораторной работе должен содержать:

Цель работы;

Изображение исследуемых микросхем;

Таблицы истинности;

Изображение результатов моделирования в среде MAX+PLUS II (файлы с расширением *.SCF).

Сравнение результатов исследования с табличными;

Выводы по работе.