- •Оглавление

- •Вступление

- •Реализация cpu для выполнения команд сложения и вычитания алгебраических чисел

- •Начальные данные

- •Состав и описание структурной схемы cpu для выполнения команд add и sub

- •Описание алгоритма операций сложения и вычитания машинных чисел

- •Состав и описание узлов модуля операционного блока (моб) для выполнения операций сложения и вычитания машинных чисел

- •Реализация моб для выполнения операции деления чисел

- •Начальные данные

- •Обоснование алгоритма деления чисел

- •Реализация моб для выполнения операции умножения чисел

- •Начальные данные

- •Обоснование алгоритма умножения чисел

- •Состав и описание операционных элементов функциональной схемы (фс) моб для выполнения операции умножения чисел

- •Синтез по заданному элементному базису минимальных реализаций функциональных узлов моб для выполнения умножения чисел

- •Синтез регистров (ра, рв, рс)

- •Синтез регистра ра на базе к155тм8:

- •Синтез коммутатора (кома):

- •Синтез регистра ра

- •2)Синтез регистра рв на базе к155тм8:

- •Синтез коммутатора (комв):

- •Синтез регистра рb

- •Синтез регистра рc на базе к155тм8:

- •Синтез коммутатора (комc):

- •Синтез регистра рc

- •Синтез коммутатора (ком)

- •Синтез сумматора (sm)

- •3.4.3 Синтез счетчика (сt)

- •Синтез триггера знака (тзн)

- •Список литературы

-

Синтез коммутатора (ком)

Таблица синтеза коммутатора КОМC имеет следующий вид (таблица 3.11):

Таблица 3.11 Таблица микроопераций коммутатора КОМ

|

СNA |

С2NA |

С4NA |

С2A |

С4A |

Ki |

K30 |

K31 |

|

0 |

0 |

0 |

0 |

1 |

PAi+2 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

PAi+1 |

PA31 |

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

|

0 |

|

1 |

0 |

0 |

0 |

0 |

|

|

|

|

* |

* |

* |

* |

* |

* |

* |

* |

|

* |

* |

* |

* |

* |

* |

* |

* |

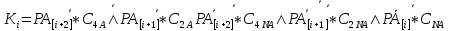

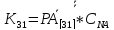

Из таблицы 3.11 получаем следующие формулы реализованные в базисе элементов, заданных согласно техническому заданию:

Рисунок 3.30 Изображение i-го разряда коммутатора КОМ

-

Синтез сумматора (sm)

Синтез сумматора SM (64р) на базе ИМ3.

Рисунок 3.31 Условно-графическое обозначение сумматор ИМ3

e=CAN

Ai=Ki

Bi=PCi

Рисунок 3.32 Схема 64-х разрядного сумматора

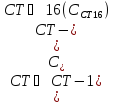

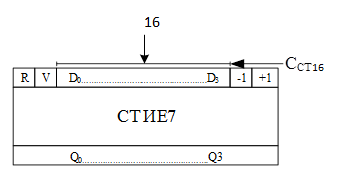

3.4.3 Синтез счетчика (сt)

Синтез счетчика СТ на базе ИЕ7.

Функциональная схема (ФС) счетчика СТ на базе ИЕ7 изображена на рисунке 3.28

Рисунок 3.28 Функциональная схема счетчика СТ на базе ИЕ7

Таблица синтеза счетчика CT имеет следующий вид (таблица 3.3):

Таблица 3.12 Таблица микроопераций счетчика CT

|

|

CCT16 |

CCT- |

Qt+1 |

R |

V |

+1 |

-1 |

Di |

|

1 |

* |

* |

Хранение |

0 |

1* |

1 |

1 |

* |

|

0 |

0 |

0 |

Хранение |

0 |

1 |

1 |

1 |

* |

|

0 |

1 |

Dec |

0 |

1 |

1 |

0 |

* |

|

|

1 |

0 |

Загрузка |

0 |

0 |

* |

* |

Ai |

|

|

1 |

1 |

* |

* |

* |

* |

* |

* |

R=0

Di=Ai

+1=1

3.4.4 Синтез схем сравнения (=0)

ZA =

ZA0

=

ZA1

=

…

ZA6

=

ZA7

=

ZA =

Рисунок 3.33 Схема ZA0

Синтез других схем сравнения выполняется аналогично ZA.