- •Оглавление

- •Вступление

- •Реализация cpu для выполнения команд сложения и вычитания алгебраических чисел

- •Начальные данные

- •Состав и описание структурной схемы cpu для выполнения команд add и sub

- •Описание алгоритма операций сложения и вычитания машинных чисел

- •Состав и описание узлов модуля операционного блока (моб) для выполнения операций сложения и вычитания машинных чисел

- •Реализация моб для выполнения операции деления чисел

- •Начальные данные

- •Обоснование алгоритма деления чисел

- •Реализация моб для выполнения операции умножения чисел

- •Начальные данные

- •Обоснование алгоритма умножения чисел

- •Состав и описание операционных элементов функциональной схемы (фс) моб для выполнения операции умножения чисел

- •Синтез по заданному элементному базису минимальных реализаций функциональных узлов моб для выполнения умножения чисел

- •Синтез регистров (ра, рв, рс)

- •Синтез регистра ра на базе к155тм8:

- •Синтез коммутатора (кома):

- •Синтез регистра ра

- •2)Синтез регистра рв на базе к155тм8:

- •Синтез коммутатора (комв):

- •Синтез регистра рb

- •Синтез регистра рc на базе к155тм8:

- •Синтез коммутатора (комc):

- •Синтез регистра рc

- •Синтез коммутатора (ком)

- •Синтез сумматора (sm)

- •3.4.3 Синтез счетчика (сt)

- •Синтез триггера знака (тзн)

- •Список литературы

Оглавление

Вступление 7

1.Реализация CPU для выполнения команд сложения и вычитания алгебраических чисел 8

1.1. Начальные данные 8

1.2. Состав и описание структурной схемы CPU для выполнения команд ADD и SUB 10

1.3. Описание алгоритма операций сложения и вычитания машинных чисел 14

1.4. Состав и описание узлов модуля операционного блока (МОБ) для выполнения операций сложения и вычитания машинных чисел 18

2Реализация МОБ для выполнения операции деления чисел 20

2.1 Начальные данные 20

2.2 Обоснование алгоритма деления чисел 20

3Реализация МОБ для выполнения операции умножения чисел 22

1Начальные данные 22

2Обоснование алгоритма умножения чисел 22

3Состав и описание операционных элементов функциональной схемы (ФС) МОБ для выполнения операции умножения чисел 27

3.1Синтез по заданному элементному базису минимальных реализаций функциональных узлов МОБ для выполнения умножения чисел 30

1Синтез регистров (РА, РВ, РС) 30

2Синтез коммутатора (КОМ) 43

3.4.2Синтез сумматора (SM) 45

3.4.3 Синтез счетчика (СT) 47

3.4.4 Синтез схем сравнения (=0) 48

3.4.5Синтез триггера знака (ТЗН) 49

Вывод 50

Список литературы 51

РЕФЕРАТ

РЕФЕРАТ

Страниц – , рисунков – 55, таблиц – 7, приложений – 0, ссылок − 5.

Этот курсовой проект посвящен архитектуре и реализации CPU, то есть реализация CPU для выполнения команд сложения и вычитания алгебраических чисел в машинном коде, реализация МОБ для выполнения операции деления чисел в машинном коде, реализация МОБ для выполнения операции умножения чисел.

Кроме этого выполнен синтез по заданному элементному базису минимальных реализаций функциональных узлов МОБ для выполнения умножения чисел.

СТРУКТУРНАЯ СХЕМА, МИКРОСХЕМА, БЛОК-СХЕМА АЛГОРИТМА, ОПЕРАТИВНАЯ ПАМЯТЬ, РЕГИСТР КОМАНД, АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО.

Вступление

Курсовой проект предназначен для разработки компьютера с аккумуляторной архитектурой с форматами команд RR, RX, с ОУ на базе закрепленных микроопераций. Вычислительное устройство должно содержать блоки для выполнения следующих операций: сложение/вычитание, умножение и деление. Все данные представлены как целочисленные значения. Для хранения данных, адресов или части исполнительных адресов, результатов предназначены MR (регистровая память) и MM (оперативная память).

-

Реализация cpu для выполнения команд сложения и вычитания алгебраических чисел

-

Начальные данные

Согласно техническому заданию заданы следующие параметры оперативной памяти (MM, MR) компьютера:

Ширина оперативной памяти (ММ) – 16М*64

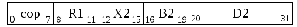

Рисунок 1.1 Ширина MM

Ширина регистровой памяти (МR) – 16М*32

Рисунок 1.2 Ширина MR

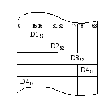

Способ адресации данных в памяти ММ – байтовый (адрес данных в ММ адрес их старшего бита), MR – регистровый (адрес данных в MR – номер четырехбайтового регистра MR).

Формат подачи операндов и результата int в ДК:

Рисунок 1.3 Формат подачи операндов и результата

Разрядность операндов 4 байта.

Состав и форматы команд ADD и SUB представлен на рисунке 1.4 (RR) и рисунке 1.5 (RX)

Рисунок 1.4 Состав и формат команды RR

Рисунок 1.5 Состав и формат команды RX

Команда RR:

Занимает 2 байта и состоит из следующих полей:

COP – восьмиразрядный код операции;

R1 – четырехразрядное поле адреса первого операнда, а также результат, находящийся в регистровой памяти MR;

R2 – четырехразрядное поле адреса второго операнда в регистровой памяти MR

Команда RX:

Занимает четыре байта и состоит из следующих полей:

COP – восьмиразрядный код операции;

R1 – четырехразрядное поле адреса первого операнда и поле результата;

X2 – четырехразрядный адрес индексной части исполнительного адреса второго операнда, который находится в MR;

B2 – четырехразрядный адрес базовой части исполнительного адреса второго операнда, находящегося в MR;

D2 – смещение в исполнительном адресе второго операнда.

Аисп = [X2]+[B2]+[D2]

Алгоритм выполнения команд ADD SUB:

RR: MR(R1) = MR(R1) * MR(R2)

RX: MR(R1) = MR(R1) * MM([X2] + [B2] + D2)

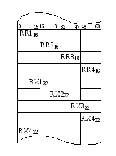

Распределение команд в памяти представлено на рисунке 1.6

Рисунок 1.6 Распределение команд в памяти

Распределение данных в памяти представлено на рисунке 1.7

Рисунок 1.7 Распределение данных в памяти