- •Оглавление

- •Вступление

- •Реализация cpu для выполнения команд сложения и вычитания алгебраических чисел

- •Начальные данные

- •Состав и описание структурной схемы cpu для выполнения команд add и sub

- •Описание алгоритма операций сложения и вычитания машинных чисел

- •Состав и описание узлов модуля операционного блока (моб) для выполнения операций сложения и вычитания машинных чисел

- •Реализация моб для выполнения операции деления чисел

- •Начальные данные

- •Обоснование алгоритма деления чисел

- •Реализация моб для выполнения операции умножения чисел

- •Начальные данные

- •Обоснование алгоритма умножения чисел

- •Состав и описание операционных элементов функциональной схемы (фс) моб для выполнения операции умножения чисел

- •Синтез по заданному элементному базису минимальных реализаций функциональных узлов моб для выполнения умножения чисел

- •Синтез регистров (ра, рв, рс)

- •Синтез регистра ра на базе к155тм8:

- •Синтез коммутатора (кома):

- •Синтез регистра ра

- •2)Синтез регистра рв на базе к155тм8:

- •Синтез коммутатора (комв):

- •Синтез регистра рb

- •Синтез регистра рc на базе к155тм8:

- •Синтез коммутатора (комc):

- •Синтез регистра рc

- •Синтез коммутатора (ком)

- •Синтез сумматора (sm)

- •3.4.3 Синтез счетчика (сt)

- •Синтез триггера знака (тзн)

- •Список литературы

-

Состав и описание узлов модуля операционного блока (моб) для выполнения операций сложения и вычитания машинных чисел

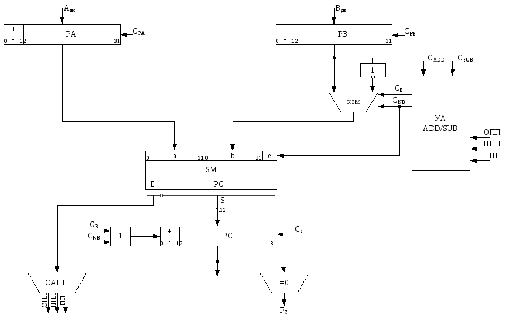

На рисунке 1.16 изображена функциональная схема модуля операционного блока (ФС МОБ) для выполнения операций сложения и вычитания машинных чисел в дополнительном коде (ДК).

Данная схема состоит из следующих элементов:

-

РА – регистр, предназначенный для хранения первого операнда;

-

РВ – регистр, предназначенный для хранения второго операнда;

-

РС – регистр, предназначенный для хранения результата;

-

SM – сумматор;

-

УА – локальный управляющий автомат для выполнения операций сложения и вычитания;

-

KOM – коммутатор инвертирования операнда В;

-

САПП – коммутатор переполнения с сигналами ОПП, ППП, ПП;

По сигналу СРА поступают данные из регистра РА на первый вход сумматора SM. Далее, по сигналу СРВ поступают данные на коммутатор КОМ и после выбора операнда по сигналам СB и CNB на второй вход сумматора SM. На е подается CNB. Сигнал о переполнении передается на Е. После чего происходит передача результата в регистр РС по сигналу СРС. Коммутатор САПП определяет ПП.

Рисунок 1.9 ФС МОБ для выполнения операций сложения и вычитания машинных чисел в ДК.

-

Реализация моб для выполнения операции деления чисел

-

Начальные данные

Согласно техническому заданию необходимо выполнить операцию деления по алгоритму «а» (2n/n) в ДК.

Операнды для выполнения примеров машинных операций:

А = 0101000101012 = 130110

В = 1001112 = 3910

Формат подачи операндов и результата int в ДК (рисунок 2.1 и 2.2)

![]()

Рисунок 2.10 Формат подачи первого операнда РА

Рисунок 2.11 Формат подачи второго операнда РВ и результата PD

-

Обоснование алгоритма деления чисел

Деление по алгоритму «а» выполняется так:

В начале алгоритма выполняется сравнение знаков делимого (А) и делителя (В). Если знаки совпали, то ЗН = 0, если нет, то ЗН = 1. Проверка на переполнение выполняется по старшему разряду РА после первого сложения РА и РВ. Если старший разряд РА равен 1, то ПП = 0, иначе ПП = 1.

После каждого сложения регистр РА необходимо сдвинуть влево на 1 разряд. Далее прибавляется регистр РВ (В или Впр высчитывается по формуле):

Ak

Ak

2 + Впр, если NAk

NB = 0

2 + Впр, если NAk

NB = 0

Ak+1 =

Ak

2 + В, если NAk

NB = 1

2 + В, если NAk

NB = 1

Впр =

Результатом сложения РА и пр = нке му аРВ является Акi. Примеры операции деления чисел по машинному алгоритму «а» представлены на рисунках 2.3

А = + 0101000101012 = + 130110 В = – 1001112 = – 3910

|

PD ← |

PA |

PB |

|

± хххххх |

± хххххх хххххх |

± хххххх |

|

ПП=0

1.1

1.10

1.100

1.1000

1.10000

1.100001 – 33 |

1.011001

0.111000 101000 0.100111

0.100111

0.100111

0.001110 000000 Ак6

0.000000 001110 Ак остаточ. 14 |

0.100111 (B) 1.011001 (Впр)

+В

+Впр

+В

+В

+В

+В

|

Рисунок 2.12 Пример операции деления чисел по алгоритму "а" в ДК (2n/n)

Проверка:

PА = 1301; PВ = 39

PD = PA/PB = 1301/39 = – 3310 = 1.1000012

1

1

0.010100

010101

0.010100

010101 0.010100

010101 |A|

0.010100

010101 |A| 1.011001

1.011001

1.101101

010101 Ак0

1.101101

010101 Ак0 1.011010

101010

1.011010

101010 0.100111

0.100111 0.000001

101010 Ак1

0.000001

101010 Ак1

0.000011

010100

0.000011

010100

1.011100

010100 Ак2

1.011100

010100 Ак2

1.011111

101000 Ак3

1.011111

101000 Ак3 0.111111

010000

0.111111

010000

1.100110

010000 Ак4

1.100110

010000 Ак4 1.001100

100000

1.001100

100000

1.110011

100000 Ак5

1.110011

100000 Ак5 1.100111

000000

1.100111

000000 0.100111

0.100111 →6р

→6р 1.100111

1.100111