Цилькер Б.Я., Орлов С.А. Организация ЭВМ и систем

.pdf

2 3 6 Глава 5. Память

бы арбитража при одномоментном обращении к одной и той же ячейке. В то же время есть и существенные отличия.

Первое состоит в том, что у микросхемы нет входов для указания адреса ячей ки, занесение и считывание данных производится в порядке их поступления через одну входную точку и одну выходную.

Второе отличие связано с необходимостью слежения за состоянием очереди. Для этого в микросхеме имеются регистры-указатели адресов начала и конца оче реди, а также специальные флаги, которые указывают на две ситуации: отсутствие данных (в этом случае блокируется считывание из микросхемы) и полное запол нение памяти (блокируется запись).

Обнаружение и исправление ошибок

При работе с полупроводниковой памятью не исключено возникновение различ ного рода отказов и сбоев. Причиной отказов могут быть производственные де фекты, повреждение микросхем или их физический износ. Проявляются отказы

втом, что в отдельных разрядах одной или нескольких ячеек постоянно считывается 0 или 1, вне зависимости от реально записанной туда информации. Сбой — это случайное событие, выражающееся в неверном считывании или записи инфор мации в отдельных разрядах одной или нескольких ячеек, не связанное с дефекта ми микросхемы. Сбои обычно обусловлены проблемами с источником питания или с воздействием альфа-частиц, возникающих в результате распада радиоактив ных элементов, которые в небольших количествах присутствуют практически

влюбых материалах. Как отказы, так и сбои крайне нежелательны, поэтому в боль шинстве систем основной памяти содержатся схемы, служащие для обнаружения и исправления ошибок.

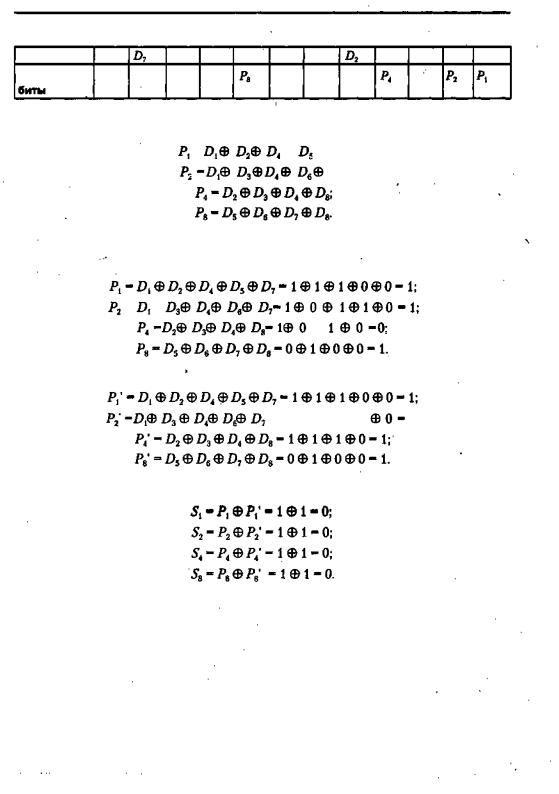

Вне зависимости от того, как именно реализуется контроль и исправление оши бок, в основе их всегда лежит введение избыточности. Это означает, что контроли руемые разряды дополняются контрольными разрядами, благодаря которым и возможно детектирование-ошибок, а в ряде методов — их коррекция. Общую схему обнаружения и исправления ошибок иллюстрирует рис. 5.15.

На рисунке показано, каким образом осуществляются обнаружение и исправ ление ошибок. Перед записью М-разрядных данных в память производится их об работка, обозначенная на схеме функцией «f», в результате которой формируется добавочный К-разрядный код. В память заносятся как данные, так и этот вычис ленный код, то есть (М + К )-разрядная информация. При чтении информации по вторно формируется К-разрядный код, который сравнивается с аналогичным ко дом, считанным из ячейки. Сравнение приводит к одному из трех результатов:

•Нe обнаружено ни одной ошибки. Извлеченные из ячейки данные подаются на выход памяти.

•Обнаружена ошибка, и она может быть исправлена. Биты данных и добавоч ного кода подаются на схему коррекции. После исправления ошибки в М-раз рядных данных они поступают на выход памяти.

•Обнаружена ошибка, и она не может быть исправлена. Выдается сообщение о неисправимой ошибке.

Обнаружение и исправление ошибок 2 3 9

Рис. 5.16. Иллюстрация кода Хэмминга для четырехразрядного слова

общее число единиц в каждой окружности было четным (см. рис. 5.16, б). Так, посколь ку окружность А содержит одну единицу, бит паритета для нее принимается равным 1. Теперь, если в результате ошибки изменится один из битов данных (см. рис. 5.16, в), это легко выявить. Путем проверки паритета обнаруживаются несоответствия в окружностях А и В. Для окружности Б несоответствия нет. Только один из семи сегментов присутствует в окружностях А и В и отсутствует в Б, и ошибка может быть исправлена за счет изменения бита в этом сегменте (см. рис. 5.16, г).

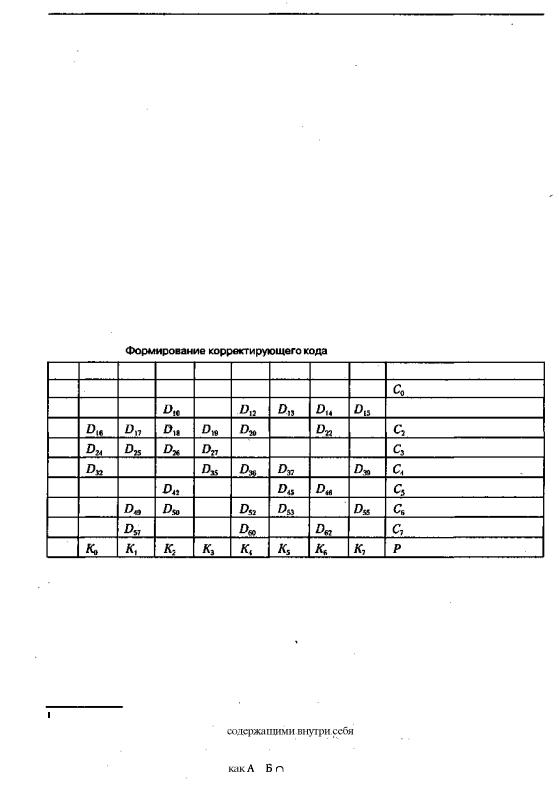

Для пояснения концепции, положенной в основу кода Хэмминга, построим код, обнаруживающий и исправляющий однобитовые ошибки в 8-разрядных словах (пример взят из [47]).

Сначала определим требуемую длину корректирующего кода. В соответствии с рис. 5.15, на вход схемы сравнения поступают два К-разрядных значения. Срав нение производится путем поразрядной операции «исключающее ИЛИ» (сложе ние по модулю 2) над входными кодами. Результатом является так называемое слово синдрома. В зависимости от того, было ли совпадение входных кодов или нет, соответствующий бит синдрома будет равен 0 или 1.

Слово синдрома состоит из К разрядов, то есть его возможные значения лежат в диапазоне от 0 до 2К - 1. Значение 0 соответствует случаю, когда ошибки не об наружено, остальные 2К - 1 случая свидетельствуют о наличии ошибки и указывают