- •Раздел I. Общие сведения о микроконтроллерах. Тема 1.1. Понятие микроконтроллера.

- •Тема 1.2. Типы микроконтроллеров.

- •Встраиваемые микроконтроллеры.

- •16-И 32-разрядные микроконтроллеры (микроконтроллеры с внешней памятью).

- •Цифровые сигнальные процессоры.

- •Тема 1.3. Архитектура процессоров. Cisc и risc процессоры.

- •Гарвард против принстона.

- •Тема 1.4. Типы памяти микроконтроллеров

- •Память программ

- •Память данных

- •Тема 1.5. Регистры микроконтроллера. Пространство ввода-вывода

- •Внешняя память

- •Раздел II. Аппаратные средства микроконтроллеров Тема 2.1. Корпуса устройств

- •Тема 2.2. Питание микроконтроллеров.

- •Потребляемая мощность.

- •Подключение питания.

- •Тема 2.3. Запуск микроконтроллера (сброс в начальное состояние). Тактирование системы.

- •Тактирование системы

- •Тема 2.4. Командные циклы. Программный счетчик. Алу. Командные циклы.

- •Программный счетчик.

- •Арифметико-логическое устройство

- •Тема 2.5. Сторожевые таймеры. Прерывания. Сторожевые таймеры.

- •Прерывания.

- •Раздел III. Средства обмена в микроконтроллерах. Тема 3.1. Таймеры.

- •Тема 3.2. Параллельный ввод-вывод данных. Преобразование логических уровней. Параллельный ввод-вывод данных

- •Преобразование логических уровней.

- •Тема 3.3. Последовательный ввод-вывод данных.

- •Асинхронный последовательный обмен.

- •Синхронный последовательный обмен.

- •Тема 3.4. Протоколы передачи данных. Протокол microwire.

- •Протокол spi.

- •Протокол i2с

- •Раздел IV. Микроконтроллеры семействаMcs-51 Тема 4.1. Фирмы-производители микроконтроллеров. Типовые характеристики семейства mcs-51.

- •Тема 4.2. Структура микроконтроллеров mcs-51 и функции выводов

- •Тема 4.3. Организация памяти и программно доступные ресурсы.

- •Тема 4.4. Синхронизация, магистральные циклы.

- •Тема 4.5. Методы адресации и система команд.

- •Методы адресации

- •Регистровая адресация.

- •Прямая адресация.

- •Косвенно-регистровая адресация.

- •Непосредственная адресация.

- •Система команд семейства mcs-51

- •Арифметические команды.

- •Логические команды.

- •Команды пересылки данных.

- •Команды работы с битами.

- •Команды передачи управления.

- •Тема 4.6. Система прерываний

- •Особенности запросов внешних прерываний.

- •Тема 4.7. Параллельные порты

- •Обновление данных в портах

- •Операции типа «чтение-модификация-запись»

- •Тема 4.8. Таймеры-счетчики

- •Тема 4.9. Последовательный порт

- •Синхронный обмен (режим 0)

- •Асинхронный обмен (режимы 1, 2, 3)

- •Обмен в многопроцессорных системах

Особенности запросов внешних прерываний.

По входам INT0#, INT1# могут приниматься сигналы запросов, активными значениями которых является либо низкий уровень входного сигнала, либо перепад «1»-«0». Тип активного значения определяется битами IT0, IT1 регистра TCON. При IТх = 0 запрос фиксируется по низкому уровню сигнала на соответствующем входе INTx#, а при ITx - 1 по перепаду.

Если запрос прерывания формируется перепадом сигнала на входе INTx#, высокий и низкий уровни сигнала должны удерживаться не менее одного машинного цикла каждый.

При запросе в виде низкого уровня сигнала активное значение должно удерживаться на входе до начала обработки данного запроса. Далее сигнал должен стать пассивным до завершения процедуры обслуживания.

Лекция № 6.

Тема 4.7. Параллельные порты

Все линии ввода/вывода микроконтроллеров семейства MCS-51 сгруппированы в несколько двунаправленных параллельных 8-разрядных портов. Микроконтроллеры типа 8051 АН имеют четыре параллельных порта Р0-Р3. Эти порты могут использоваться как для выполнения функций обмена данными (допуская при этом поразрядное программирование на ввод или на вывод), так и для выполнения альтернативных функций, таких как обращение к внешней памяти, прием запросов прерываний и другие.

При обращении к внешней памяти используются порты Р0 и Р2. Через порт Р0 выдается младший байт адреса, который должен быть зафиксирован во внешнем регистре, поскольку вслед за ним на линиях порта появляются данные для записи или чтения. Через порт Р2 выдается старший байт адреса. В микроконтроллерах типа 8051 и 8751 с внутренней памятью программ в условиях, когда внешняя память программ не используется, порты Р0 и Р2 могут служить для обмена данными как порты общего назначения. В микроконтроллерах с программируемой внутренней памятью программ порт РО используется для ввода или вывода байта кода при записи и верификации. Младший байт адреса при программировании и чтении внутренней памяти вводится через порт Р1, а старший байт адреса — через порт Р2.

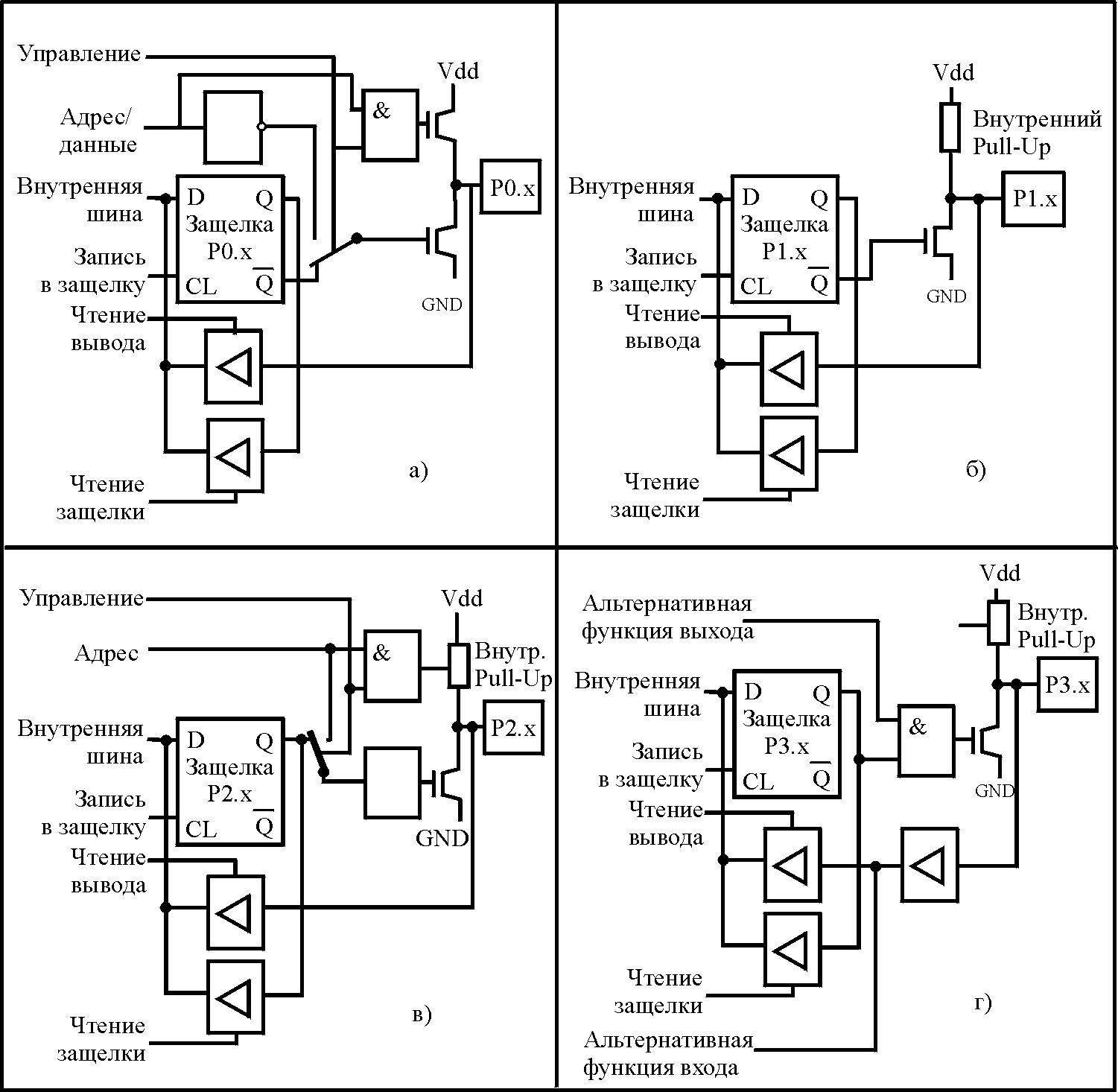

На рис. 4.10 приведены структурные схемы аппаратных средств, обслуживающих одну линию каждого из портов Р0-РЗ. Все линии параллельных портов имеют защелки (типа D-триггера), которые объединены в группы по восемь и рассматриваются как регистры специальных функций Р0-РЗ. Кроме защелки, каждая линия ввода/вывода имеет входной буфер и формирователь выходного сигнала. На рис. 4.10 видно, что на внутреннюю шину микроконтроллера может быть прочитано как состояние каждой из защелок, так и значения сигналов на внешних выводах. Часть команд микроконтроллера во время выполнения читают защелки (регистры портов), а другие — значение сигналов на линиях портов.

Для выполнения портом Р3 альтернативных функций в соответствующий разряд регистра порта должна быть записана «1». Во время обращения к внешней памяти во все разряды порта Р0 автоматически записываются «1», значения защелок порта Р2 не изменяются.

Чтобы вывести значение «0» или «1» на внешний вывод, необходимо записать это значение в соответствующий разряд регистра параллельного порта. Значение появится на внешнем выводе на фазе S1P1 первого машинного цикла следующей команды. Для использования линии порта в качестве входа, ее защелка должна содержать «1». При этом у портов Р1, Р2, Р3 соответствующая линия внутри подтягивается к уровню «1», но может быть внешним источником переведена в состояние «0». Из-за такого механизма порты Р1-РЗ называют «квазидвунаправленными».

Порт Р0 элементов постоянного подтягивания к уровню «1» не имеет. Запись «1» в защелку порта Р0 переводит соответствующую линию в высокоимпедансное состояние, поэтому этот порт является действительно двунаправленным. Верхний транзистор выходного формирователя открыт только при выдаче «1» на линию в качестве бита адреса внешней памяти. При работе порта Р0 на ввод/вывод данных его линии должны быть подтянуты к уровню «1» внешними резисторами.

Рис. 4.10 - Аппаратные средства, обслуживающие линии портов Р0..Р3

Поскольку функция записи «1» и функция чтения для выходного формирователя представляют собой одно и то же состояние с малым выходным током, для ускорения переключения внешних устройств выходные формирователи портов обеспечивают в течение первого машинного такта (S1P1-S1P2) увеличенный ток.