- •39. Логический элемент и-не: условное обозначение, таблица истинности. Принципиальная схема элемента транзисторно-транзисторной логики.

- •40. Логический элемент или-не: условное обозначение, таблица истинности. Принципиальная схема элемента эмиттерно-связанной логики.

- •41. Правила сложения чисел в двоичном коде. Одноразрядный и многоразрядный сумматоры.

- •42. Дешифратор: определение и область применения. Функциональная схема и таблицы истинности дешифратора с тремя выходами. Синтез дешифратора.

- •43. Мультиплексор: определение и область применения. Функциональная схема, логическое уравнение и синтез мультиплексора с двумя управляющими входами.

- •44. Демультиплексор: определение и область применения. Функциональная схема. Синтез демультиплексора.

- •49. Трехразрядный счетчик импульсов на синхронных счетных триггерах (схема и временные диаграммы).

- •50. Распределители импульсов.

- •38. Основные логические функции двух аргументов: операции и, или, не, и-не, или-не. Таблицы истинности.

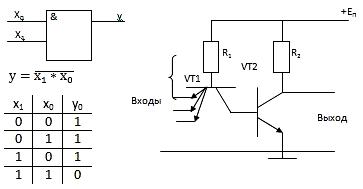

39. Логический элемент и-не: условное обозначение, таблица истинности. Принципиальная схема элемента транзисторно-транзисторной логики.

Операция «И» выполняется многоэмиттерным транзистором VT1, а транзистор VT2 осуществляет инверсию.

При наличии сигналов на всех входах (логическая единица) все эмиттерные переходы VT1 закрыты и не пропускают ток. Ток от источника питания через R1и коллекторный переход VT1 поступает на базу VT2, VT2 полностью открывается, его сопротивление стремится к нулю, и напряжение на выходе Uвых 0 (4 строка таблицы истинности).

Если хоты бы на одном входе сигнал отсутствует (логический ноль) соответствующий эмиттерный переход открыт, и ток от источника питания через R1 устремляется во входную цепь. VT1 обладает меньшим сопротивлением чем входное сопротивление VT2. Ток базы , VT2 стремится к нулю, , VT2 закрывается, его сопротивление стремится к нулю и напряжение на выходе и Uвых EП (логическая единица) (1-3 строки таблицы истинности).

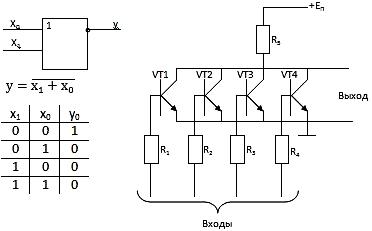

40. Логический элемент или-не: условное обозначение, таблица истинности. Принципиальная схема элемента эмиттерно-связанной логики.

Транзисторы работают в режиме ключа, напряжение на выходе либо Uвых 0 (транзистор полностью открыт) либо Uвых EП (транзистор закрыт).

Если Uвых 0 (логический ноль), если Uвых EП (логическая единица).

Если на всех входах сигналы отсутствуют (логический ноль) транзистор закрыт, ток через них не протекает и Uвых EП (логическая единица) (1 строка таблицы истинности).

Если хотя бы к одному входу подать сигнал (логическая единица) то соответствующий этому входу транзистор полностью откроется, его сопротивление будет близко к 0 и Uвых 0 (логический ноль) (2-4 строки таблицы истинности).

Любое устройство можно реализовать на элементах «ИЛИ-НЕ».

41. Правила сложения чисел в двоичном коде. Одноразрядный и многоразрядный сумматоры.

В двоичной системе счисления информация представляется последовательностью сигналов из 0 и 1, при этом число представляет собой многочлен по степеням числа 2.

![]()

n – число разрядов до запятой

а = 0 или а = 1

Отдельные цифры в записи представляет двоичный код который называется битами, а кодовое слово длинной 8 бит – байтом.

Пример: 13.75

Ц![]() елая

часть: последовательно делим на 2, и

остаток записывается в обратном порядке.

елая

часть: последовательно делим на 2, и

остаток записывается в обратном порядке.

Дробная часть: старшая цифра дробной части находится умножением на 2, если это произведение меньше 1,

то a-1=0, и если оно больше, либо равно 1, то a-1=1, т.е. равна целой части произведения. Следующая цифра a-2 определяется умножением дробной части полученного ранее произведения на 2 и выделение его целой части и т.д.

0.75*2=1.5 > 1 0.7511

a-1=1

0.5*2=1 = 1

a-2=1

13.751101.11

Комбинированные цифровые устройства – устройства, логическое состояния выходов которых определяются только комбинацией логических сигналов на входах.

Сумматор – комбинированное цифровое устройство, выполняющее арифметическую операцию сложения двух многоразрядных двоичных чисел, кодовые комбинации которых присутствуют на его информационных входах. Результат сложения отображается параллельным двоичным кодом на выходе сумматора.

П![]() оскольку

сложение двух многоразрядных чисел

всегда начинается с суммирования их

младших разрядов, рассмотрим простейшее

цифровое устройство, выполняющее

сложение двух одноразрядных чисел и

называемое полусумматором.

оскольку

сложение двух многоразрядных чисел

всегда начинается с суммирования их

младших разрядов, рассмотрим простейшее

цифровое устройство, выполняющее

сложение двух одноразрядных чисел и

называемое полусумматором.

Он имеет два информационных входа, куда поступает содержимое суммируемых разрядов, а так же два выхода. Первый из них представляет младший разряд результата и описывается суммой по модулю 2, а второй – обеспечивает сигнал переноса.