- •131. Метод эквивалентного генератора в разветвленных электрических цепях с одним нелинейным резистором (привести расчетный пример).

- •132. Операционные усилители. Обратные связи в усилителях.

- •Обратные связи в усилителях

- •133. Электронные генераторы (общие сведения, классификация). Автогенераторы синусоидальных колебаний lc-типа.

- •3. Электронные генераторы

- •3.1. Генераторы синусоидальных колебаний

- •3.1.1 Колебательный контур

- •3.1.2. Lc генераторы

- •134. Работа импульсного электронного генератора на примере симметричного транзисторного мультивибратора. Мультивибратор

- •135. Электронные импульсные и цифровые устройства. Триггер - бистабильная ячейка. Цифровые и импульсные электронные устройства

- •136.Сформулируйте законы коммутации, их физический смысл. Как вы экспериментально убеждались в соблюдении законов коммутации?

- •137. Понятия переходного и установившегося процессов. Причины, вызывающие переходной процесс.

- •138. Логические элементы цифровой техники.

- •140. Микроэлектроника как совокупность технологий

- •141. Интегральные микросхемы

135. Электронные импульсные и цифровые устройства. Триггер - бистабильная ячейка. Цифровые и импульсные электронные устройства

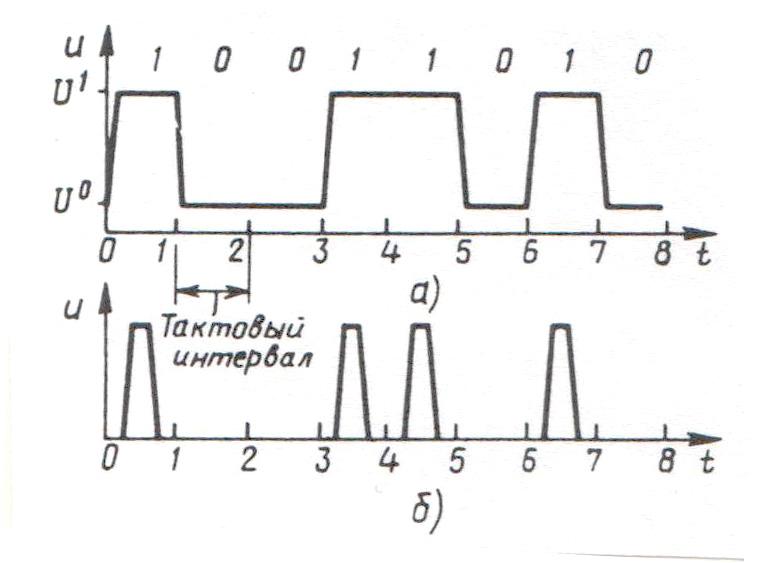

Устройства импульсной и цифровой электроники существенно отличается от устройств аналоговой электроники видом используемых сигналов (цифровые сигналы) и приёмами проектирования. Цифровой сигнал может принимать два значения (высокого уровня и низкого уровня). Устройства, работающие с цифровыми сигналами, называются цифровыми. Цифровыми сигналами сигналом представляются двоичные числа. Элементами сигнала являются нуль(0) и единица(1). Цифровой сигнал может быть потенциальным или импульсивным:

Элементами потенциального уровня (рисунок а)) являются потенциалы уровней u0 и u1. Каждый уровень остаётся неизменным в течении тактового интервала. Потенциалу u1 соответствует 1, потенциалу u0 — 0. Элементами импульсивного сигнала (рисунок б)) являются импульсы неизменной амплитуды и их отсутствие. Импульс представляет 1, а отсутствие импульса представляет 0. Обоим цифровым сигналам, изображённым на рисунке, соответствует двоичное число: 10011010. В природе практически все сигналы аналоговые, которые чувствительны к действию паразитных сигналов — шумов, наводок, помех. В отличии от аналоговых, цифровые сигналы, имеющие всего два разрешённых уровня, защищены от действий паразитных сигналов гораздо лучше. Для преобразования аналоговых сигналов в цифровые применяются специальные схемы, например АЦП.

Исходной структурной ячейкой, на основе которой строятся последовательностные логические схемы, является триггер. В основе структуры триггера лежит бистабильный элемент (имеет 2 устойчивых состояния).

3.1. RS–ТРИГГЕР

Рассмотрим

принцип действия элементарного триггера

(рис. 3.1, а). В произвольной паре

смежных ключей ![]() и

и ![]() выходное

напряжение транзистора

равно

входному напряжению транзистора

,

следовательно,

выходное

напряжение транзистора

равно

входному напряжению транзистора

,

следовательно, ![]() ,

таким образом, соединив вход транзистора

с

выходом

(штриховая

линия), мы не изменим устойчивого

состояния пары. Это устойчивое состояние

двухвариантно,

– заперт,

– открыт

(насыщен) и наоборот. Предложенная

структура и является бистабильной

ячейкой (триггером).

,

таким образом, соединив вход транзистора

с

выходом

(штриховая

линия), мы не изменим устойчивого

состояния пары. Это устойчивое состояние

двухвариантно,

– заперт,

– открыт

(насыщен) и наоборот. Предложенная

структура и является бистабильной

ячейкой (триггером).

|

|

а – последовательностная; |

б – симметричная |

Рис. 3.1 Структура элементарного триггера |

|

Если

изобразить триггер в виде самостоятельной

схемы (рис. 3.1, б), то ей присущи

графическая симметрия и перекрестные

обратные связи (ОС). Электрической

симметрии в схеме быть не может. Если

предположить, что транзисторы ячейки

находятся в симметричном состоянии,

т. е. ![]() ,

то например, увеличение тока коллектора

,

то например, увеличение тока коллектора ![]() ,

а следовательно, уменьшение напряжения

коллектора, будет усилено и через цепь

положительной обратной связи подано

на базу того же транзистора так, что его

ток коллектора еще больше увеличится.

Таким образом, транзистор

,

а следовательно, уменьшение напряжения

коллектора, будет усилено и через цепь

положительной обратной связи подано

на базу того же транзистора так, что его

ток коллектора еще больше увеличится.

Таким образом, транзистор ![]() переходит

в устойчивое насыщенное состояние

(открывается), а транзистор

переходит

в устойчивое насыщенное состояние

(открывается), а транзистор ![]() надежно

запирается. Этот процесс получил название

процесса регенерации.

надежно

запирается. Этот процесс получил название

процесса регенерации.

Принимая во внимание, что двух абсолютно одинаковых транзисторов быть не может, считаем наличие явления флюктуации в бистабильной ячейке обязательным. Поскольку знак флюктуации – величина случайная, то и результаты регенеративного процесса равновероятны.

При

помощи цепи управления триггера

(рис. 3.1, б), реализованной на

транзисторах ![]() и

и ![]() ,

с помощью внешних раздельных

сигналов

,

с помощью внешних раздельных

сигналов ![]() и

и![]() переводят

бистабильную ячейку в одно из двух

устойчивых состояний. Пусть в исходном

состоянии транзистор

заперт,

а транзистор

открыт

и насыщен, ключи

и

заперты.

Если открыть транзистор

переводят

бистабильную ячейку в одно из двух

устойчивых состояний. Пусть в исходном

состоянии транзистор

заперт,

а транзистор

открыт

и насыщен, ключи

и

заперты.

Если открыть транзистор

![]() ,то

состояние ключа

не

изменится. Если открыть транзистор

,

то напряжение

,то

состояние ключа

не

изменится. Если открыть транзистор

,

то напряжение ![]() уменьшится

до 0 и транзистор

закроется,

отпирая транзистор

и

вводя его в насыщение. После этого

ключ

теряет

свое управляющее воздействие.

уменьшится

до 0 и транзистор

закроется,

отпирая транзистор

и

вводя его в насыщение. После этого

ключ

теряет

свое управляющее воздействие.

Если

одновременно подать управляющие

сигналы

и

,

то ![]() ,

следовательно транзисторы

и

будут

заперты. По окончании воздействия

управляющих сигналов оба транзистора

откроются, и триггер окажется в равновесном

состоянии, из которого он может с равной

вероятностью перейти в любое из двух

устойчивых состояний, что недопустимо.

Таким образом, для RS триггера

характерна поочередная подача сигналов

на оба входа.

,

следовательно транзисторы

и

будут

заперты. По окончании воздействия

управляющих сигналов оба транзистора

откроются, и триггер окажется в равновесном

состоянии, из которого он может с равной

вероятностью перейти в любое из двух

устойчивых состояний, что недопустимо.

Таким образом, для RS триггера

характерна поочередная подача сигналов

на оба входа.

Условное

графическое обозначение RS–триггера

показано на рис. 3.2, а. В триггерах

выходы ![]() и

и ![]() всегда

находятся в противоположных

(комплиментарных) состояниях. Входы S (set)

и R (reset) рассматриваемого триггера

называют соответственно входом установки 1

и входомустановки 0. Для сигналов

,

будем

различать две совокупности

значений:

всегда

находятся в противоположных

(комплиментарных) состояниях. Входы S (set)

и R (reset) рассматриваемого триггера

называют соответственно входом установки 1

и входомустановки 0. Для сигналов

,

будем

различать две совокупности

значений: ![]() ,

, ![]() – значения

выходных напряжений, соответствующие

состоянию триггера в момент появления

входных сигналов

– значения

выходных напряжений, соответствующие

состоянию триггера в момент появления

входных сигналов ![]() и

и ![]() ;

; ![]() ,

, ![]() – соответствуют

состоянию триггера, полученному в

результате воздействия сигналов

и

.

Принцип работы RS-триггера иллюстрирует

его таблица истинности (табл. 3.1),

отражающая переход значений выходного

сигнала

к

.

При построении таблицы истинности

используют положения, вытекающие из

принципа работы триггера: если управляющие

сигналы на входах

и

отсутствуют,

то состояние триггера не меняется;

сигнал

– соответствуют

состоянию триггера, полученному в

результате воздействия сигналов

и

.

Принцип работы RS-триггера иллюстрирует

его таблица истинности (табл. 3.1),

отражающая переход значений выходного

сигнала

к

.

При построении таблицы истинности

используют положения, вытекающие из

принципа работы триггера: если управляющие

сигналы на входах

и

отсутствуют,

то состояние триггера не меняется;

сигнал ![]() устанавливает

на выходе

сигнал,

равный «1»; сигнал

устанавливает

на выходе

сигнал,

равный «1»; сигнал ![]() устанавливает

на выходе

уровень

логического «0»; совокупность входных

сигналов

,

приводит

к неопределенности состояния значения

.

устанавливает

на выходе

уровень

логического «0»; совокупность входных

сигналов

,

приводит

к неопределенности состояния значения

.

|

|

а – условное графическое обозначение; |

б – принципиальная схема |

Рис. 3.2 RS – триггер |

|

|

|

|

|

Режим работы |

0 |

0 |

0 |

0 |

Хранение |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

Установка 0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

Установка 1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

Х |

Запрещенное состояние |

1 |

1 |

1 |

Х |

RS – триггеры можно приобрести в готовом виде (в виде однокорпусных микросхем) или их можно собрать из логических элементов (рис. 3.2, б). Для этого полученную таблицу истинности триггера изображают картой Карно для сигнала (используя правила заполнения карты для частично определенной функции) и определяют логическую формулу функционирования RS – триггера:

![]()

Триггеры на интегральных логических элементах можно разделить на две основные группы – асинхронные и синхронные (тактируемые) триггеры.Асинхронные триггеры срабатывают в момент поступления сигналов на информационные входы. Рассмотренные ранее триггерные схемы можно отнести к асинхронным. В синхронных триггерах, кроме информационных импульсов, используют последовательности тактовых импульсов. Переход триггера в следующее состояние происходит только в момент прихода тактового импульса при наличии сигналов на информационных входах. Срабатывание синхронного триггера может происходить либо при воздействии фронта тактового импульса, либо его среза.

Рис. 3.3 Синхронный RS – триггер

Рис. 3.3 Синхронный RS – триггер

Рассмотрим

работу тактируемого фронтом RS – триггера,

условное графическое обозначение

которого показано на рис. 3.3. Наличие

синхронизирующего входа ![]() (clock)

вносит изменения в работу триггера,

временные диаграммы сигналов которого

иллюстрирует рис. 3.4. Тактовый

импульс

не

оказывает никакого влияния на состояние

выхода

,

когда на обоих входах установлен уровень

логического 0. Во время прохождения

импульса 1 триггер находится в режиме

хранения. В момент предварительной

установки входа

,

когда на вход подается логическая 1,

выход

остается

в прежнем состоянии

(clock)

вносит изменения в работу триггера,

временные диаграммы сигналов которого

иллюстрирует рис. 3.4. Тактовый

импульс

не

оказывает никакого влияния на состояние

выхода

,

когда на обоих входах установлен уровень

логического 0. Во время прохождения

импульса 1 триггер находится в режиме

хранения. В момент предварительной

установки входа

,

когда на вход подается логическая 1,

выход

остается

в прежнем состоянии ![]() ,

и только на фронте тактового импульса 2

происходит его переключение к 1.

Тактовые импульсы 3 и 4 не влияют

на состояние выхода

.

Во время прохождения импульса 3 триггер

находится в режиме установки 1, во

время прохождения импульса 4 – в

режиме хранения. Затем логическая 1

подается на вход

(предустановка

входа

).

На фронте импульса 5 происходит сброс

(очистка) выхода

путем

установки его в состояние 0. Во время

прохождения импульсов 5 и 6

триггер находится в режиме установки 0,

во время прохождения импульса 7 – в

режиме хранения. Подробное описание

работы синхронного RS – триггера

позволяет составить его таблицу

истинности и записать характеристическое

уравнение

,

и только на фронте тактового импульса 2

происходит его переключение к 1.

Тактовые импульсы 3 и 4 не влияют

на состояние выхода

.

Во время прохождения импульса 3 триггер

находится в режиме установки 1, во

время прохождения импульса 4 – в

режиме хранения. Затем логическая 1

подается на вход

(предустановка

входа

).

На фронте импульса 5 происходит сброс

(очистка) выхода

путем

установки его в состояние 0. Во время

прохождения импульсов 5 и 6

триггер находится в режиме установки 0,

во время прохождения импульса 7 – в

режиме хранения. Подробное описание

работы синхронного RS – триггера

позволяет составить его таблицу

истинности и записать характеристическое

уравнение

![]()

Рис. 3.4 Временные

диаграммы синхронного RS – триггера

Рис. 3.4 Временные

диаграммы синхронного RS – триггера