- •Рассмотрим пример построения схемы и оформления лабораторной работы:

- •Доказательство основных тождеств булевой алгебры

- •Задание

- •1. Используя пакет Electronics Workbench спроектировать схемы, соответствующие обеим частям тождества, и с помощью проведения анализа доказать тождество.

- •3. Лабораторная работа выполняется в соответствии с вариантами заданий, полученными у преподавателя (см. Таблицу ниже).

- •Счетчики.

- •1. Изучение структуры и алгоритмов работы многоразрядных счетчиков с произвольным основанием.

- •2. Обучение навыкам составления структурных схем счетчиков.

- •Мы будем рассматривать в основном циклические счетчики, которые

- •Двоичные счетчики.

- •1.1. Двоичные суммирующие счетчики.

- •1.2.Двоичные вычитающие счетчики.

- •2 Коэффициент пересчета.

- •3. Десятичные счетчики.

- •Счетчики по произвольному модулю.

3. Десятичные счетчики.

Десятичный счетчик состоит из нескольких подсчетчиков, соответствующих одному из десятичных разрядов. Такие подсчетчики называют декадными счетчиками (КСЧ=10).

Счетная последовательность декадного счетчика зависит от способа представления десятичного числа. Наиболее распространено представление десятичных чисел в двоичном коде 8-4-2-1.

Этот код представляет каждую десятичную цифру четырехразрядным двоичным числом от 0000 до 1001. Очевидно, что счетная последовательность декадного счетчика должна предусматривать переход от двоичного кода 1001 (цифры 9 в десятичной системе счисления) к коду 0000 (поскольку цифры 10 в десятичной системе счисления нет).

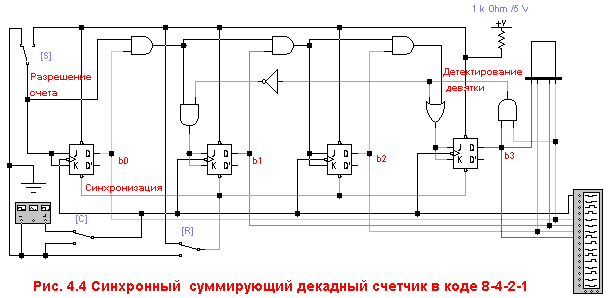

Рассмотрим схему синхронного суммирующего декадного счетчика в коде 8-4-2-1 (рис. 4.4):

Эта схема представляет собой модификацию двоичного суммирующего счетчика, при которой счетная последовательность прерывается после девяти. Для этого в счетчике предусмотрена схема детектирования девятки.

Модификация двоичного суммирующего счетчика заключается в следующем:

Введем вентиль “И” с входами сигналов Q0 и Q3 (что соответствует коду 1001), имеющий на выходе логическую единицу только при этой кодовой комбинации.

Введем вентиль “ИЛИ” перед входом Т3, обеспечивающий при кодовой комбинации 1001 на выходе декадного счетчика подачу логической единицы на вход ИЛИ и далее на вход Т3, следовательно, следующий синхроимпульс установит выход b3 в логический нуль.

Введем инвертор “НЕ” и вентиль “И” перед входом Т1, поэтому при кодовой комбинации 1001 на вход вентиля ”И” и далее на вход Т1 триггера будет подан логический нуль, следовательно, следующий синхроимпульс не изменит состояние на выходе “b1” (т.е. “b1” останется в нулевом состоянии)

Состояние выходов “b0” и ”b2” не изменяется в связи с доработками, т.к. их значения и при нуле и при десяти равны логическому нулю(0000 и 1010).

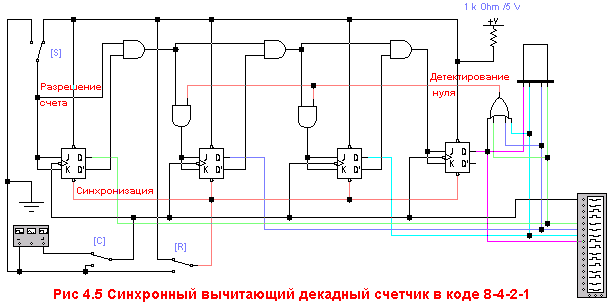

Аналогично можно построить схему синхронного вычитающего декадного счетчика в коде 8-4-2-1 (рис. 4.5):

4. n – разрядные счетчики.

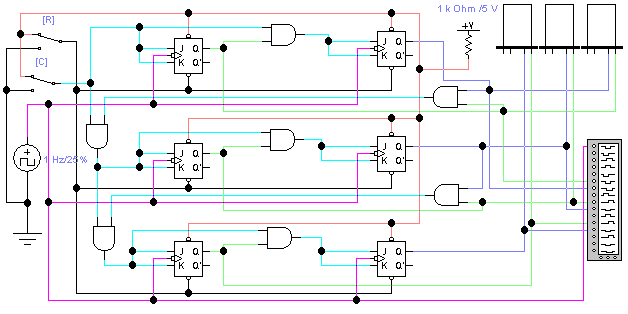

Рассмотренные декадные счетчики служат основой для создания n -разрядных счетчиков по модулю 10, которые строятся по схемам, используемым при построении двоичных счетчиков.

Разр.сч.

&

&

Р.с.

Д.

д.

C

Q10

Q11

Q12

Q1

3

Р.с.

Д.

д.

C

Q10

Q11

Q12

Q1

3

Р.с.

Д.

д.

C

Q10

Q11

Q12

Q1

3

Декада

1

Декада

2

Декада

3

Синхр.

В схемах n-разрядных счетчиков в каждой декаде сигнал “разрешение счета” должен быть равен единице тогда и только тогда, когда все предшествующие декады будут содержать девятки.

Таким же образом можно построить трехразрядный суммирующий счетчик в коде 4-2-1 по модулю 4 (рис. 4.6).

Рис. 4.6 Трехразрядный суммирующий счетчик в коде 4-2-1 по модулю 4.