- •Адреса 0000 – 1fff Занято 0000 – 07 ff Процессор Шина адреса Буфер шины адреса адреса

- •Старшие разряды адреса выборка выборка

- •Область озу Адреса 4000- 5fff Занято 4000 - 47ff

- •Типы интерфейсов вычислительных устройств. 16

- •2) Радиальные (типа звезда).

- •Архитектурные особенности построения пэвм. 25

- •Коп младший байт адреса старший байт адреса

Понятие о структурной модели ЭВМ 1

Любую техническую систему принято представлять ее моделью. В ЭВМ чаще всего в качестве модели применяют структурную схему.

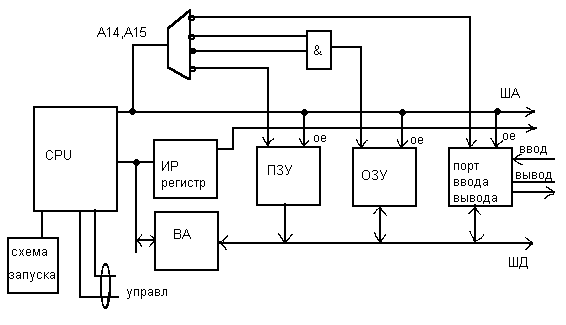

Структура ЭВМ отображает основные функциональные блоки и связи между ними. В зависимости от класса ЭВМ, ее сложности, структурное построение будет различаться. Например, типовая структура простейшего вычислителя (микроконтроллера) может быть представлена в виде (Рис.1).

Шина адреса ( ША)

Шина адреса ( ША)

Сигналы управления

Основа любого структурного построения ЭВМ – процессор (CPU), формирующий основные сигналы в схеме. Для обмена командами и данными используются две шины – шина адреса (ША) и шина данных (ШД). Структурные блоки оперативной памяти (ОЗУ) , постоянной памяти (ПЗУ), контроллеров внешних устройств подключены к этим шинам. Следует заметить, что шины адреса и данных можно рассматривать как некий «скелет» всей модели, неизменный для конкретного типа ЭВМ. Состав блоков при этом может изменяться, но способ их объединения – шины – неизменный. В основе построения структурной модели ЭВМ – функционально-модульный принцип. Каждый модуль отображается прямоугольником с соответствующими связями и представляет набор определенных функций. Структурная модель дает представление о составе вычислителя, но временные процессы и условия функционирования блоков ЭВМ в ней не определены.

Структурная схема считается обязательным документом при описания состава изделия, но не дает полных сведений о взаимодействии блоков между собой и непосредственной работы самих блоков. Это касается вопросов адресации, распределения адресного пространства, реализации системы прерываний, приоритетов и начальных загрузчиков. Часто для полного описания функционирования ЭВМ используют термин « архитектура». В технической документации нет такого понятия, он характерен для описания основных принципов работы вычислителя и охватывает как саму структуру, так и характеристики памяти, способы и виды предоставления информации, условия функционирования и т.д. Этот термин первоначально предложили с целью формального описания произвольной ЭВМ и для некоторых типов устройств такие представления были разработаны. Но поиск универсальной формальной модели произвольного типа ЭВМ не дал желаемого результата, а термин сохранился в своем значении.

Основные характеристики ЭВМ 2

На протяжении своего развития вычислительные машины претерпели большие изменения как в своем аппаратном составе, так и по основным характеристикам. Но перечень таких характеристик остался примерно постоянным. Причем эти характеристики нельзя распределить по приоритетам, все они важны и каждая говорит о тех или иных параметрах устройства. К числу основных относятся: операционные ресурсы, емкость памяти, быстродействие устройств, производительность, разрядность представления данных и адреса, надежность, стоимость.

Операционные ресурсы – это перечень действий (операций), которые может делать (выполнять) аппаратура ВК в плане обработки информации (исходных данных). В этот перечень прежде всего включается система машинных операций – список F={+,-,*,/,…}. Кроме того, это порождающая ее (систему операций) система машинных команд К={К1, …, КN}. В понятие операционные ресурсы включаются также способы представления информации в ЭВМ, способы представления чисел, текстов, логических значений. Чем шире перечень действий, чем шире многообразие способов представления данных – тем шире операционные ресурсы ЭВМ и, следовательно, возможности ВК в плане обработки информации.

Емкость памяти – очевидная техническая характеристика, которая характеризует вместимость памяти программ и данных ЭВМ. Единицы измерения – бит, байт В, килобайт КВ = 210В, мегабайт МВ = 220В, гигабайт ГВ = 230В, терабайт ТВ = 240В. Емкость памяти обычно кратна степени 2: Е = 2m, m – длина адреса.

Быстродействие измеряется в единицах времени. Показывает интервал времени в течении которого выполняется одна короткая операция, как правило, часть команды. Например, пересылка между регистрами, или сложение содержимого двух регистров. Быстродействие определяется элементной базой и частотой тактового генератора. Как правило, это время берется несколько большим, чем задержка при выполнении самой длинной операции в АЛУ процессора. Быстродействие определяет потенциальные

возможности устройств, указывает на верхнюю границу. Относится к отдельным блокам, а не к ЭВМ в целом. Так, быстродействие АЛУ характеризует скорость, с которой это устройство может выполнять операции: VАЛУ={V+, V-, V*, Vдел, …} Быстродействие зависит от времени выполнения операции: V=1/t – чем меньше время выполнения операции t, тем выше быстродействие. Быстродействие – это паспортная характеристика, указывается в документе на устройство либо в виде вектора скоростей V, либо в виде набора времен: t+, t-, t*, t/, … Следует отметить, что время выполнения команды tк зависит от многих факторов – быстродействия памяти (т.к. выборка команды и данных осуществляется из памяти, результаты также засылаются в память), от быстродействия АЛУ, а также организации ЭВМ. В простейшем случае

tк = tвк + tво + tалу + tзр,,,

где первое слагаемое определяет время выборки команды из памяти, второе – время выборки операнда(ов), третье – время выполнения операции в АЛУ, четвертое – время засылки результата операции. Быстродействие процессора для целочисленных операций принято измерять миллионами операций в секунду - MIPS или миллионами операций с плавающей запятой в секунду - MFLPS.

Память ЭВМ предназначена для хранения, записи и чтения информации. Быстродействие памяти принято характеризовать количеством операций чтения/записи в единицу времени. Память ЭВМ строится на базе ЗУ (БИС ОЗУ, ППЗУ). Итак, быстродействие каждого блока ЭВМ характеризует его потенциальные возможности. Быстродействие же ЭВМ в целом зависит от многих факторов: от быстродействия устройств, внутренней организации самого комплекса, от операционной системы, под управлением которой работает аппаратура, т.е. от организации вычислительных процессов и других факторов. Поэтому понятие быстродействие на ЭВМ не распространяется. Вместо него используется понятие производительность. Назначением ЭВМ является обработка информации, решение различных задач. Поэтому производительность естественно оценивать количеством задач в единицу времени. Но решаемые задачи разные. Как оценить производительность? Ответ на этот вопрос даёт метрическая теория: процессы в ЭВМ (ВК+ПО) описываются в виде некоторой математической модели, исследование которой и дает все ответы. В качестве такой модели, в частности, используется теория массового обслуживания. Она позволяет получить значения разных характеристик ЭВМ: времени решения задач Треш, производительности =1/Треш, загрузки процессора , времени ожидания в очереди и др. Следует отметить, что время решения конкретной задачи можно приближенно оценить по формуле: Треш=N(p1t1+p2t2+…). Здесь N – длина программы (количество команд), p1, p2, …-вероятности (частоты), а t1, t2 …- времена выполнения операций. Было замечено (Гибсоном, в частности), что эти вероятности обладают устойчивостью при решении задач разных классов.

Для сравнения различных ЭВМ по производительности обычно используют один и тот же набор программ, который испытывают на различных типах вычислителей. Например, Бенч-Марковские программы .

Разрядность представления данных. Принято считать данные в байтах 1,2,4,8 байтов. Полная разрядность данных в вычислителях называется словом. Аппаратная часть (АЛУ) выполняет операцию над полным словом одновременно, но алгоритмы вычислителей позволяют получать результаты над словами двойной и более длины. Плата за это – пропорциональное увеличение времени. Основным считают разрядность слова. Произвольный специализированный вычислитель может иметь разрядность отличную от стандартных – например 26 разрядов.

Адресная составляющая (разрядность адресуемой памяти). Разрядность адреса число адресных разрядов, показывающих максимальный объем памяти, к которой возможно адресоваться напрямую. При этом время доступа к памяти минимально. В микроконтроллерах это 16 разрядов (64К), в малых вычислителях 20 разрядов (1Мб), в вычислительных системах -24,32 разряда. Объем памяти вычислителя в общем случае не ограничен сверху. Разделяют лишь оперативную память , ОЗУ, имеющую непосредственный доступ (прямоадресуемая память), и ВЗУ – внешняя память, данные, из которой считываются последовательно.

Надежность ЭВМ – это свойство выполнять возложенные на нее функции в течение заданного отрезка времени. Надежность отлична от 100%. Дело в том, что элементы, из которых строится ЭВМ, рано или поздно перестают (отказываются) нормально работать. В результате отказа элемента работоспособность вычислителя нарушается. Отказы аппаратуры – случайные события, частоту которых принято характеризовать интенсивностью отказов , т.е. количеством отказов в единицу времени. Другая характеристика надежности – . наработка на отказ: T=1/ - это промежуток времени между двумя соседними (по времени) отказами. Для увеличения надежности ЭВМ используется резервирование аппаратуры, например, дублирование – двукратное резервирование, если недостаточно, то трехкратное и так далее.

Сигналы адреса, данных и управления 3

Функционирование ЭВМ определяется жесткой последовательностью сигналов адреса, управления и данных. При этом сигналы управления наиболее изменчивы. Они активизируют конкретные функциональные блоки и поэтому зависят от режима работы, от типа выполняемой команды. Сигналы адреса более постоянны. Источник этих сигналов – процессор. Они всегда однонаправлены от процессора и для того, чтобы увеличить их мощность (по току) стремятся ША формировать через буфер (например, регистр). Если такой регистр имеет по выходу три состояния, ЭВМ может работать и в режиме прямого доступа к памяти (ПДП). Тогда источником адреса становится контроллер ПДП, а регистр переводится в третье состояние, отключая процессор от шины. Разрядность шины адреса – типовая, в контроллерах 16,20,24,32.

В общем случае необязательно все разряды адреса передавать через буфер. В буфере фиксируются те разряды, которые необходимо сохранить в течение всего цикла обмена. На временной диаграмме сигналы адреса показывают следующим образом ( Рис.2).

Поскольку ША многоразрядная, а приводится лишь одна линия

( один разряд), двойная линия на диаграмме показывает, что адрес на различных разрядах может быть «1» и «0» одновременно.

Ш

ина

адреса

ина

адреса

адрес 1 адрес 2 адрес 3

t

Шина данных

данные 1 данные 2 данные 3 t

Сигнал управления

t

Сигналы данных также представлены шиной (ШД). Ее разрядность 8, 16, 32. В отличие от адреса, эта шина двунаправлена. В качестве буфера данных применяют двунаправленные регистры и шинные фор

мирователи типа АП (589АП2) и элементы ВА (588ВА1). Сигналы данных на временной диаграмме отображаются в интервале текущего адреса. Поскольку ШД не ограничена по длине, следует всегда обращать внимание на нагрузочную способность буферных элементов. И в случае ее невыполнения выбирают схему с буфером Буферные элементы в шине данных обязательны.

Шина управления (ШУ) объединяет достаточно условно сигналы для активизации (включено, выключено) отдельных функциональных блоков. Каждый такой сигнал индивидуален и объединяют их в шину только для упрощения структурной схемы. Представленная структура (Рис.1) является трехшинной, поскольку сигналы управления объединены в самостоятельную шину.

Последовательность прохождения сигналов по шинам следующая (Рис.1). Процессор выставляет на ША текущий адрес. По этому адресу из ПЗУ по сигналу чтения на ШД передается код операции (КОП). Буфер данных при этом настроен на прием. Поэтому КОП фиксируется в регистре команд процессора. Процессор, приняв КОП, расшифровывает его и настраивает внутренние функциональные блоки и связи между ними на выполнение текущей операции. По сигналам синхронизации во внутренних регистрах процессора фиксируется преобразованная информация. Если текущая команда выполнена, процессор выставляет следующий адрес, по которому читается новый КОП и процесс выполнения команды повторяется. В сложных командах после чтения из ПЗУ кода операции может производится дальнейшее выполнение текущей команды: чтение байтов адреса, данных или запись данных в ОЗУ.

2.2.Организация магистралей. Распределение ресурсов в ЭВМ 4

Современные вычислители строятся по магистрально-модульному принципу (ММП). Он подразумевает, что обмен информацией производится между двумя модулями: источником и приемником. При этом из большинства модулей только источником может быть ПЗУ ( память команд). Процессор, ОЗУ, устройства ввода-вывода информации могут быть как источниками, так и приемниками.

Связь между источником и приемником осуществляется по магистрали данных (ШД). Адресные же сигналы необходимы для выделения второго блока: первый – процессор, а второй – ячейка (внешний регистр, ОЗУ, ПЗУ). Простейшая конструкция модульного типа представляет печатную плату с системой шин, на которых помешены розетки для подключения функциональных блоков. Если поменять расположение блоков в розетках, то изменится адрес этих блоков. В универсальных системах этот способ приводит к изменению приоритетов. Но при этом следует учитывать, что сигналы управления также следует коммутировать. Помимо двухшинной организации, существуют вычислители с совмещенной шиной адреса и данных. (Рис.3). Сигналы адреса и данных по шине передаются последовательно, один за другим.

Процессор

Регистр

Регистр

Регистр

ОЗУ

ПЗУ

Контроллер

а).

Ш А/Д

адрес1 данные 1 адрес 2 данные2 адрес3 t

б)

Рис.3. Организация ЭВМ с мультиплексированной шиной (а) и временная диаграмма передачи сигналов по шине адреса / данных (б).

При таком способе время цикла возрастает, но аппаратные затраты (площадь под металлические проводники) меньше. Эта организация больше приспособлена к модульному подходу: каждая розетка имеет связь со всеми разрядами адреса и данных и всеми сигналами управления. Отсюда замена модулей в розетках не требует изменения в коммутации сигналов управления. Таким образом, это более удобно для модульного построения.

С появлением персональных ЭВМ увеличилось и число магистралей используемых для передачи сигналов в ЭВМ. Так, для первых ПЭВМ, типа ХТ, характерна следующая структура (Рис. 4).

диаграмма передачи сигналов по шине адреса / данных (б).

Процессор с сопроцессором объединяются по локальной шине (LB), т.е. все сигналы доступные главному процессору находятся и в сопроцессоре. Локальная шина через буферы связана с системной шиной (SB), которая объединяет остальные функциональные блоки. Эти блоки распределены по функциям: память – шина МB, объединяющая модули памяти, шина расширения ХB – через которую подключены внешние устройства.

Процессор

Буфер шины

MB

Буфер шины

ОЗУ

ОЗУ

Сопро-цессор

Буфер шины

КЭШ - память

ВУ1

ВУ2

LB SB

Рис. 4. Разделение локальной и системной шин в вычислителе типа РС-ХТ

Наличие буферов между шинами позволяет разделять локальную шину или процессор с сопроцессором от системной шины SB, выделять шину расширения.

Развитие шинной организации в ЭВМ, распределение сигналов по соответствующим шинам, привело к появлению архитектуры открытых систем( ОС).

Распределение ресурсов в ЭВМ

Главный ресурс в ЭВМ – это адресное пространство памяти. Причем памяти, к которой возможен доступ по шине адреса. Поскольку процессор может обмениваться информацией в произвольный момент времени только с одним функциональным блоком ( ПЗУ, ОЗУ, устройства ввода-вывода), адресное пространство делится на соответствующие области. Когда процессор выставляет на шину адреса текущее его значение, адресный дешифратор позволяет работать лишь одному блоку. Тому, в область адресов которого попадает текущий адрес. На вход дешифратора поступает несколько старших разрядов адреса (Рис.5).

Адреса 0000 – 1fff Занято 0000 – 07 ff Процессор Шина адреса Буфер шины адреса адреса

П З У

О З У

Старшие разряды адреса выборка выборка

Дешифратор

DC

Дешифратор

DC

Рис.5 Адресная выборка блоков в ЭВМ.

В произвольный момент времени один из выходов дешифратора активен, он и разрешает обмениваться с процессором информацией соединенному с ним блоку. Согласно такого подхода, адресное пространство следует поделить на соответствующие области. Заметим, что часто для увеличения области памяти под ОЗУ несколько выходов дешифратора объединяют по схеме «или». Такое деление отображается в карте распределения адресов между блоками ЭВМ. Пример распределения адресного пространства приведен на рисунке 6. В карте показаны области памяти, отведенные для BIOS, ПЗУ, ОЗУ, двух внешних устройств (ВУ). Объем всей памяти – 64 Кб, из которого для ОЗУ отведено 32Кб, для ПЗУ –4Кб, под BIOS – 2Кб, под внешние устройства – по 2 Кб. Как видим, распределение с помощью двоичного полного дешифратора далеко неоптимальное, поскольку он позволяет выделять лишь одинаковые области памяти. И для лучшего варианта распределения необходимо использовать программируемые логические матрицы (ПЛМ) или двухступенчатые двоичные дешифраторы.

Конечный

адрес -FFFF

Область ОЗУ

Область ОЗУ

Область ОЗУ

Начальный адрес

8000

Область озу Адреса 4000- 5fff Занято 4000 - 47ff

Область ВУ 2

Адреса

6000 – 7FFF Занято

6000 - 67FF

Адреса

0000 – 1FFF Занято

0000 – 07 FF

Адреса

2000 – 3FFF Занято

2000 – 2FFF

Область

ПЗУ

Область

ПЗУ

Область BIOS

0000

Рис. 6. Пример распределения адресного пространства контроллера

Процессоры в эвм. структура гипотетического процессора. 5

Типы процессоров. Операционная и управляющая часть.

Любая вычислительная машина имеет в своей структуре процессор как основную составляющую часть. Многообразие ЭВМ в основном определяется организацией процедуры обработки. Принято вычислительные машины разделять в зависимости от числа процессоров: одно и много процессорные. На сегодня это деление условно, поскольку современные микропроцессоры имеют сложную организацию, включающую несколько логических процессоров. По нормам десятилетней давности они должны быть отнесены к многопроцессорной структуре. Поэтому для определенности будем считать за один процессор один корпус, ориентируясь на конструктивное выполнение.

По функциям процессоры делятся на универсальные и специализированные. Первые выполняют типовой набор операций и любая задача может быть практически реализована. Вторые ориентированы по системе команд на выполнение редких специальных операций дополнительно к универсальным. Задача таких структур – оптимизировать время выполнения команд. Большинство процессоров имеют универсальную систему команд.

Простейшая структура универсального процессора предусматривает операционное устройства (сумматор), два основных регистра и регистр расширения. Последовательно передавая информацию, такая структура позволит выполнить любую операцию через сложение/вычитание и последовательное преобразование.

Специализированные схемы включают «быстрые» преобразования за счет аппаратных средств. По способу преобразования информации: последовательные схемы, параллельные процессоры, векторные и матричные процессоры, однородные вычислительные схемы (транспьютеры). Последовательные структуры – универсальные, обычно в процессорах последующая команда выполняется после окончания предыдущей. Режим работы не влияет на последовательность выполнения команд.

Параллельные процессоры, как правило, - многопроцессорные структуры, в которых возможно выполнение операций над частями операндов: одни схемы преобразуют младшую частью, другие среднюю, третьи - старшую частью слова данных, либо над несколькими операндами . Но разделение операнда на части сегодня уже не используется. Этот подход остался на микропрограммируемых секциях, поэтому современные параллельные процессоры обрабатывают операнды одновременно, но под управлением различных команд. Синхронизация во времени, выборка требуемых операндов – задача довольно сложная, она решается усложнением программы. Это направление на сегодня успешно развивается.

Векторные процессоры – параллельное включение нескольких процессоров, как правило, для работы с комплексными переменными, где каждый процессор обрабатывает свою координату. От параллельного включения отличается тем, что задача одна, а в предыдущем случае задачи могут быть различными. Их можно отнести к специализированным процессорам по особенностям используемых команд.

Матричные процессоры сочетают в себе параллельный ряд модулей и конвейер – несколько слоев последовательного преобразования. Структура используется для ускорения выполнения сложных преобразований (вектора, матрицы и т.д.). По своему назначению относятся к специализированным структурам.

Однородные вычислительные секции. Повышения скорости преобразования информации привело к разработке однородных вычислительных сред (ОВС). ОВС имеет матричную структуру процессора, в которой каждая ячейка выполняет одну несложную, но перестраиваемую операцию. Чтобы определить эти ячейки, в структурах устанавливают связь каждой ячейки со всемисоседними. На сегодня в качестве ячеек ОВС применяют транспьютеры – вариант микропроцессора с небольшим АЛУ, но с множеством коммутаторов, позволяющих быстро передавать операнды в другие ячейки.

Процессоры также делятся по условиям эксплуатации на устройства широкого применения и специализированные. Помимо рассмотренных параметров, каждый процессор имеет характеристики ЭВМ (разрядность, объем адресуемой памяти, тактовую частоту).

6

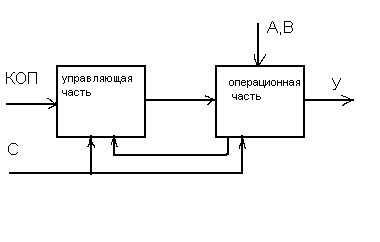

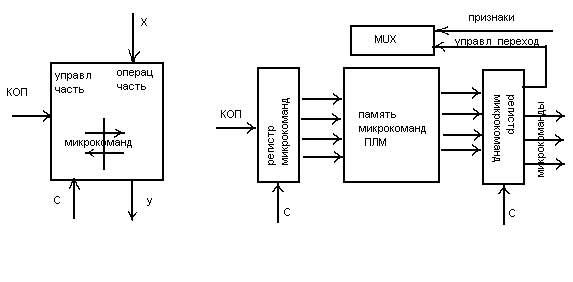

Структуру любого процессора, как цифрового автомата, можно представить состоящей из двух частей: управляющей и операционной.

Рис.7. Две составляющих части процессора

Операционная часть выполняет непосредственно преобразования операндов А и В, формируя выходной сигнал Y. Управляющая часть из КОП формирует множество управляющих сигналов, каждый из которых отвечает за настройку своего узла в операционной части. Эти сигналы принято называть микрокоманды, поскольку на каждый период сигнала синхронизации они свои. Управляющая часть – цифровой автомат, который в зависимости от входного кода операции последовательно формирует микрокоманды. Его структура на сегодня реализована преимущественно на ПЛМ.

Операционная часть помимо выходных сигналов Y по окончании каждой команды посылает в управляющую часть специальные сигналы, называемые «признаки» (флаги). Эти сигналы необходимы для учета условий ветвления и, как правило, отражают наиболее характерные качества результата:

1) Равенство результата нулю, Z=1,

2) Сигнал выходного переноса, С=1,

3) Состояние старшего разряда S=1.

Помимо трех основных признаков встречаются и дополнительные: переполнение (OVR), четность результата (Р), перенос из одной тетрады кода результата в другую (АС).

Признаки призваны помогать пользователю в управлении процедурой вычисления. В зависимости от типа процессора соотношение аппаратных составляющих управляющей части и операционной различно.

Полный цикл работы процессора

Работу процессора можно рассматривать относительно его синхросигналов, т.е. разделить время выполнения команды на составляющие. Для пояснения работы процессора вводят понятия «такт» и «цикл».

Такт – это интервал времени между двумя соседними тактовыми сигналами (период синхросигнала). Величина такта строго постоянна для всей вычислительной системы и определяется из наибольшей задержки при выполнении микрокоманды. Наибольшая задержка определяется временем преобразования в АЛУ и временем записи в регистр хранения. Тактовый генератор, определяющий этот интервал, может иметь и меньшую частоту, но процессор при этом простаивает.

Время цикла – интервал времени за который процессор из памяти считает или запишет туда операнд, при этом выполняются микрокоманды анализа, сохранения результата и анализа внешних сигналов. В интервале одного цикла состояние шины адреса не изменяется. Принято команду процессора представлять набором различных циклов: выборка команд, чтение памяти, запись в память, цикл прямого доступа к памяти, цикл обработки прерываний и т.д. Такое деление принято в системах с командами типа IBM. В DEC- структуре различают три типа основных циклов: ввод, вывод, ввод – модификация – вывод.

Приведем пример цикла для микропроцессора типа К580ВМ80. Первый цикл – выборка, с нее начинается выполнение любой команды.

В первом такте любой операции процессор выставляет на шину адреса адрес текущей команды (или адрес, определенный на предыдущем шаге). Содержимое выбранной ячейки памяти ( КОП) по шине данных поступает в процессор и фиксируется в регистре команд. Код операции расшифровывается во втором такте с учетом входных сигналов управления режима процессора. Если работа разрешена, процессор продолжает выполнять команду, настраивает внутренние коммутаторы и связи между блоками на пересылки данных. Команда выполняется в течение 3,4,5 тактов. Фактически для выполнения команды достаточно одного такта. Дополнительные такты используются для записи результатов или чтения с шины данных. Таким образом,. длительность цикла выборка для различных команд изменяется от 3 до 5 тактов. В первом такте каждого цикла устройство управления процессора выставляет на шину данных слово состояния процессора (ССП). Это восьмиразрядный код, несущий информацию о типе цикла. Любая команда начинается с выборки, поэтому в первом цикле всегда устанавливается код выборки. В последующих циклах работы процессора слово состояния принимает соответствующие значения. Этот код используют для получения сигналов, управляющих внешними по отношению к процессору схемами – ОЗУ, ПЗУ и так далее. Длительность цикла можно наблюдать по состоянию младшего разряда на шине адреса. Кроме того, процессор в начале каждого цикла формирует синхросигнал, используемый для записи текущего адреса в буфер адресной шины.

ПРИНЦИПЫ ПРОГРАММНОГО УПРАВЛЕНИЯ 7

Считают, что начало организации вычислителей на основе цифровых автоматов было положено принципами программного управления. На начальном этапе эти принципы считались незыблемыми, хотя сегодня некоторые положения могут трактоваться необязательными. Выделяют пять основных принципов программного управления:

1) Информация кодируется в двоичной форме и разделяется на единицы информации, называемыми словами. Известна троичная (SD) - система, но она не нашла широкого применения в вычислителях.

2) Разнотипные слова подразделяются по способу использования, а не по системе кодирования: данные, адреса и коды команд осциллографом не различимы. Мы их различаем местом нахождения.

3) Слова информации размещаются в ячейки памяти машины и идентифицируются по номеру ячейки памяти.

4) Алгоритм выполнения задачи представляется в форме последовательности управляющих слов, которые определяют операции и слова информации. Такую последовательность называют кодами.

5) Программа – это последовательное выполнение команд в порядке, обозначенном алгоритмом. Иногда программу определяют как алгоритм, представленный в терминах команд. Каждая операция (команда) может преобразовывать операнды различного уровня сложности. На сегодня различают три уровня.

1) Микрокоманды: элементарное преобразование операнда. Например: занесение с входа в память, пересылка из одного регистра в другой, вывод содержимого регистра на выходных данных. Главное отличие микрокоманды – она выполняется за один такт синхросигнала. Поскольку у тактового импульса два фронта, возможно в рамках микрокоманды «протолкнуть» информацию» через два регистра. На большее фронтов уже не хватает. Обычно микрокоманда - составная часть операции. За время выполнения любой микрокоманды производится два действия: фиксации входного операнда в регистре процессора, момент фиксации – фронт синхросигнала, и самого преобразования операнда с фиксацией результата по срезу синхроимпульса. Определенная длительность синхросигнала необходима чтобы:

а) закончить переходные процессы при записи в регистр,

б) чтобы результат преобразования входных операндов комбинационной схемой был сформирован на входе выходного регистра в истинном виде.

Современная микрокоманда, как правило - , элементарная операция АЛУ типа сложения. Микрокоманда присутствует в любом вычислителе, хотя часто пользователи их не выделяют.

2) Команды часто приравнивают к операциям. Например, сложение и вычитание. Действительно логически проще мыслить операцией. Поэтому это наиболее распространенный вид управления, большинство современных вычислителей основано на командном уровне управления. Любая команда включает в себя множество микрокоманд, число которых достигает нескольких десятков. При этом не обязательно помнить все микрокоманды текущей команды. Их последовательность формируется автоматически по жесткой программе.

3) Макрокоманды или тэги. Макрокоманды появились в силу того, что сложные процедуры требовали большого числа команд, обращений в память. Переход на макрокоманды сокращал число обращений в память, повышая тем самым скорость выполнения. В любой ситуации макрокоманды так же состоят из последовательности микрокоманды.

В зависимости от вида управления информация, хранящаяся в памяти, представляется в виде формата микрокоманды, команды, макрокоманды. Принято изображать любой формат прямоугольником с соответствующей длины с указанием начального и конечного разрядов информации. Если принята байтовая система (слово), формат разделяется на байты. Такое деление необходимо, чтобы каждую команду можно было осмыслить, понять по ее формату структуру операции (состав) (Рис.7). В приделах формата микрокоманда представляется полями, поэтому это деление может быть связано с выполняемой микрокомандой. Первым словом (байтом)

Код операции

Младший байт адреса Старший байт

адреса

0 7 8 15 16 23

Рис.9 Пример формата команды прямой адресации

любой команды всегда идет код операции (КОП). За КОП могут следовать адреса – первым младший, затем старший байты; аналогично представляются данные. Если команда сложная, КОП размещается не в одном байте, последующие байты КОП называются постбайтами. Команда, какой бы сложности она не была, хранится в ячейках ПЗУ.

Устройства управления с жесткими связями 8

Большинство современных процессоров ориентировано на командный тип управления. Структура такого процессора включает управляющую часть и операционную(Рис.8 (а)). На вход управляющей части поступает КОП, который расшифровывается в сигналы микрокоманд. С каждым тактом эти сигналы обновляются, поскольку для каждой команды необходимо множество микрокоманд. В свою очередь, по результатам текущих операций из операционной в управляющую поступают признаки (флаги), изменяющие последовательность микрокоманд. Управляющая часть по своей структуре считается цифровым автоматом, структура такого автомата обычно имеет вид (Рис.8 (б)).

(а)

(б)

(а)

(б)

Рис.10 Структуры автоматов с программным (а) и микропрограммным (б) управлением

Структура называется с жестким управлением, поскольку пользователь не может сам изменить таблицу ПЛМ. В результате каждой операции на входе соответствует строго своя последовательность микрокоманд. На предприятии можно поменять кодировку, и скорость выполнения операций изменяется без изменения кодов команд. Проводились опыты по применению перепрограммирования матричных структур в качестве устройств управления микропроцессором. Основной недостаток тех структур – большая задержка в элементах матриц, что приводило к увеличению времени выборки. В то же время получаемая гибкость, возможность изменения микрокоманд была не большой. Необходимость в таком изменении для схем широкого применения не нужна, следовательно, такие структуры целесообразны, если универсальный микропроцессор используется как специализированный вариант спецпроцессора.

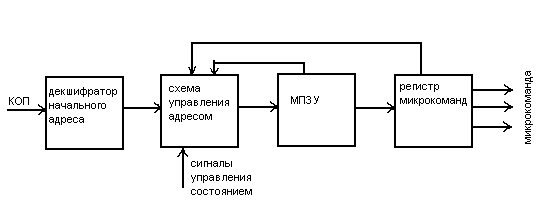

Микропрограммный принцип управления 9

Микропрограммный способ управления является основным при разработке специализированных схем и в системах на основе секционированных микропроцессоров. В его основе лежит введение промежуточного преобразования кода команд в микрокоманды с использованием схем памяти. Управление на уровне команд – это выборка из памяти команд кода операции. Блок управления процессора из КОП формирует последовательность микрокоманд. Такая последовательность микрокоманд должна иметь возможность изменения. При записи кодов микрокоманд в промежуточную память смена содержимого памяти эквивалентна замене микрокоманд.

С приходом КОП ( Рис.9.) дешифратор начального адреса микрокоманды (ПЛМ) формирует адрес, по которому из памяти микрокоманд необходимо считать первую микрокоманду. Считанный код микрокоманды уходит

Р ис.

11. Структура простейшего устройства

микропрограммного управления

ис.

11. Структура простейшего устройства

микропрограммного управления

на управление различными узлами операционной части, вместе с этим этот код содержит признак смещения, по которому определяется адрес следующей микрокоманды. В следующем такте по новому адресу из памяти микрокоманды читается новое содержимое. И так до тех пор, пока в микрокоманде не появится признак конца команды, этот признак увеличит счетчик адреса текущей команды на 1, и из ПЗУ прочитается следующий КОП. Такой подход был предложен в 50-х годах. На сегодня схемы ППЗУ типа РТ, РР, РФ обеспечивают удобство в применении такого способа. Обратная связь из регистра микрокоманд в схему управления адресом микрокоманды обеспечивает изменение текущего адреса микрокоманды. Связи жесткие и они определяют последовательность в выполнение микрокоманд. Для операций ветвления необходимы адреса переходов. Эти адреса считываются из МПЗУ и совместно с управлением (смещением) изменяют следующий адрес микрокоманды. Для анализа текущего состояния процессора на схему управления адреса из операционного блока поступают сигналы управления состоянием – признаки (флаги), формируемые другими устройствами. В результате адрес следующей микрокоманды зависит от трех групп сигналов: 1) смещения 2) адреса перехода, если он используется, 3) признаков (флагов) из операционного блока. Запаздывание смещение на один такт от адреса перехода объясняется необходимостью записи этого адреса в регистр управления.

Введение регистра адреса перед МПЗУ хотя и задерживает выполнение микрокоманды на один такт, но позволяет организовать конвейер, т.е. сократить время выполнения операции. На практике МПЗУ выполняются большой разрядности: от нескольких десятков до сотен бит. Поэтому регистр адреса вводят редко. В качестве МПЗУ используют схемы с пережогом связей (К155РТ2, К566 РТХХ) и репрограммируемые схемы. Блок микропрограммного управления при использовании схем СИС и БИС аппаратно занимает значительный объем. Поэтому иногда, в специальных процессорах, его выполняют в виде одной БИС – управляющей памяти. Эти БИС, как правило, масочнопрограммируемые.. Аппаратные затраты сокращаются, но изменять микрокоманды пользователям в них невозможно.

Секционированные микропроцессоры. 11

Секционированные микропроцессоры (СМП) ориентированы на использование в специализированных вычислителях и контроллерах. Требуемая разрядность устройства получается за счет наращивания разрядности нескольких секций. Например, шестнадцатиразрядный вычислитель строится на четырех 4-х разрядных секциях. Наиболее замечательными сериями являются К588ВС1;2 К1804ВС1;2;3, К1800 ВС1.

К588ВС – 16 - разрядная секция, выполнена по КМОП технологии, ориентирована на применение в вычислителях с системой команд DEC. Она может использоваться как самостоятельная схема с микропрограммным управлением. Базовая технология КМОП позволяет использовать автономное питание. Схема не требует тактового генератора, в качестве тактового сигнала применяется 13-й разряд микрокоманды. Совместно с основной схемой разработаны дополнительные ИМС - регистры.

Поскольку схемы КМОП не могут работать в сложных условиях, разработали вычислительные ТТЛШ- секции серий К1802, К1804. Основное их назначение – бортовая аппаратура высокой производительности. Секции включают набор дополнительных схем. Серия К1804 получила большее распространение, в ее состав входит более 10 схем, но в них отсутствуют схемы ОЗУ и ПЗУ. Помимо серии 1802 и 1804 существуют сверхбыстродействующая серия К1800ВС1, выполненная по технологии ЭСЛ - схем. Кроме четырехразрядных секций и буферных регистров в ее состав включены небольшие схемы ОЗУ и ПЗУ. Структура секций во многом повторяет ОМП, но в них отсутствует адресный счетчик, регистр команд и регистр флагов, а дешифратор преобразует микрокоманду в унитарный код. Причина таких упрощений – большое выделение тепла элементами биполярных схем и, что бы кристалл не перегрелся , степень его интеграции делают небольшой.

Многокристальные микропроцессоры

Первые однокристальные микропроцессоры (микроконтроллеры) мало подходили для организации вычислительных процедур, а именно:

1) Разрядность адреса не высока, разрядность данных (8,16).

2) При необходимости разрядность данных можно было увеличить в 2-4 раза, но это приводило к большим временным затратам.

3) Сложные арифметические операции выполнялись программно, низкая производительность.

4) Неудобная система прерываний.

С развитием технологии производства интегральных схем эти недостатки в схемах микропроцессоров, разработанных для вычислительных систем, исключены полностью. Так, по своей структуре микропроцессор Pentium-4 во многом напоминает отечественную разработку «Эльбрус-3» с явно выраженной суперскалярной архитектурой. Первый шаг был сделан за счет введения адресного сумматора, позволяющего формировать адрес на ША гибким способом. Физический адрес формировался как сумма содержимого нескольких внутренних регистров процессора: индексного, адресного, смещения, сегментного и базового.

Сложные команды выполняются на специализированных операционных узлах. Первые опыты в этом направлении - применения арифметических микропроцессоров. Сопроцессор К1810ВМ87 заменяет основной процессор при выполнении команд деления , умножения, требующих большого времени. Локальная шина объединяет шина адреса и данных двух схем и общие сигналы управления. При получении кода длинной команды основной процессор блокируется, операция выполняется сопроцессором. Специализированные схемы, как правило, сочетали программную и аппаратную реализацию, что позволяло выполнять также операции за несколько тактов (5-6). Этот подход был оправдан, если в задачах постоянно встречались длинные операции. Увеличение интеграции позволило разместить на кристалле большее число элементов и интегрировать сопроцессор в основной кристалл, либо сделать кристалл сопроцессора рядом с основным кристаллом. Это направление привело также к введению буферной памяти команд и данных в структурах микропроцессора.

При передаче по ШД КОП и данных немало ситуаций, когда по шине ничего не передается, т.к. процессор выполняет текущую команду. Чтобы повысить производительность, предложено в «свободные окна» на ШД передавать коды следующих команд, расположенных по нарастанию адресов. Но для их хранения на кристалле нужна память, поэтому начали выполнять отдельный третий кристалл «кэш» память. Таким образом, микропроцессор стал состоять минимум из 3 частей. Такая конструкция размещается на посадочном месте в корпусе ИМС и коммутируется между собой локальной шиной в корпусе. Сегодня этот подход реализован на одном кристалле процессора, где дополнительно имеется буферная память данных с тем, чтобы снизить число обращений процессора во внешнюю память данных. Таким образом, введение буферной памяти команд и данных позволило заметно повысить производительность схемы. Команды загрузки выполняются традиционно, а чтение требуемых данных в процессе преобразования выполняется без обращения к шине данных. Использование буферной памяти приводит к тому, что программа располагается сегментами. Переход внутри сегментов не проводит к смене содержимого буферной памяти. Выход за пределы сегмента – перезапись нового сегмента в буферную память команд.

Разработаны схемы с коротким набором команд - RISC микропроцессор. В них введет конвейерный подход к преобразованию. Одновременно несколько команд выполняются в различных фазах. Самая первая команда заканчивается, последняя начинается. Команды разбиты на простые фрагменты.

Микропроцессоры с набором «длинных» команд – CISC-архитектура. Появились как альтернатива RISC-микропроцессорам с целью повышения производительности. Длинные команды в них выполнялись на специализированных арифметических устройствах, что позволяло упростить процедуру управления такой схемой и снизить частоту синхросигналов в микропроцессоре. Развитие архитектуры этих двух типов схем показало, что отдельно взятые ни RISC, ни CISC – процессоры не обладают заметным преимуществом при достижении высокой производительности. Только сочетание их качеств – конвейерной архитектуры и аппаратной реализации длинных команд позволяет заметно повысить производительность схем.

Вычислитель на ОМП 12

В качестве базовой схемы микропроцессора используем ОМП серии К1821 ВМ85 (Intel 8085)

Р ис.

20 .Пример схемы контроллера на ОМП.

ис.

20 .Пример схемы контроллера на ОМП.

А14 |

А15 |

|

0 |

0 |

ПЗУ |

0 |

1 |

Порт в/вывода |

1 |

0 |

ОЗУ |

1 |

1 |

ОЗУ |

С соответствующих выходов дешифратора согласно таблице подаем сигналы на входы разрешение выборки кристалла. Для ОЗУ необходима схема «И», объединяющая два выхода дешифратора. Управляющий сигнал чтение/запись формируется процессором, либо системным контроллером. Возможна ситуация, когда объем ОЗУ и ПЗУ превышает 64К. в этом случае рассматривается два адресных пространства: первое для ОЗУ и второе ПЗУ и порты ввода/вывода. Переключение адресных пространств – сигналами контроллера – фаза выборки, чтение/запись и т.д.

В реальных схемах число порто ввода/вывода может быть значительно, поэтому число областей в адресном пространстве может достигать 6-10. В этом случае используют двухступенчатую дешифрацию. Первая ступень - «грубый»дешифратор, у которого лишь один выход обращения к внешним устройствам. Второй дешифратор активизируется этим выходом и обеспечивает разделение внешних устройств и ПЗУ с помощью младших разрядов адреса.

Для ОМП с общей шиной необходимо сформировать адресные дешифраторы и адресные регистры на каждом функциональном блоке. Каждый блок имеет на входе адресный регистр с дешифрацией. Если адресное пространство его в регистр записывается – адрес и блок становится активными. Все остальные блоки не выбраны. Однокристальные микроЭВМ имеют в своем составе порты и некоторую память, поэтому структура контроллера отличается лишь блоком процессора. Способы подключения внешних устройств аналогичны. Контроллер на основе ОМП используют в промышленных системах управления, отображения информации ввода вывода. Их относительная черта – невысокая производительность, при несложных аппаратных затратах.

ПРОЦЕДУРА ВВОДА-ВЫВОДА 13

Работа любой ЭВМ складывается из процедур передачи информации между ее отдельными функциональными блоками. При этом передача информации между внутренними РОН называется пересылка, между процессором и памятью - чтение/запись, а между памятью и внешними устройствами- ввод/вывод информации. Наиболее длинными во времени процедурами считают операции ввода/вывода, поскольку внешние устройства в большинстве случаев имеют меньшее быстродействие, чем процессор или память. При разработке ЭВМ уделяют большое внимание возможным вариантам пересылки информации, рассматривая их с точки зрения снижения времени всей процедуры. Доступ к внешним устройствам, как правило, адресный, т. е. по структуре ввод/вывод не должен отличаться от чтения/записи. Но объем памяти значителен, значительна и шина адреса (минимум 16 разрядов). В тоже время число внешних устройств не может быть физически большим. В вычислителях системы DEC, I360 было принято ограничение на число внешних устройств - до 256. Это информационный объем байта, хотя реально число внешних устройств значительно меньше. Поэтому, сохраняя адресную выборку ВУ, ввод/вывод выполнялся с некоторым отличием от чтения/записи: Сигналы разрешения ввода/вывода формируются шинным контролером, в то время схемы ОЗУ и ПЗУ блокируется; Байт адреса выставляется на младших разрядах и дублировался на старших. Старший байт практически не используется Шина данных соединяет выход процессора и вход внешнего устройства (при выводе) и наоборот. Обмен информацией между внешними устройствами и памятью реализуется в одном из трех подходов: Программный режим. Процессор читает содержимое нужной ячейки памяти ОЗУ и выводит это содержимое из своего регистра во внешнее устройство. Не преобразуя информацию, процессор выступает лишь как временное хранилище (буферная память). Способ позволяет синхронизировать быстродействие внешнего устройства и памяти. Для выполнения процедуры требуется две команды. Адреса для внешних устройств байтовые. Способ возможен, если в наборе команд имеется команды ввода и вывода(IN ADR,.OUT ADR)Ввод/вывод с отображением в память. Наиболее универсальный способ, применяется, когда нет команд ввода/вывода. Последовательность выполнения та же самая: ОЗУCPU, CPUВУ. Отличие: процессор на внешнее устройство выставляет полный адрес, поэтому из адресного пространства исключаются адреса внешних устройств. Вывод с отображением используется часто, поскольку чтение/запись во многом похожи на ввод/вывод. Основной недостаток второго способа — занимается часть адресного пространства. Поэтому способ рекомендуется, если имеются свободные области в адресном пространстве.

Прямой доступ к памяти 14

Суть способа в том, что процессор как бы отключается от ШД и содержимое ОЗУ напрямую копируется во внешнее устройство. Главная цель применения ПДП — сократить время ввода/вывода с одновременным использованием процессора для выполнения следующей операции. Существует три способа обеспечения режима ПДП:

С блокировкой процессора.

С приходом запроса на ПДП, процессор отключается, его выходные шины адреса, данных и управления переводятся в третье состояние. Микрокоманды не расшифровываются устройством управления. Процессор не может выполнять операции, хотя тактовый сигнал и питание поступают. Чтобы перевести процессор в такой режим, требуется небольшое время. Для обеспечения управления (сигналы выборки, сопровождения, формирование сигналов адреса) необходимо новое устройство, называемое контролер ПДП. Контролер должен заменить процессор при формировании указанных сигналов. Обратный переход также требует некоторого времени. Способ характерен для несложных микропроцессоров, имеющих один или несколько регистров команд и не имеющих внутренней буферной памяти (кэш) данных.

С квантованием цикла.

В каждом цикле обращения к памяти (ОЗУ, ПЗУ) процессор должен успеть выполнить это обращение за время половины длительности цикла обмена с памятью. Во второй половине цикла процессор отключает свои выходы, позволяя контролеру ПДП выставить свой адрес на шину. За второй интервал выполняется процедура ввода/вывода. Такое условие требует быстродействующей памяти, следовательно, смены элементной базы (переход к ЭСЛ-схемам). Последнее затрудняет использование такого подхода, поэтому он практически не применяется.

С отъемом цикла.

При работе процессора, имеющего внутреннюю буферную память команд и данных, реализуется ПДП с отъемом цикла. Процессор начинает команду с выборки — обращение к ПЗУ, далее ОЗУ или ввод/вывод. Особенность третьего способа в том, что вместо положенного обращения процессора в память (стандартный цикл) выполняется процедура ввода/вывода режима ПДП. При этом процессор выполняет текущую команду, поскольку в его буфере команд стоит очередь следующих друг за другом операций. Выходные разряды процессора переводятся в третье состояние и не оказывают влияния на состояние шин адреса и данных. Главное отличие от первого способа — процессор выполняет текущую, следующую команды не останавливаясь. Поскольку процессор не занимает шины в этом режиме, процедура ввода/вывода выполняется как бы одновременно с основной операцией.

В любом режиме ПДП необходим контроллер специализированная схема, работающая синхронно с процессором. Контролеры входят в микропроцессорные комплекты соответствующих серий. Основу их составляют счетчики адреса с произвольной загрузкой и небольшая схема управления

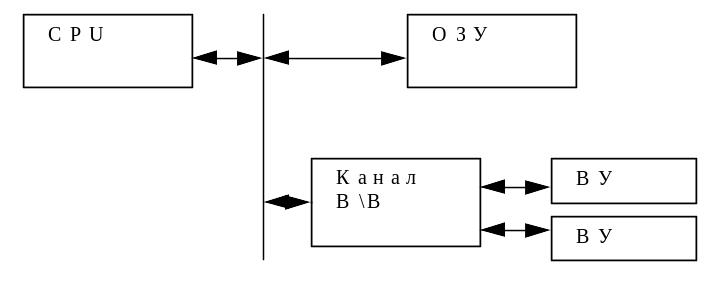

Каналы ввода-вывода 15

Для обмена

информацией между процессором, ОЗУ и

внешними устройствами существует

буферный блок — каналы ввода/вывода.

Канал — это интегрированное понятие,

объединяющее как аппаратные, так и

программные средства вычислителя для

подключения периферии. Число внешних

устройств может быть значительным,

поэтому для удобства работы с большим

числом внешних устройств, применяют

специальное оборудование — каналы

ввода/вывода. Структурно каналы включаются

между шиной процессора и внешними

устройствами

Для обмена

информацией между процессором, ОЗУ и

внешними устройствами существует

буферный блок — каналы ввода/вывода.

Канал — это интегрированное понятие,

объединяющее как аппаратные, так и

программные средства вычислителя для

подключения периферии. Число внешних

устройств может быть значительным,

поэтому для удобства работы с большим

числом внешних устройств, применяют

специальное оборудование — каналы

ввода/вывода. Структурно каналы включаются

между шиной процессора и внешними

устройствами

. Функционально канал — это промежуточный буферный блок, предназначенный для согласования во времени работы быстрого процессора и разнотипных внешних устройств. Основу канала составляют устройства управления и буферная память, накапливающая данные для ввода или вывода из процессора. Любая процедура ввода/вывода переносит данные из ОЗУ в буферную память канала в режиме ПДП или программно, т.е. процессор не видит внешнего устройства. Процессор работает с каналом, произвольное ВУ также не имеет прямого доступа к ОЗУ или процессору. Внешнее устройство переносит информацию в канал. Каналы конструктивно и функционально были развиты в машинах ЕС ЭВМ. Там использовались каналы двух типов: селекторные и мультиплексные. Первые обеспечивали связь процессора с одним быстрым ВУ, т.е. селекторный канал имел буферную память маятникового типа (память делится пополам, в одну часть запись из другой части чтение, если память переполнена, составляющие меняются местами). Это позволяет «одновременно» читать/записывать память.

Селекторные каналы объединялись в группы, что позволяло подключать несколько внешних устройств к процессору, но в любой момент работало только одно ВУ. Мультиплексные каналы рассчитаны на работу с медленными ВУ (печать, клавиатура, НМЛ). Мультиплексный канал работает в байт-последовательном режиме с несколькими внешними устройствами «одновременно». Фактически канал опрашивает последовательно каждое внешнее устройство, пересылает байт и обращается к следующему.

Буферная

память таких каналов разделена на

подканалы. Каждый подканал работает с

одним ВУ. В конечном счете, буферная

память заполняется информацией с

нескольких ВУ и процессор быстро

прочитает данные. Управляющие сигналы

формируются на основании командного

слова канала — процессор пересылает

команду в канал, она расшифровывается

и внешнее устройство получает управляющий

не от процессора, а от устройства

управления каналом. Кроме командного

слова процессор посылает в канал адресное

слово — начальный или конечный адрес

источника информации. Слова данных

также иногда выделяют при обмене

информации. Многие внешние устройства

имеют собственную буферную память,

поэтому необходимости в самостоятельном

канале у них нет. Функции канала, его

принципы организации уже внесены в

структуру внешнего устройства. Отсюда

необходимость в использовании каналов

как самостоятельных функциональных

узлов возникает в тех случаях, когда

очень быстрый процессор обменивается

с довольно медленными внешними

устройствами, число которых значительно.

Буферная

память таких каналов разделена на

подканалы. Каждый подканал работает с

одним ВУ. В конечном счете, буферная

память заполняется информацией с

нескольких ВУ и процессор быстро

прочитает данные. Управляющие сигналы

формируются на основании командного

слова канала — процессор пересылает

команду в канал, она расшифровывается

и внешнее устройство получает управляющий

не от процессора, а от устройства

управления каналом. Кроме командного

слова процессор посылает в канал адресное

слово — начальный или конечный адрес

источника информации. Слова данных

также иногда выделяют при обмене

информации. Многие внешние устройства

имеют собственную буферную память,

поэтому необходимости в самостоятельном

канале у них нет. Функции канала, его

принципы организации уже внесены в

структуру внешнего устройства. Отсюда

необходимость в использовании каналов

как самостоятельных функциональных

узлов возникает в тех случаях, когда

очень быстрый процессор обменивается

с довольно медленными внешними

устройствами, число которых значительно.