- •1.Задачи развития и совершенствования средств связи. Современное состояние и перспективы в области телекоммуникаций.

- •3. Строение уха, слуховое восприятие, формирование звуков речи и их свойства

- •4. Электроакустические преобразователи (телефон, микрофон), их основные технические параметры.

- •5. Телефонные аппараты (принципиальные противоместные схемы). Параметры номеронабирателя.

- •6. Обобщенная схема атс, порядок установления соединений

- •7. Сигналы управления и взаимодействия (сув) в атс. Виды и назначение сигналов.

- •9. Обобщенная структурная схема цифровой атс. Преобразование аналогового сигнала в цифровую форму

- •10. Многоканальные разговорные икм - тракты с временным разделением каналов (врк).

- •11. Принципы построения основных функциональных узлов цифровых атс. Линейный блок, синхронная и асинхронная схемы передачи-приема

- •4.4 Линейный комплект

- •12. Принципы построения основных функциональных узлов цифровых атс Коммутационное поле пространственной и временной коммутации, многочастотные приемники и передатчики

- •4.5 Коммутационное поле

- •4.6 Цифровые многочастотные передатчики

- •13. Сигнализация по 2-х проводным аналоговым абонентским линиям, по цифровым линиям (е-dss1). Сигнализация по интерфейсу v5.

- •14. Межстанционная линейная и регистровая сигнализация. Сценарии протоколов сигнализации на языке msc.

- •15. Сеть общеканальной сигнализации окс- 7. Принципы построения, режимы.

- •16. Уровни и подсистемы окс-7.

- •17. Подсистема передачи сообщений (мтр) окс-7.

- •18. Подсистема пользователя сети окс-7 с интеграцией служб (isup). Сообщения при установлении соединения. Сценарий процесса установления соединения.

- •19. Идеология и архитектура Softswitch. Эталонная модель.

- •20. Функциональные объекты в архитектуре Softswitch.

- •21. Примеры реализации Softswitch в архитектуре сетей следующего поколения.

- •22. Архитектура и интерфейсы gsm (мобильная станция, подсистема базовых станций, центр коммутации,, домашний и визитный регистры).

- •23. Архитектура и интерфейсы сети gsm(регистры защиты и аутентификации, оборудование эксплуатации и технического обслуживания)

- •28. Gsm. Обновление местоположения. Аутентификация и защита Обновление местоположения

- •Хэндовер

- •31. Многостанционный доступ с кодовым разделением (cdma). Функции Уолша. Многостанционный доступ с кодовым разделением

- •36. Сети на основе cdma. Мягкая передача вызова.

- •37. Сети на основе cdma. Параметры хэндовера.

- •1) Таймер снижения уровня t_tdrop

- •2) Порог обнаружения пилот-сигнала t_add

- •3) Порог сравнение t_comp

- •4) Порог снижения пилот-сигнала t_drop

- •5) Значение таймера снижения уровня t_tdrop

- •38. Сети на основе cdma. Процедура совмещённого мягкого хэндовера.

12. Принципы построения основных функциональных узлов цифровых атс Коммутационное поле пространственной и временной коммутации, многочастотные приемники и передатчики

Рисунок 3.6.1 – Структурная схема цифровой АТС

АТСЭ состоит из отдельных модулей, представляющих собой функционально-конструктивные единицы.

В состав АТСЭ входят:

модули абонентских линий (МАЛ);

модули цифровой коммутации (МЦК);

модули соединительных линий (МСЛ);

другое дополнительное оборудование.

Управляющее устройство (УУ)

Цифровые многочастотные передатчики (ПРДЧ) и приемники (ПРМЧ)

По шине данных и управления (ШДУ) УУ задает команды и контролирует изменение состояния комплектов.

4.5 Коммутационное поле

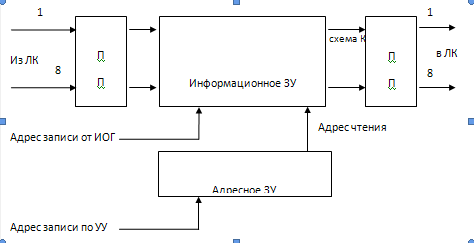

Коммутационное поле (КП) предназначено для коммутации любого канала входящего тракта с любым каналом исходящего тракта. Структурная схема КП приведена на рисунке 4.5.1, она содержит: последовательно-параллельные преобразователи (ППП) на входе и параллельно-последовательные — на выходе, информационное запоминающее устройство (ИЗУ) и адресное ЗУ (АЗУ). В ИЗУ хранится разговорная информация, а в АЗУ — информация об установленных соединениях.

Р исунок

4.5.1 - Функциональная схема КП

исунок

4.5.1 - Функциональная схема КП

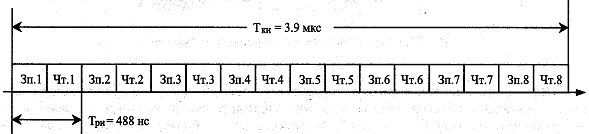

За время одного канального интервала (Тки=3.9 мке) последовательно во времени производится запись и чтение байта информации для всех одноименных каналов всех трактов. За время одного разрядного интервала Три= 488нс происходит запись по адресу.

Я чейки

чейки

Рисунок 4.5.3 - Диаграмма работы ИЗУ

Один из путей построения КП большой емкости — увеличение числа операций записи в чтения за один Тки, что приводит к уменьшению времени на эти операции. Ограниченное быстродействие ЗУ налагает ограничения на максимальную емкость КП, которая обычно не превышает емкость 16x16 трактов. Поэтому идут другим путем.

4.6 Цифровые многочастотные передатчики

С труктурная

схема цифрового передатчика изображена

на рисунке 4.6.1. Она содержит; n-разрядный

счетчик Сч, полупостоянное запоминающее

устройство ППЗУ, параллельно-поcледовательный

преобразователь ППП. На вход счетчика

от ОИГ поступают импульсы частотой 8

кГц (каждые 125 мкс). Код на выходе Сч

определяет номер ячейки, с которой

считывается очередное значение цифрового

синусоидального сигнала. Разрядность

Сч определяется номиналом генерируемой

частоты. На вход КП значения отсчетов

частоты поступают после ППП в

последовательном виде.

труктурная

схема цифрового передатчика изображена

на рисунке 4.6.1. Она содержит; n-разрядный

счетчик Сч, полупостоянное запоминающее

устройство ППЗУ, параллельно-поcледовательный

преобразователь ППП. На вход счетчика

от ОИГ поступают импульсы частотой 8

кГц (каждые 125 мкс). Код на выходе Сч

определяет номер ячейки, с которой

считывается очередное значение цифрового

синусоидального сигнала. Разрядность

Сч определяется номиналом генерируемой

частоты. На вход КП значения отсчетов

частоты поступают после ППП в

последовательном виде.

Рисунок 4.6.1 - Структурная схема цифрового передатчика.

Для определения минимального значения разрядности Сч следует сократить дробь 8000/f, где f — номинал требуемой частоты. Тогда числитель выражает разрядность n, а знаменатель — число периодов требуемой частоты Т. Мгновенные значения сигналов определяются по формуле

u = Um sin 27πfkt, k=l,2,…n,

где Um — требуемая амплитуда сигнала, f — номинал требуемой частоты, t=125 мкс. Значение Um обычно задается уровнем сигнала Ао в точке с 0-м относительным уровнем, поэтому сначала из уравнения

Ао = 20 lg U/Uo

при

известных значениях Uo=0.775

В и Ао находится действующее значение

U,

а затем — амплитуда

![]() .

.

Шаг квантования Q изменяется при переходе от сегмента к сегменту и в зависимости от номера сегмента r определяется выражением

Q = q, при r=0

2r-1>q, при r=1,..7

где q = Uorp / 2 11 , Uoгp=2.5 В — порог ограничения кодера.

В случае многочастотного передатчика оговариваются параметры (амплитуда и частота) каждого сигнала. Процедура проектирования цифрового многочастотного передатчика следующая.1. Пользуясь значениями частот f1, находят наименьший общий период (минимальную разрядность счетчика — n).2. Пользуясь значениями заданных уровней каждой частоты, находят амплитуды каждого из сигналов Ui.3. Используя формулуU=U1, sin 2πf1, kt + U2 sin 2πf2 kt + ..., k=l,2,...n,находят мгновенные значения сигналов, а из таблицы — значения кодов.4. Записывают найденные значения кодов в соответствующие ячейки ППЗУ.

4.7 Цифровые многочастотные приемники

Структурная схема цифрового приемника изображена на Рисунок 4.7.1. Она содержит: n-разрядный счетчик Сч, оперативное запоминающее устройство ОЗУ, параллельно-последовательный преобразователь ППП, микропроцессор Мпр. На вход счетчика от ОИГ на счетный вход С поступают импульсы с частотой следования каналов 8 кГц. Код на выходе Сч соответствует номеру канала и определяет номер ячейки, в которую записывается очередное значение цифрового значения синусоидального сигнала, поступающего из КП через ППП. Разрядность Сч определяется числом каналов в ИКМ-тракте.

Алгоритм декодирования одной частоты состоит в подсчете экстремумов и проверке периодичности их появления.

Известен один из алгоритмов декодирования 2-частотных сигналов, состоящий в подсчете на определенном периоде числа глобальных и локальных экстремумов, количественное сочетание которых и определяет номиналы поступивших частот.

Р исунок

4.7.1 - Структурная схема цифрового

приемника частоты.

исунок

4.7.1 - Структурная схема цифрового

приемника частоты.

Общий алгоритм декодирования многочастотного сигнала F=f1+f2+…fn

состоит в определении номинала одной из частот fi путем обнаружения и подсчета периодически повторяющихся экстремумов. Затем из суммарного сигнала F вычитаются (суммируются с противоположным знаком) значения обнаруженной частоты fi и далее эта же процедура повторяется для нового значения суммарного сигнала (F – fi).