- •1. Введение

- •2. Дискретизация аналоговых сигналов

- •2.1 Квантование по уровню

- •2.2 Квантование по времени

- •2.3 Квантование по уровню и по времени

- •2.3.1 Расчет погрешности ацп

- •2.3.2 Выбор величины шага квантования по времени

- •3. Применение алгебры логики (булевой алгебры) при анализе и синтезе цифровых электронных устройств

- •3.1 Определение и способы задания переключательных функций

- •3.4 Базисные логические функции

- •3.5 Принцип двойственности булевой алгебры

- •3.8 Совершенная дизъюнктивная нормальная форма (сднф) записи булевых выражений

- •3.9 Дизъюнктивная нормальная форма (днф)

- •3.10 Совершенная конъюнктивная нормальная форма (скнф) записи булевых выражений

- •3.11 Конъюнктивная нормальная форма (кнф)

- •3.12 Минимизация логических функций

- •3.12.1 Алгебраический способ минимизации пф

- •3.12.2 Минимизация пф с использованием диаграмм Вейча (карт Карно)

- •3.12.2.1 Минимизация пф с помощью диаграмм Вейча

- •3.12.2.1.1 Общие правила минимизации

- •3.12.2.1.2 Примеры минимизации пф с помощью диаграмм Вейча

- •3.12.2.2 Минимизация пф с помощью карт Карно

- •4. Логические элементы

- •4.1 Инвертор (логический элемент не)

- •4.2 Конъюнктор (логический элемент и)

- •4.3 Дизъюнктор (логический элемент или)

- •4.4 Повторитель

- •4.7 Исключающее или

- •4.8 Сложение по модулю два (нечетность)

- •4.9 Сложение по модулю два с отрицанием (четность)

- •4.10 Эквивалентность

- •4.11 Неэквивалентность

- •4.13 Запрет

- •4.14 Логические элементы с открытым коллектором

- •4.15 Логические элементы с третьим состоянием

- •5. Реализация логических функций в разных базисах

- •5.1 Базисные наборы лэ и их взаимосвязь

- •5.2 Реализация логических функций в различных базисах

- •5.2.1 Реализация элемента “Равнозначность” (исключающее или - не)

- •5.2.2 Реализация элемента “Неравнозначность” (исключающее или, сумма по модулю два)

- •5.2.3 Реализация элемента “Запрет”

- •5.2.4 Реализация многобуквенных логических функций на элементах с небольшим количеством входов

- •6. Параметры и характеристики цифровых интегральных микросхем (имс)

- •6.1 Коэффициент объединения по входу (Коб)

- •6.2 Коэффициент разветвления по выходу (Краз)

- •6.3 Статические характеристики

- •6.4 Помехоустойчивость

- •6.5 Динамические характеристики и параметры

- •6.6 Вид реализуемой логической функции

- •6.7 Потребляемые токи и мощность

- •6.8 Входные и выходные токи, напряжения

- •6.9 Пороговые напряжения

- •6.10 Допустимые значения основных параметров

- •7. Базовые логические элементы

- •7.1 Базовый ттл (ттлш) - элемент и-не

- •7.2 Базовый эсл - элемент или/или-не

- •7.3 Базовый кмоп-элемент или-не

- •8. Генераторы тактовых импульсов (гти) на логических элементах

- •8.1 Гти на двух инверторах

- •8.2 Гти на 3-х инверторах.

- •9. Функциональные устройства компьютерной (цифровой) электроники

- •9.1 Комбинационные цифровые устройства (кцу)

- •9.1.1 Анализ и синтез кцу

- •9.1.1.1 Анализ кцу

- •9.1.1.2 Синтез кцу

- •9.1.2 Типовые кцу

- •9.1.2.1 Шифраторы и дешифраторы

- •9.1.2.1.1 Шифраторы двоичного кода

- •9.1.2.1.2 Шифраторы двоично-десятичного кода

- •9.1.2.1.3 Дешифраторы двоичного кода

- •9.1.2.1.4 Дешифратор bcd-кода в семисегментный код

- •9.1.2.1.4.1 Семисегментные индикаторы на светодиодах

- •9.1.2.2 Мультиплексоры и демультиплексоры

- •9.1.2.2.1 Мультиплексоры

- •9.1.2.2.2 Демультиплексоры

- •9.1.2.2.3 Мультиплексоры–селекторы (мультиплексоры-демультиплексоры)

- •9.1.2.3 Сумматоры и полусумматоры

- •9.1.2.4 Устройства контроля четности (укч)

- •9.1.2.5 Цифровые компараторы

- •9.1.3 Использование для проектирования кцу мультиплексоров, дешифраторов и постоянных запоминающих устройств

- •9.1.3.1 Построение кцу на мультиплексорах

- •9.1.3.2 Построение кцу на дешифраторах

- •9.1.3.3 Построение кцу на постоянном запоминающем устройстве (пзу)

- •9.2 Последовательностные цифровые устройства

- •9.2.1 Триггеры

- •9.2.1.1 Триггеры на логических элементах

- •9.2.1.1.1 Rs - триггеры

- •9.2.1.1.1.1 Асинхронные rs - триггеры

- •9.2.1.1.1.2 Синхронные rs - триггеры

- •9.2.1.1.2 Т-триггеры (триггеры со счетным входом)

- •9.2.1.1.3 D-триггеры (триггеры задержки)

- •9.2.1.1.4 Jk-триггеры

- •9.2.1.2 Триггеры в интегральном исполнении

- •9.2.2 Регистры

- •9.2.2.1 Параллельные регистры

- •9.2.2.2 Последовательные (сдвигающие) регистры

- •9.2.2.3 Регистры сдвига

- •9.2.2.4 Последовательно-параллельные и параллельно-последовательные регистры

- •9.2.2.5 Регистры в интегральном исполнении

- •9.2.3.1 Асинхронный суммирующий двоичный счетчик с последовательным переносом

- •9.2.3.2 Асинхронный вычитающий двоичный счетчик с последовательным переносом

- •9.2.3.3 Асинхронные реверсивные двоичные счетчики с последовательным переносом

- •9.2.3.4 Синхронный счетчик со сквозным переносом

- •9.2.3.5 Десятичные счетчики

- •9.2.3.6 Счетчики в интегральном исполнении

- •9.2.4 Делители частоты

- •9.2.5 Распределители

- •10. Связь мп-ра и омэвм с аналоговым объектом управления и с пк

- •10.1 Структура типичной локальной микропроцессорной системы управления (лмпсу)

- •10.1.1 Назначение и схемная реализация отдельных узлов лмпсу

- •10.1.1.1 Аналоговый мультиплексор (ампс)

- •10.1.1.2 Устройство выборки-хранения (увх)

- •10.1.1.3 Аналого-цифровой преобразователь (ацп)

- •10.1.1.4 Ведомая однокристальная микроЭвм (омэвм)

- •10.1.1.5 Шинный формирователь (шф)

- •10.1.1.6 Регистры (Рг1...Рг3)

- •10.1.1.7 Схемы согласования уровней (ссу1...Ссу3)

- •10.1.1.8 Цифро-аналоговые преобразователи (цап1...Цап3)

- •10.2 Применение ацп и увх при вводе аналоговой информации в мпс

- •10.2.1 Расчет ацп

- •10.2.2.1 Описание микросхемы к1113 пв1

- •10.2.2.2 Расчет микросхемы к1113 пв1

- •10.2.2.3 Ввод данных от ацп в мпс через ппи в режиме 0

- •10.2.3 Устройство выборки и хранения (увх)

- •10.2.3.1 Обоснование применения увх

- •10.2.3.2 Принцип действия, схема и основные параметры увх

- •10.2.3.3 Функциональные возможности и схема включения микросхемы увх к1100ск2 (кр1100ск2)

- •10.2.4.1 Описание микросхемы max154. Временные диаграммы и режимы работы

- •10.2.4.2 Расчет ацп max154

- •10.3 Применение цап при выводе цифровой информации из мпс

- •10.3.1 Расчет цап на матрице r-2r c суммированием токов

- •10.3.2.1 Описание микросхемы к572 па1

- •10.3.2.2 Расчет цап к572 па1

- •10.3.3.1 Описание микросхемы max506

- •10.3.3.2 Расчет цап max506

- •10.4 Особенности аппаратной и программной реализации модуля ацп-цап мпс

- •10.4.1 Аппаратный уровень:

- •10.4.2 Программный уровень:

- •10.5 Обмен между мп-м (омэвм) и пк по последовательному каналу связи с помощью интерфейса rs-232с

- •10.5.1 Устройство асинхронное программируемое приёмопередающее (уапп)

- •10.5.2 Устройство преобразования уровней (упу)

- •10.5.3 Разъём rs-232с

- •10.5.4 Буферный регистр адреса rs-232c

- •10.5.5 Шинный формирователь

- •10.6 Выбор и расчет датчиков, нормирующих преобразователей и фильтров нижних частот (фнч)

- •10.6.1 Выбор и расчет датчиков и нормирующих преобразователей

- •10.6.1.1 Выбор датчиков

- •10.6.1.2 Выбор нормирующих преобразователей

- •10.6.2 Выбор фнч

- •10.6.3 Расчет фнч

- •10.7 Разработка схемы алгоритма и управляющей программы

9.2.3.6 Счетчики в интегральном исполнении

В различных сериях интегральных микросхем широко представлены счетчики [3, 4]. В качестве примера рассмотрим ИМС К555ИЕ7, которая представляет собой двоичный 4-х разрядный реверсивный счетчик (рисунок 9.61).

Рисунок 9.61

Микросхема содержит два входа для счетных импульсов. Если счетчик работает как суммирующий, то счетные импульсы подаются на вход С+, а если как вычитающий – то на С-, причем на неиспользуемом счетном входе должно быть напряжение высокого уровня. В качестве очередного счетного импульса на одном из входов С+ или С- воспринимается срез нулевого импульса (перепад из 0 в 1).

Счетчик содержит асинхронный вход установки в нуль R и входы параллельной записи исходной кодовой комбинации D1...D4. Эта запись производится при наличии нулевых сигналов на входах R и V (загрузка).

На выходе >15 формируется сигнал переноса при суммировании входных импульсов, когда их число превышает 15, а на выводе <0 - сигнал заема при вычитании, когда очередной импульс на вход С - поступает при нулевом состоянии счетчика. Эти сигналы представляют перепад из 0 в 1 и являются ответными на срез (перепад из 0 в 1) нулевых входных счетных импульсов.

Путем последовательного соединения четырехразрядных счетчиков К555ИЕ7 можно построить двоичные реверсивные счетчики с большим числом разрядов.

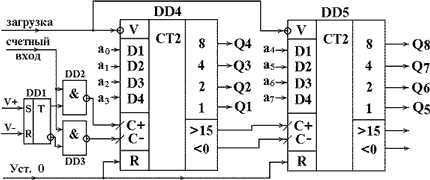

На рисунке 9.62 показан пример построения 8-разрядного реверсивного счетчика на двух 4-разрядных типа К555ИЕ7.

Рисунок 9.62

Счетчик содержит один счетный вход и два сигнала управления V+ и V-, определяющие, в каком режиме предполагается использовать схему - в режиме суммирования (V+=1, V- =0) или вычитания (V+=0, V- =1). Для управления микросхемой К555ИЕ7, содержащей два счетных входа С+ и С-, в устройство включены асинхронный RS-триггер (DD1) и два конъюнктора (DD2, DD3).

При подаче единичного сигнала на вход V+ (при V- =0) RS-триггер устанавливается в 1 и счетные импульсы через DD2 поступают на вход С+ микросхемы СТ2 (DD4). При поступлении единичного сигнала на вход V- (при V+=0) RS-триггер сбрасывается в нуль и счетные импульсы через DD3 подаются на вход С - микросхемы СТ2(DD4). Когда рассматриваемая схема производит суммирование входных импульсов, то сигнал переноса (перепад из 0 в 1) появляется на выходе >15 второй микросхемы СТ2(DD5) при поступлении на вход 256-го импульса (при условии, что счет начинался с нулевого значения). Сигнал заема на выходе <0 второй схемы СТ2(DD5) (перепад из 0 в 1) появляется при поступлении на счетный вход 256-го вычитающего импульса (при условии, что вычитание начиналось с единичных значений во всех разрядах). При этом происходит вычитание из нуля единицы, и все триггеры счетчика вновь устанавливаются в единицу.

9.2.4 Делители частоты

В делителях частоты входная периодическая последовательность импульсов делится на заданное число.

В качестве делителя частоты можно использовать счетчик, коэффициент пересчета которого Ксч определяет число, на которое делится частота входных счетных импульсов. Особенность делителя состоит в том, что он имеет один выход.

Коэффициент деления Кдел=Ксч может иметь постоянное или изменяемое (переменное) значение.

Делители с переменным коэффициентом деления (ДПКД) могут быть построены по различным схемотехническим вариантам. Например, с предустановкой исходного состояния, от которого ведется счет, до переполнения счетчика, либо с установкой заданного промежуточного значения, до которого, начиная с нулевого, ведется счет входных импульсов, а затем результат сбрасывается и начинается новый счетный цикл. Примеры счетчиков работающих по описанным правилам рассмотрены в [3, 4].

Пример ДПКД, построенного по первому варианту (с предустановкой исходного состояния) приведены на рисунке 9.63.

Рисунок 9.63

Делитель выполнен на основе микросхемы четырехразрядного двоично/десятичного реверсивного счетчика К561ИЕ14. На входы предустановки D1...D4 подается код, соответствующий числу “лишних” состояний (24 - Кдел). Выход сигнала переноса Р соединяют через инвертор DD1 с управляющим входом V (загрузка). Сигналом 1 на этом входе число с входов D1...D4 записывается в триггеры счетчика. На входы +/- и 2/10 подаются единичные сигналы, настраивающие ИМС на работу в режиме суммирующего двоичного счетчика. Чтобы разрешить счет вход Po соединяют с землей (нулевым потенциалом). Под воздействием входных импульсов на входе С счетчик-делитель последовательно проходит состояния от исходного, предварительно установленного по входам D1...D4, до конечного, когда он заполняется единицами во всех четырех разрядах. Следующим импульсом после этого схема сбрасывается в нуль и формируется сигнал переноса на выходе Р. Этим сигналом разрешается запись в счетчик исходного кода и цикл вновь повторяется. С выхода схемы снимается последовательность импульсов с частотой

fвых = fвх / Кдел.(9.22)

Для рассматриваемого устройства Кдел принимает значения от 1 до 16.

На рисунке 9.64 приведен пример делителя, построенного по второму варианту.

Рисунок 9.64

Основу ДПКД составляет двоичный счетчик (DD2), который начинает счет с нулевого значения и продолжает работу до установленного промежуточного состояния, равного требуемому коэффициенту деления Кдел. После этого счетчик вновь сбрасывается нуль и начинается новый цикл счета. Для определения момента достижения равенства кодов, определяющих промежуточное состояние счетчика и значение Кдел, в схеме использован цифровой компаратор (DD1). В момент равенства кодов А=В на выходе компаратора появляется логическая единица, сбрасывающая счетчик в исходное нулевое состояние. Дополнительный триггер (DD3) необходим для исключения возможности сбоя при установке нулевого состояния СТ2 из-за разброса временных параметров триггеров счетчика. Сигналом с выхода компаратора FА=В триггер устанавливается в 1 и поддерживает на входе R счетчика единичный сигнал на время, достаточное для сброса всех разрядов DD2. Следующим входным импульсом триггер сбрасывается в нулевое состояние. Если разброс временных параметров триггеров счетчика невелик, то DD3 можно исключить.

Делитель с постоянным коэффициентом деления можно построить проще. Для этого компаратор заменяют конъюнктором, на входы которого подают выходные сигналы с тех разрядов счетчика, которые в кодовой комбинации, соответствующей Кдел, имеют высокий уровень. Пример делителя с Кдел = 9 показан на рисунке 9.65.

Рисунок 9.65