- •1. Введение

- •2. Дискретизация аналоговых сигналов

- •2.1 Квантование по уровню

- •2.2 Квантование по времени

- •2.3 Квантование по уровню и по времени

- •2.3.1 Расчет погрешности ацп

- •2.3.2 Выбор величины шага квантования по времени

- •3. Применение алгебры логики (булевой алгебры) при анализе и синтезе цифровых электронных устройств

- •3.1 Определение и способы задания переключательных функций

- •3.4 Базисные логические функции

- •3.5 Принцип двойственности булевой алгебры

- •3.8 Совершенная дизъюнктивная нормальная форма (сднф) записи булевых выражений

- •3.9 Дизъюнктивная нормальная форма (днф)

- •3.10 Совершенная конъюнктивная нормальная форма (скнф) записи булевых выражений

- •3.11 Конъюнктивная нормальная форма (кнф)

- •3.12 Минимизация логических функций

- •3.12.1 Алгебраический способ минимизации пф

- •3.12.2 Минимизация пф с использованием диаграмм Вейча (карт Карно)

- •3.12.2.1 Минимизация пф с помощью диаграмм Вейча

- •3.12.2.1.1 Общие правила минимизации

- •3.12.2.1.2 Примеры минимизации пф с помощью диаграмм Вейча

- •3.12.2.2 Минимизация пф с помощью карт Карно

- •4. Логические элементы

- •4.1 Инвертор (логический элемент не)

- •4.2 Конъюнктор (логический элемент и)

- •4.3 Дизъюнктор (логический элемент или)

- •4.4 Повторитель

- •4.7 Исключающее или

- •4.8 Сложение по модулю два (нечетность)

- •4.9 Сложение по модулю два с отрицанием (четность)

- •4.10 Эквивалентность

- •4.11 Неэквивалентность

- •4.13 Запрет

- •4.14 Логические элементы с открытым коллектором

- •4.15 Логические элементы с третьим состоянием

- •5. Реализация логических функций в разных базисах

- •5.1 Базисные наборы лэ и их взаимосвязь

- •5.2 Реализация логических функций в различных базисах

- •5.2.1 Реализация элемента “Равнозначность” (исключающее или - не)

- •5.2.2 Реализация элемента “Неравнозначность” (исключающее или, сумма по модулю два)

- •5.2.3 Реализация элемента “Запрет”

- •5.2.4 Реализация многобуквенных логических функций на элементах с небольшим количеством входов

- •6. Параметры и характеристики цифровых интегральных микросхем (имс)

- •6.1 Коэффициент объединения по входу (Коб)

- •6.2 Коэффициент разветвления по выходу (Краз)

- •6.3 Статические характеристики

- •6.4 Помехоустойчивость

- •6.5 Динамические характеристики и параметры

- •6.6 Вид реализуемой логической функции

- •6.7 Потребляемые токи и мощность

- •6.8 Входные и выходные токи, напряжения

- •6.9 Пороговые напряжения

- •6.10 Допустимые значения основных параметров

- •7. Базовые логические элементы

- •7.1 Базовый ттл (ттлш) - элемент и-не

- •7.2 Базовый эсл - элемент или/или-не

- •7.3 Базовый кмоп-элемент или-не

- •8. Генераторы тактовых импульсов (гти) на логических элементах

- •8.1 Гти на двух инверторах

- •8.2 Гти на 3-х инверторах.

- •9. Функциональные устройства компьютерной (цифровой) электроники

- •9.1 Комбинационные цифровые устройства (кцу)

- •9.1.1 Анализ и синтез кцу

- •9.1.1.1 Анализ кцу

- •9.1.1.2 Синтез кцу

- •9.1.2 Типовые кцу

- •9.1.2.1 Шифраторы и дешифраторы

- •9.1.2.1.1 Шифраторы двоичного кода

- •9.1.2.1.2 Шифраторы двоично-десятичного кода

- •9.1.2.1.3 Дешифраторы двоичного кода

- •9.1.2.1.4 Дешифратор bcd-кода в семисегментный код

- •9.1.2.1.4.1 Семисегментные индикаторы на светодиодах

- •9.1.2.2 Мультиплексоры и демультиплексоры

- •9.1.2.2.1 Мультиплексоры

- •9.1.2.2.2 Демультиплексоры

- •9.1.2.2.3 Мультиплексоры–селекторы (мультиплексоры-демультиплексоры)

- •9.1.2.3 Сумматоры и полусумматоры

- •9.1.2.4 Устройства контроля четности (укч)

- •9.1.2.5 Цифровые компараторы

- •9.1.3 Использование для проектирования кцу мультиплексоров, дешифраторов и постоянных запоминающих устройств

- •9.1.3.1 Построение кцу на мультиплексорах

- •9.1.3.2 Построение кцу на дешифраторах

- •9.1.3.3 Построение кцу на постоянном запоминающем устройстве (пзу)

- •9.2 Последовательностные цифровые устройства

- •9.2.1 Триггеры

- •9.2.1.1 Триггеры на логических элементах

- •9.2.1.1.1 Rs - триггеры

- •9.2.1.1.1.1 Асинхронные rs - триггеры

- •9.2.1.1.1.2 Синхронные rs - триггеры

- •9.2.1.1.2 Т-триггеры (триггеры со счетным входом)

- •9.2.1.1.3 D-триггеры (триггеры задержки)

- •9.2.1.1.4 Jk-триггеры

- •9.2.1.2 Триггеры в интегральном исполнении

- •9.2.2 Регистры

- •9.2.2.1 Параллельные регистры

- •9.2.2.2 Последовательные (сдвигающие) регистры

- •9.2.2.3 Регистры сдвига

- •9.2.2.4 Последовательно-параллельные и параллельно-последовательные регистры

- •9.2.2.5 Регистры в интегральном исполнении

- •9.2.3.1 Асинхронный суммирующий двоичный счетчик с последовательным переносом

- •9.2.3.2 Асинхронный вычитающий двоичный счетчик с последовательным переносом

- •9.2.3.3 Асинхронные реверсивные двоичные счетчики с последовательным переносом

- •9.2.3.4 Синхронный счетчик со сквозным переносом

- •9.2.3.5 Десятичные счетчики

- •9.2.3.6 Счетчики в интегральном исполнении

- •9.2.4 Делители частоты

- •9.2.5 Распределители

- •10. Связь мп-ра и омэвм с аналоговым объектом управления и с пк

- •10.1 Структура типичной локальной микропроцессорной системы управления (лмпсу)

- •10.1.1 Назначение и схемная реализация отдельных узлов лмпсу

- •10.1.1.1 Аналоговый мультиплексор (ампс)

- •10.1.1.2 Устройство выборки-хранения (увх)

- •10.1.1.3 Аналого-цифровой преобразователь (ацп)

- •10.1.1.4 Ведомая однокристальная микроЭвм (омэвм)

- •10.1.1.5 Шинный формирователь (шф)

- •10.1.1.6 Регистры (Рг1...Рг3)

- •10.1.1.7 Схемы согласования уровней (ссу1...Ссу3)

- •10.1.1.8 Цифро-аналоговые преобразователи (цап1...Цап3)

- •10.2 Применение ацп и увх при вводе аналоговой информации в мпс

- •10.2.1 Расчет ацп

- •10.2.2.1 Описание микросхемы к1113 пв1

- •10.2.2.2 Расчет микросхемы к1113 пв1

- •10.2.2.3 Ввод данных от ацп в мпс через ппи в режиме 0

- •10.2.3 Устройство выборки и хранения (увх)

- •10.2.3.1 Обоснование применения увх

- •10.2.3.2 Принцип действия, схема и основные параметры увх

- •10.2.3.3 Функциональные возможности и схема включения микросхемы увх к1100ск2 (кр1100ск2)

- •10.2.4.1 Описание микросхемы max154. Временные диаграммы и режимы работы

- •10.2.4.2 Расчет ацп max154

- •10.3 Применение цап при выводе цифровой информации из мпс

- •10.3.1 Расчет цап на матрице r-2r c суммированием токов

- •10.3.2.1 Описание микросхемы к572 па1

- •10.3.2.2 Расчет цап к572 па1

- •10.3.3.1 Описание микросхемы max506

- •10.3.3.2 Расчет цап max506

- •10.4 Особенности аппаратной и программной реализации модуля ацп-цап мпс

- •10.4.1 Аппаратный уровень:

- •10.4.2 Программный уровень:

- •10.5 Обмен между мп-м (омэвм) и пк по последовательному каналу связи с помощью интерфейса rs-232с

- •10.5.1 Устройство асинхронное программируемое приёмопередающее (уапп)

- •10.5.2 Устройство преобразования уровней (упу)

- •10.5.3 Разъём rs-232с

- •10.5.4 Буферный регистр адреса rs-232c

- •10.5.5 Шинный формирователь

- •10.6 Выбор и расчет датчиков, нормирующих преобразователей и фильтров нижних частот (фнч)

- •10.6.1 Выбор и расчет датчиков и нормирующих преобразователей

- •10.6.1.1 Выбор датчиков

- •10.6.1.2 Выбор нормирующих преобразователей

- •10.6.2 Выбор фнч

- •10.6.3 Расчет фнч

- •10.7 Разработка схемы алгоритма и управляющей программы

9.1.2.1.2 Шифраторы двоично-десятичного кода

Шифраторы двоично-десятичного кода преобразуют входной десятичный (унитарный) код в двоично-десятичный (BCD)-код (код 8421). С выхода такого шифратора параллельно снимается группа двоичных сигналов, из которых каждые четыре (тетрада) отображают в двоичном коде десятичную цифру. Отличие четырехразрядного двоичного кода от четырехразрядного BCD-кода заключается в диапазоне изменения комбинаций выходного кода: в первом случае выходной код изменяется от 0000 до 1111, а во втором – от 0000 до 1001.

В одном байте (восьми битах) можно упаковать (уложить) две десятичные цифры в BCD-коде. Такой формат представления десятичных чисел называется упакованным.

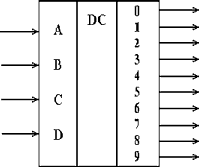

На рисунке 9.6 приведено функциональное обозначение шифратора BCD-кода.

На вход системы поступают двоичные цифры от 0 до 9, которые отображаются на выходе одной тетрадой двоичного кода, принимающей значения от 0000 В до 1001 В.

Рисунок 9.6

9.1.2.1.3 Дешифраторы двоичного кода

Дешифратором (декодером) двоичного кода называют КЦУ, преобразующее входной двоичный код в десятичный (унитарный). Полный дешифратор с m входами имеет 2m выходов. Каждой комбинации входных сигналов соответствует активное значение только одного определенного выходного сигнала. Ниже показана таблица истинности (таблица 9.4) и условное обозначение (рисунок 9.7) трехвходового полного дешифратора с единичными активными значениями выходных сигналов F0...F7.

Рисунок 9.7

Дешифратор реализует восемь различных логических функций:

Таблица 9.4

№ набора |

C |

B |

A |

F0 |

F1 |

F2 |

F3 |

F4 |

F5 |

F6 |

F7 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

2 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

3 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

4 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

5 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

6 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

7 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Если входные переменные рассматривать как двоичную запись чисел, то логическая единица формируется на том выходе, номер которого соответствует десятичному эквиваленту входного двоичного числа.

Рассмотренный дешифратор (таблица 9.4) является преобразователем двоичного кода в унитарный (десятичный).

Приведенные булевы выражения функций F0...F7 можно реализовать на логических элементах в базисах И, ИЛИ, НЕ; И-НЕ или ИЛИ-НЕ, пользуясь методикой изложенной ранее.

В интегральном исполнении выпускаются различные структуры дешифраторов, в которых имеются 2, 3 или 4 входа. В одном корпусе может быть несколько дешифраторов.

Для увеличения функциональных возможностей устройств часто предусматривается использование нескольких дополнительных сигналов управления. В качестве примера на рисунке 9.8 дано изображение микросхемы К555ИД4, содержащей сдвоенный двухвходовый дешифратор с активными нулевыми выходными сигналами.

Рисунок 9.8

Выходные сигналы обоих дешифраторов зависят от комбинации входных сигналов А, В. Синхронизация процесса формирования выходных сигналов F0...F3 для каждого дешифратора задается комбинациями управляющих сигналов V. Работу верхнего дешифратора разрешает комбинация V1=0, V2=1, а работу нижнего- V3=0, V4=0. Введение такого управления расширяет возможности микросхемы при построении более сложных устройств, например, дешифраторов с увеличенным числом входов и выходов.

На рисунке 9.9 показан пример включения двух микросхем К555ИД4 для реализации дешифратора четырехразрядного входного двоичного кода в выходной шестнадцатипозиционный унитарный (десятичный) код. Работу этого дешифратора поясняют таблицы 9.4.1 и 9.4.2.

Рисунок 9.9

Таблица 9.4.1

X3 |

X2 |

Рабочий дешифратор |

0 |

0 |

Нижний ИМС DD1 |

0 |

1 |

Верхний ИМС DD1 |

1 |

0 |

Нижний ИМС DD2 |

1 |

1 |

Верхний ИМС DD2 |

Таблица 9.4.2

-

№ набора

X3

X2

X1

X0

F0

F1

F2

F3

F4

F5

F6

F7

F8

F9

F10

F11

F12

F13

F14

F15

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

0

0

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

3

0

0

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

4

0

1

0

0

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

5

0

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

6

0

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

7

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

8

1

0

0

0

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

9

1

0

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

10

1

0

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

11

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

12

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

13

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

14

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

15

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

Дешифраторы могут быть неполными (имеющими число выходов Nвых<2m, где m – число входных переменных). Например, такие дешифраторы могут использоваться для преобразования двоично-десятичного кода в код, предназначенный для управления десятичным индикатором (дешифраторы 4х10). На рисунке 9.10 показано условное обозначение дешифратора 4х10 (например, микросхемы К555ИД1 или К564ИД1). Схема имеет активные единичные выходные сигналы.

Рисунок 9.10