- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

Variable I:integer;

Variable stim_vector: std_logic_vector(2 downto 0);

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <=i;

stim_vector :=to_vector(i,3);

x0<= stim_vector(0);

x1<= stim_vector(1);

x2<= stim_vector(2);

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;

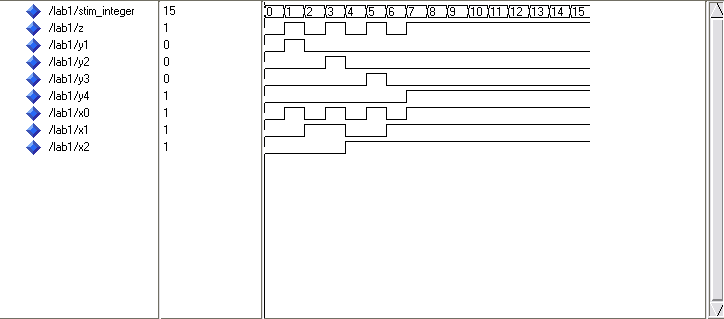

Временные диаграммы:

Как видно из временных диаграмм, теперь результат совпадает с результатом, полученным в пункте 1 данной работы. Это можно объяснить тем, что вынеся оператор вычисления Z из процесса в общую операторную часть архитектурного тела, теперь вначале вычисляются сигналы Xi, а уже после выполнения процесса вычисляется и само значение Z.

9. Модифицируем программу так, чтобы учитывались задержки, полагая задержки перехода 0-1 и 1-0 равными для всех элементов.

Сделаем задержку равную 20 нс для всех элементов.

Текст программы:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1 IS

END lab1;

ARCHITECTURE test1 OF lab1 IS

SIGNAL stim_integer: integer;

SIGNAL z,y1,y2,y3,y4,x0,x1,x2: std_logic;

BEGIN

logic_unit:process(x0,x1,x2) -- процесс, отвечающий за описание функции

-- в форме логических уравнений, в двухуровневую

-- последовательную И-ИЛИ форму

begin

-- z<=(x0 and x1 and x2) or

-- (x0 and y1 and (not x2));

y1<= (not x2) and (not x1) and x0 after 20ns;

y2<= (not x2) and x1 and x0 after 20ns;

y3<= x2 and (not x1) and x0 after 20ns;

y4<= x2 and x1 and x0 after 20ns;

END process;

z<= y1 or y2 or y3 or y4 after 20ns;

Stimulator: PROCESS

Variable I:integer;

Variable stim_vector: std_logic_vector(2 downto 0);

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <=i;

stim_vector :=to_vector(i,3);

x0<= stim_vector(0);

x1<= stim_vector(1);

x2<= stim_vector(2);

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;

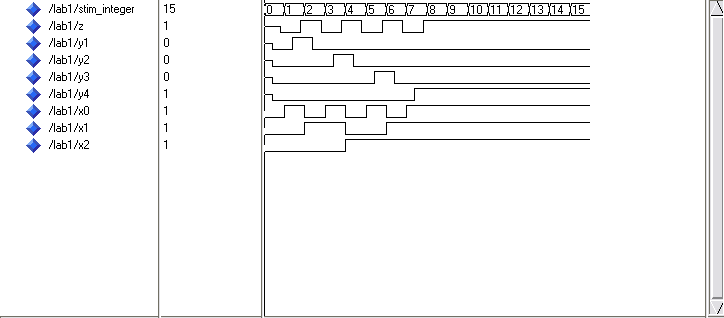

Временные диаграммы:

Теперь мы наблюдаем все сигналы с учетом временных задержек логических элементов.

Выводы по работе

В результате выполнения данной работы мы усвоили общую структуру программы в языке VHDL и получили навыки работы в среде ModelSim.

Также в ходе выполнения данной работы мы получили начальные представления о процессах и их взаимодействиях, получили представление об основных формах представления сигналов и усвоили некоторые способы представления комбинационных схем.