- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3);

z <= stim_vector(0);

END process;

logic_unit_new:process(stim_integer)

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3);

case stim_vector is

when "001"=> z1<='1';

when "011"=> z1<='1';

when "101"=> z1<='1';

when "111"=> z1<='1';

when OTHERS => z1<='0';

end case;

END process;

logic_unit_new2:process(stim_integer) -- тот же процесс, что и в пред. пункте

-- только с использованием case

Variable stim_vector: std_logic_vector(2 downto 0);

VARIABLE x0,x1,x2: std_logic;

begin

stim_vector := to_vector(stim_integer,3);

x0 := stim_vector(0);

x1 := stim_vector(1);

x2 := stim_vector(2);

case x0 is

when '0'=> z2<= '0';

when '1'=> z2<= '1';

when OTHERS => z2 <= '0';

end case;

END process;

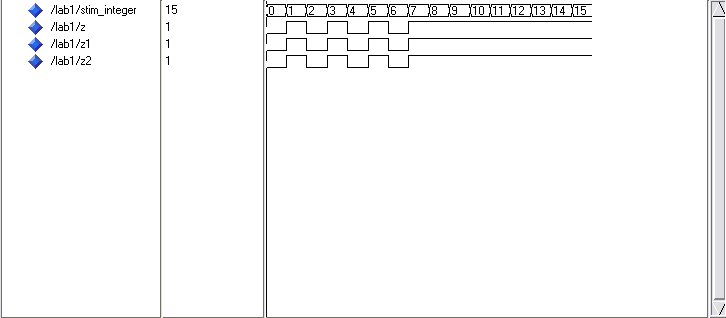

Временные диаграммы:

7. Вызовем к работе файл, созданный по пункту 1. Преобразуем фрагмент программы, обеспечивающей описание функции в форме логических уравнений, в двухуровневую последовательность И-ИЛИ форму, определив выходы логических элементов «И» как сигналы.

Текст модифицированной программы:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1 IS

END lab1;

ARCHITECTURE test1 OF lab1 IS

SIGNAL stim_integer: integer;

SIGNAL z,y1,y2,y3,y4,x0,x1,x2: std_logic;

BEGIN

logic_unit:process(x0,x1,x2) -- процесс, отвечающий за описание функции

-- в форме логических уравнений, в двухуровневую

-- последовательную И-ИЛИ форму

begin

-- z<=(x0 and x1 and x2) or

-- (x0 and y1 and (not x2));

y1<= (not x2) and (not x1) and x0;

y2<= (not x2) and x1 and x0;

y3<= x2 and (not x1) and x0;

y4<= x2 and x1 and x0;

z<= y1 or y2 or y3 or y4;

END process;

Stimulator: PROCESS

Variable I:integer;

Variable stim_vector: std_logic_vector(2 downto 0);

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <=i;

stim_vector :=to_vector(i,3);

x0<= stim_vector(0);

x1<= stim_vector(1);

x2<= stim_vector(2);

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;

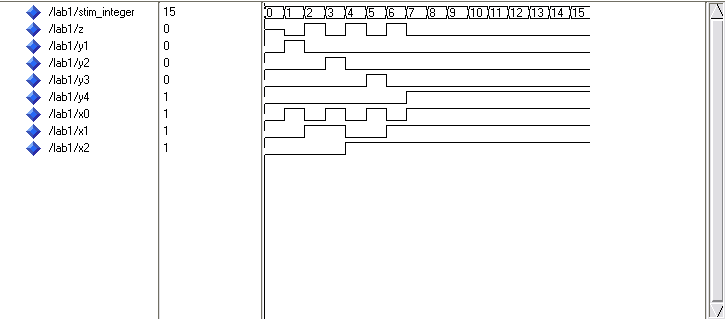

Временные диаграммы:

Как видно из временных диаграмм, результат отличается от полученного ранее в 1 пункте данной работы. Это обусловлено тем, что присвоение значений используемым в процессе сигналам происходит сразу после завершения процесса, а не во время его выполнения.

8. В программе, представленной в предыдущем пункте, оператор вычисления Z оформим как параллельное присваивание.

Для этого перенесем этот оператор в общую операторную часть архитектурного тела.

Получится след. текст программы:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1_15 IS

END lab1_15;

ARCHITECTURE test1 OF lab1_15 IS

SIGNAL stim_integer: integer;

SIGNAL z,y1,y2,y3,x0,x1,x2: std_logic;

BEGIN

logic_unit:process(x0,x1,x2)

begin

y1<= (not x2) and (not x1) and x0;

y2<= (not x2) and x1 and x0;

y3<= x2 and (not x1) and x0;

y4<= x2 and x1 and x0;

END process;

z <= y1 or y2 or y3 or y4; -- перенесенный оператор вычисления Z

Stimulator: PROCESS