- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3);

z<=stim_vector(0);

END process;

logic_unit_new:process(stim_integer) -- новый процесс, реализ. пункт а)

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3);

case stim_vector is

when "001"=> z1<='1';

when "011"=> z1<='1';

when "101"=> z1<='1';

when "111"=> z1<='1';

when OTHERS => z1<='0';

end case;

END process;

compare:process(z,z1) -- новый процесс, реализ. пункт б)

begin

if z/=z1 then

ASSERT false REPORT "Signal z and z1 is not equal! Modelling is stop!"

SEVERITY failure;

end if;

END process;

Stimulator: PROCESS

Variable I:integer;

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <= i;

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;;

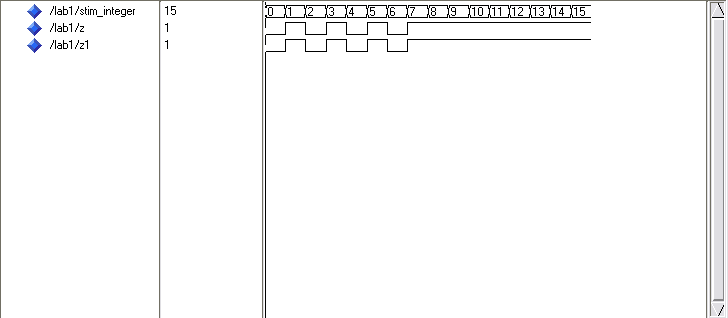

Временные диаграммы:

5. Введем в программу процесс, реализующий функцию на основе разложения Шеннона по одной переменной.

Разложение Шеннона:

![]()

Исходная функция:

![]()

Подформулы разложения:

![]()

В языке VHDL такое вычисление может быть представлено фрагментом:

if x1=0 then z <= <подформула, полученная из f заменой x1 на 0>;

else z <= <подформула, полученная из f заменой x1 на 1>;

end if;

С учетом этого, программа примет след. вид:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1 IS

END lab1;

ARCHITECTURE test1 OF lab1 IS

SIGNAL stim_integer: integer;

SIGNAL z,z1,z2: std_logic;

BEGIN

logic_unit:process(stim_integer)

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3);

z<= stim_vector(0);

END process;

logic_unit_new:process(stim_integer)

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3);

case stim_vector is

when "001"=> z1<='1';

when "011"=> z1<='1';

when "101"=> z1<='1';

when "111"=> z1<='1';

when OTHERS => z1<='0';

end case;

END process;

logic_unit_new2:process(stim_integer) -- новый процесс, реализующий

-- разложение Шеннона

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3);

if (stim_vector(0) = '0') then

z2 <= '0';

else

z2 <= '1';

end if;

END process;

compare:process(z,z1)

begin

if z/=z1 then

ASSERT false REPORT "Signal z and z1 is not equal! Modelling is stop!"

SEVERITY failure;

end if;

END process;

Stimulator: PROCESS

Variable I:integer;

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <= i;

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;

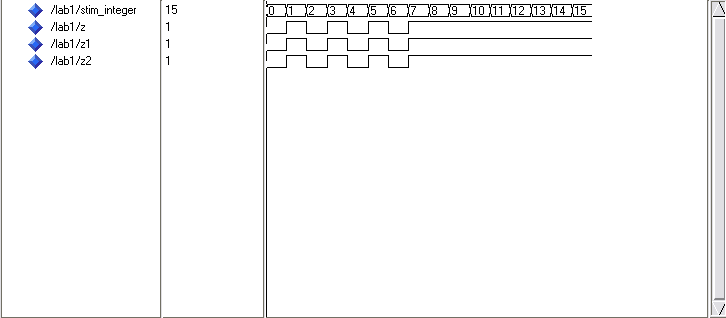

Временные диаграммы:

6. Выполним описание той же логической функции, как и в предыдущем пункте, только с использованием оператора CASE.

Текст модифицированной программы:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1 IS

END lab1;

ARCHITECTURE test1 OF lab1 IS

SIGNAL stim_integer: integer;

SIGNAL z,z1,z2: std_logic;

BEGIN

logic_unit:process(stim_integer)