- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

- •Variable I:integer;

- •Variable stim_vector: std_logic_vector(2 downto 0);

Министерство образования РФ

Санкт-Петербургский государственный

Электротехнический университет «ЛЭТИ»

Кафедра ВТ

Отчет

по лабораторной работе N1

по Языкам проектирования аппаратуры

Вариант 3

Выполнил: Гладилин Г.А.

Группа: 3371

Проверил: Мурсаев А. Х.

Санкт-Петербург

2007

Лабораторная работа №1

«Описание комбинационных схем в языке VHDL»

Цель работы: изучение программы описания комбинационной схемы на языке VHDL, представляемой обучающемуся в качестве образца, и последующая ее модификация с применением некоторых базовых конструкций языка.

Исходный текст программы:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1 IS

END lab1;

ARCHITECTURE test OF lab1 IS

SIGNAL stim_integer: integer;

SIGNAL z,x0,x1,x2: std_logic;

BEGIN

logic_unit:process(x0,x1,x2)

VARIABLE y1: std_logic;

begin

y1:=not x1;

z<=(x0 and x1 and x2) or

(x0 and y1 and (not x2));

END process;

Stimulator: PROCESS

VARIABLE i:integer;

VARIABLE stim_vector: std_logic_vector(2 downto 0);

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <=i;

stim_vector :=to_vector(i,3);

x0<= stim_vector(0);

x1<= stim_vector(1);

x2<= stim_vector(2);

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test;

1. Изменим текст программы так, чтобы реализовать заданную функцию.

Заданная функция:

-

X2 X1 X0

Числовой эквивалент

Z

0 0 0

0

0

0 0 1

1

1

0 1 0

2

0

0 1 1

3

1

1 0 0

4

0

1 0 1

5

1

1 1 0

6

0

1 1 1

7

1

Реализуемая функция:

![]()

Текст измененной программы:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1_8 IS

END lab1_8;

ARCHITECTURE test1 OF lab1_8 IS

SIGNAL stim_integer: integer;

SIGNAL z,x0,x1,x2: std_logic;

BEGIN

logic_unit:process(x0,x1,x2)

begin

z <= x0; -- реализуемая функция

END process;

Stimulator: PROCESS

Variable I:integer;

Variable stim_vector: std_logic_vector(2 downto 0);

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <=i;

stim_vector :=to_vector(i,3);

x0<= stim_vector(0);

x1<= stim_vector(1);

x2<= stim_vector(2);

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;

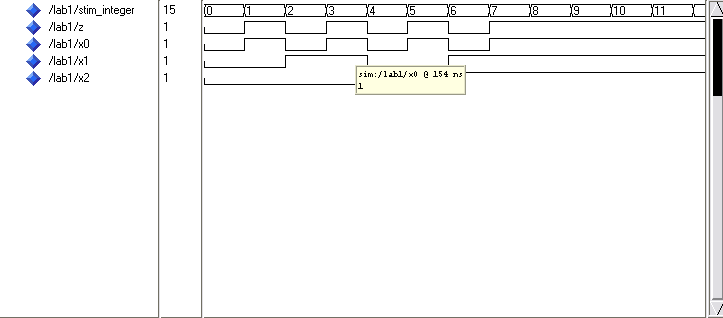

Временные диаграммы:

2. Перестроим программу таким образом, чтобы сигнал от генератора воздействий передавался на логическую схему в форме битового вектора.

Для этого перенесем объявление сигнала из блока stim_vector в раздел описания межблочных соединений, изменим список инициаторов процесса logic_unit и изменим в выражениях для вычисления переменных скалярные входные переменные на элементы вектора.

Текст перестроенной программы будет выглядеть след. образом:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1 IS

END lab1;

ARCHITECTURE test1 OF lab1 IS

SIGNAL stim_integer: integer;

SIGNAL z: std_logic;

SIGNAL stim_vector: std_logic_vector(2 downto 0);

BEGIN

logic_unit:process(stim_vector)

begin

z<= stim_vector(0); -- реализуемая функция в форме битового вектора

END process;

Stimulator: PROCESS

Variable I:integer;

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <= i;

stim_vector <= to_vector(i,3);

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;

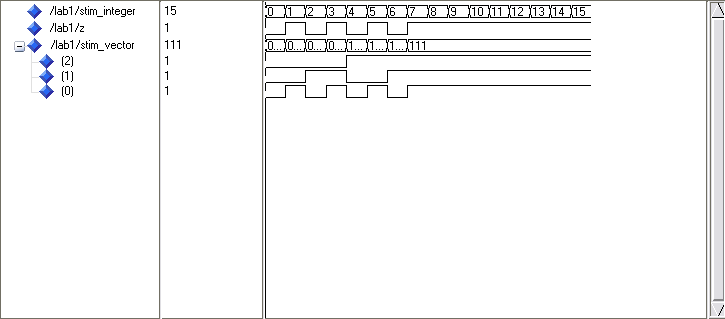

Временные диаграммы:

3. Перестроим программу таким образом, чтобы сигнал от генератора воздействий передавался на логическую схему в форме целого числа.

Для этого наряду с преобразованиями с предыдущего пункта, внутри тела logic_unit произведем преобразование целого в вектор, используя стандартную функцию:

<новая переменная типа std_logic_vector> := to_vector(<целое1>,<целое2>);

где: целое1 – преобразуемое значение или переменная;

целое2 – число битов результата.

Модифицированная программа будет выглядеть след. образом:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1_10 IS

END lab1_10;

ARCHITECTURE test1 OF lab1_10 IS

SIGNAL stim_integer: integer;

SIGNAL z: std_logic;

BEGIN

logic_unit:process(stim_integer)

Variable stim_vector: std_logic_vector(2 downto 0);

begin

stim_vector := to_vector(stim_integer,3); -- преобразование целого в вектор

z<=((not stim_vector(0)) and (not stim_vector(1)) and (not stim_vector(2))) or

(stim_vector(0) and (not stim_vector(1)) and (not stim_vector(2))) or (

(not stim_vector(0)) and stim_vector(1) and stim_vector(2));

-- перестроенная реализуемая функция

END process;

Stimulator: PROCESS

Variable I:integer;

BEGIN

FOR i IN 0 TO 15 LOOP

stim_integer <= i;

WAIT for 50 ns;

END LOOP;

ASSERT false REPORT "End of Stimulation !"

SEVERITY note;

WAIT;

END PROCESS;

END test1;

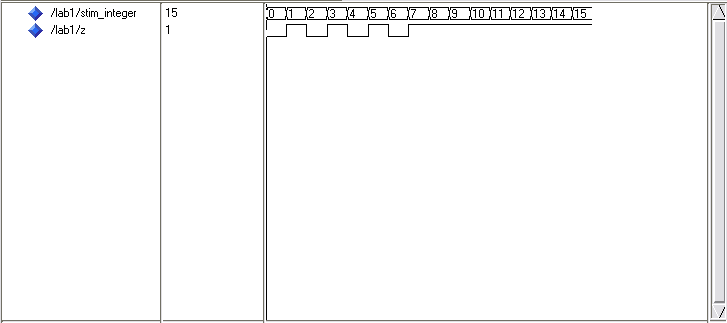

Временные диаграммы:

4. Добавим в программу новый процесс, который:

а). реализует исходную логическую функцию на основе табличного задания функции;

б). сравнивает реализацию логической функции в исходной и модифицированной формах. В случае обнаружения разницы моделирование прекращается и выдает сообщение об ошибке.

Текст программы примет след. вид:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY lab1 IS

END lab1;

ARCHITECTURE test1 OF lab1 IS

SIGNAL stim_integer: integer;

SIGNAL z: std_logic;

SIGNAL z1: std_logic;

BEGIN

logic_unit:process(stim_integer)