- •140010, Г. Люберцы, Московской обл., Октябрьский пр-т, 403.

- •Глава 1. Архитектура реального режима

- •1.1. Память и процессор

- •Глава 1

- •Глава 1

- •1.2. Распределение адресного пространства

- •Глава 1

- •1.3. Регистры процессора

- •Глава 1

- •Глава 1

- •9 7H Шестнадцатернчное обозначение числа

- •Глава 1

- •1.4. Сегментная структура программ

- •Глава 1

- •Глава 1

- •Глава 1

- •1.5. Стек

- •Глава 1

- •1.6. Система прерываний

- •Глава 1

- •Глава I

- •1.7. Система ввода-вывода

- •Глава I

- •Глава 1

- •Глава 2. Основы программирования

- •2.1. Подготовка и отладка программы

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •2.2. Представление данных

- •Глава 2

- •Глава 2

- •2.3. Описание данных

- •Глава 2

- •Глава 2

- •2.4. Структуры и записи

- •Глава 2

- •Глава 2

- •2.5. Способы адресации

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 2

- •2.7. Вызовы подпрограмм

- •Глава 2

- •2.8. Макросредства ассемблера

- •Глава 2

- •Глава 2

- •Глава 2

- •Глава 3. Команды и алгоритмы

- •Глава 3

- •Глава 3

- •Глава 3

- •Глава 3

- •Глава 3

- •Глава 3

- •Глава 3

- •Глава 3

- •3.2. Циклы и условные переходы

- •Глава 3

- •Глава 3

- •3.3. Обработка строк

- •Глава 3

- •3.4. Использование подпрограмм

- •Глава 3

- •Глава 3

- •3.5. Двоично-десятичные числа

- •Глава 3

- •Глава 3

- •3.6. Программирование аппаратных средств

- •Глава 3

- •37Ah Порт управлсш!я

- •Глава 3

- •Глава 3

- •Глава 4. Расширенные возможности

- •4.1. Архитектурные особенности

- •Глава 4

- •4.2. Дополнительные режимы адресации

- •Глава 4

- •4.3. Использование средств 32-разрядных процессоров в программировании

- •Глава 4

- •Глава 4

- •Глава 4

- •4.4. Основы защищенного режима

- •Глава 4

- •Глава 4

- •Глава 4

- •Глава 4

- •Idiv Деление целых чисел со знаком

- •Imul Умножение целых чисел со знаком

- •In Ввод из порта

- •Inc Инкремент (увеличение на 1)

- •Int Программное прерывание

- •Into Прерывание по переполнению

- •Iret Возврат из прерывания

- •1 Lods Загрузка операнда из строки : lodsb Загрузка байта из строки lodsw Загрузка слова из строки

- •Операнд

- •Xadd память, регистр

- •Xchg Обмен данными между операндами

- •Xlat Табличная трансляция

- •Xor Логическое исключающее или

- •Содержание

Глава 4. Расширенные возможности

,, СОВРЕМЕННЫХ МИКРОПРОЦЕССОРОВ

4.1. Архитектурные особенности

Операционная система MS-DOS, язык ассемблера МП 86 и методы программирования микропроцессоров корпорации Intel разрабатывались применительно к 16-разрядному процессору 8086 и тому режиму, который впоследствии получил название реального. Появление процессора 80386 знаменовало собой начало нового этапа в развитии операционных систем и прикладного программирования — этапа многозадачных графических операционных систем защищенного режима типа Windows и 32-разрядных прикладных программ. При этом, как уже отмечалось во введении, все архитектурные средства 86-го процессора входят в состав любого современного процессора, который, таким образом, можно условно разделить на две части — МП 86 и дополнительные средства, обеспечивающие защищенный режим, 32-разрядную адресацию и прочее. Из этих дополнительных средств можно выделить те, которые обеспечивают защищенный режим, и в реальном режиме не используются (во всяком случае, явным образом; в действительности, процессор, даже работая в реальном режиме, использует по крайней мере некоторые из этих средств). Сюда, например, относятся регистры таблиц дескрипторов, регистры тестирования и отладки, привилегированные команды защищенного режима, система страничного отображения адресов и др. С другой стороны, часть новых свойств современных процессоров можно использовать и в реальном режиме, выполняя программы под управлением MS-DOS. Сюда прежде всего относится использование 32-битовых операндов, некоторых новых команд процессора и расширенных возможностей старых команд. Настоящая глава будет в основном посвящена именно этим средствам процессоров 80386, i486 и Pentium, которые в дальнейшем мы будем обобщенно называть 32-разрядными процессорами. Вопрос о программировании защищенного режима слишком сложен, чтобы его можно было осветить в рамках этой книги, хотя основные принципы защищенного режима будут описаны.

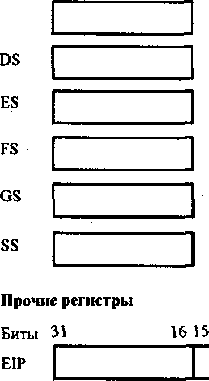

32-разрядные процессоры содержат несколько десятков программно-адресуемых регистров (не считая регистров сопроцессора), из которых шесть являются 16-разрядными, а остальные — 32-разрядными. Регистры принято объединять в семь групп: регистры общего назначения (или регистры данных), регистры-указатели, сегментные регистры, упраатяющие регистры, регистры системных адресов, отладочные регистры и регистры тестирования. Кроме того, в отдельную группу выделяют счетчик команд и регистр флагов. Регистры, используемые в реальном режиме, показаны на рис. 4.1.

Расширенные возможности соврелмнных микропроцессоров

161

Решстры данных

Биты 31 16 15

ЕАХ ЕВХ ЕСХ EDX |

|

АН АХ AL |

|

||

|

ВН ВХ BL |

|

|

||

|

СН СХ CL |

|

|

||

|

DH DX DL |

|

Аккумулятор Базовый регистр Счетчик Регистр данных

Регистры-указатели

Биты 31 16 15

ESI EDI ЕВР ESP |

|

SI |

Индекс источника Индекс приемника Указатель базы Указатель стека |

|

|

||

|

D, |

||

|

|

||

|

ВР |

||

|

|

||

|

SP |

Сегментные регистры

Регистр сегмента команд

Регистр сегмента данных

Регистр дополнительного сегмента данных

Регистр дополнительного сегмента данных

Регистр дополнительного сегмента данных

Регистр сегмента стека

Биты 15 О

Указатель команд Регистр флагов

IP

EFLAFS

CS

Рис. 4.1. Основные регистры 32-разрядных процессоров.

162