Мажоритарное декодирование циклических кодов.

Связь между значениями избыточных и информационных символов линейных кодов позволяет получить несколько эквивалентных выражений для любого символа кодовой комбинации через другие символы. Так например для циклического кода (7,4) из (2.4) можно получить следующие соотношения для a1 :

a1 =

a2![]() a3

a3![]() b1;

b1;

a1 =

a2![]() a4

a4![]() b3;

(2.5)

b3;

(2.5)

a1 =

a4![]() b1

b1![]() b2;

b2;

a1

= a3![]() b2

b2![]() b3;

b3;

Причем последние два соотношения получается сложением соответственно 1-го и 2-го,

2-го и 3-го уравнений в (2.4).

Наличие нескольких эквивалентных выражений для одного символа кодовой комбинации через другие позволяет при декодировании получить оценки для каждого символа и определить значение каждого символа по значениям большинства его оценок, то есть по мажоритарному принципу.

Так, на основании (2.5) , в декодере можно организовать получение следующих пяти оценок для a1:

a11 = a1’

a12

= a2’![]() a3’

a3’![]() b3’

b3’

a13

= a2’![]() a4’

a4’![]() b3’

(2.6)

b3’

(2.6)

a14

= a4’![]() b1’

b1’![]() b2’

b2’

a15

= a3’![]() b2’

b2’![]() b3’

b3’

Причем , оценка a11 является тривиальной. Очевидно , если принятые символы совпадают с переданными ai’= ai и bj’= bj , все оценки будут одинаковыми и совпадут со значением a1.

При несовпадении принимаемых и передаваемых символов , оценки , содержащие нечетное число искаженных символов , будут неправильными (искаженными). Если число искаженных оценок будет меньше количества неискаженных , мажоритарный принцип выработки значения проверяемого символа позволяет определить его правильное значение даже при наличии ошибок при передаче.

Количество оценок

(включая тривиальные), которое необходимо

для исправления ошибок кратности gиспр

, определяется выражением

![]() =

2

=

2

![]() gиспр

+1 ,

gиспр

+1 ,

где![]() - коэффициент связности оценок, численно

равный максимальному числу оценок,

содержащих одинаковые символы.

- коэффициент связности оценок, численно

равный максимальному числу оценок,

содержащих одинаковые символы.

Для приведенных

выше оценок

![]() =2, так как, например, b3’входит

одновременно в две оценки.

=2, так как, например, b3’входит

одновременно в две оценки.

Минимальное

количество оценок будет в случае, если

они независимы (![]() = I),

когда каждый символ принятой комбинации

входит только в одну оценку. При этом

= I),

когда каждый символ принятой комбинации

входит только в одну оценку. При этом

![]() =

2 gиспр

+1 = d0

=

2 gиспр

+1 = d0

Однако независимые

оценки можно получить только для

некоторых линейных кодов. Так для

кода (7,4 } независимых оценок не существует,

можно получить только 5 оценок с

![]() = 2, позволяющих исправлять все

однократные ошибки.

= 2, позволяющих исправлять все

однократные ошибки.

Оценки, аналогичные (2. б), могут быть получены и для остальных символов кодовой комбинации. При этом с помощью мажоритарных элементов можно производить одновременную выработку исправленных значений принятых символов любого линейного кода. Но декодер в этом случае оказывается слишком сложным из-за большого количества мажоритарных элементов и сумматоров по модулю 2.

Использования циклических кодов позволяет получать оценки и вырабатывать исправленные значения символов по очереди, производя циклический сдвиг принятой комбинации и используя одно и то же оборудование для исправления всех символов кодовой комбинаций.

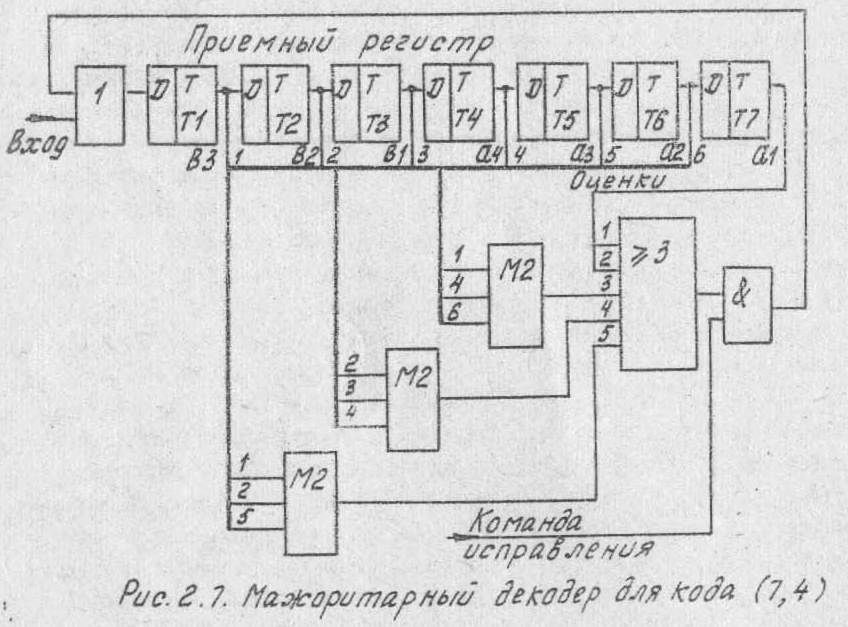

Мажоритарный

декодер для циклического кода (7,4)

(рис.2.7) состоит из приемного сдвигающего

регистра RG

, сумматоров по модулю 2 для выработки

оценок, порогового элемента (

![]() 3), выполняющего роль мажоритарного

элемента, схемы И и входной схемы ИЛИ.

Оценки вырабатываются в соответствии

с (2.6) , за исключением второй. Вторая

оценка заменена на тривиальную a12

= a11

= a1’

, так как ее использование не увеличивает

коэффициента связности, а следовательно,

и необходимого количества оценок, но

позволяет уменьшить объем оборудования

декодера.

3), выполняющего роль мажоритарного

элемента, схемы И и входной схемы ИЛИ.

Оценки вырабатываются в соответствии

с (2.6) , за исключением второй. Вторая

оценка заменена на тривиальную a12

= a11

= a1’

, так как ее использование не увеличивает

коэффициента связности, а следовательно,

и необходимого количества оценок, но

позволяет уменьшить объем оборудования

декодера.

Мажоритарное декодирование циклического кода производится в два этапа. На первом этапе (значение команды исправления равно нулю) в течение 7 тактов производится прием комбинации и запись ее в регистр, так что к концу 7-го такта приема в регистре оказывается записанной вся принятая комбинация (распределение символов принятой комбинации по ячейкам регистра для этого случая указано на рисунке), а на входы порогового элемента (ПЭ) поступают оценки a1. С выхода порогового элемента снимается исправленное значение символа, a1 совпадающее со значением большинства оценок.

На втором этапе (этапе исправления) значение команды исправления равно единице. В течение первого такта исправленное значение а1 записывается через схемы И и ИЛИ в первую, ячейку регистра, а остальные символы принятой комбинации сдвигаются в сторону старших разрядов, так что на месте a1’ к концу первого такта будет записано значение a2’ , на входы ПЭ будут поступать оценки a2 . Во втором такте исправленное значение a2 с выхода ПЭ запишется в первую ячейку регистра и остальные символы сдвинутся и т.д.

В качестве примера в табл. 2.5 приведены значения сигналов в различных точках мажоритарного декодера при приеме комбинации (0 0 1 0 0 1 0), у которой искажен первый избыточный символ (искаженные символы и оценки отмечены точками).

Таблица 2.5

|

Номер Такта Исправ-ления |

Состояние регистра |

Оценки |

Выход ПЭ |

||||||||||

|

|

T1 |

T2 |

T3 |

T4 |

T5 |

T6 |

T7 |

1 |

2 |

3 |

4 |

5 |

|

|

7 такт приема |

0 |

1 |

0* |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1* |

0 |

0 |

|

1 |

0 |

0 |

1 |

0* |

0 |

1 |

0 |

0 |

0 |

1* |

1* |

0 |

0 |

|

2 |

0 |

0 |

0 |

1 |

0* |

0 |

1 |

1 |

1 |

1 |

1 |

0* |

1 |

|

3 |

1 |

0 |

0 |

0 |

1 |

0* |

0 |

0 |

0 |

1* |

0 |

0 |

0 |

|

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0* |

0* |

0* |

1 |

1 |

1 |

1 |

|

5 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

7 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Как видно из

таблицы, исправление искаженного

символа происходит на 5- м такте. После

исправления все оценки становятся

одинаковыми и совпадают со значениями

символа, записанного в старший разряд

регистра. Из таблицы видно также, что

число искаженных оценок в некоторых

случаях может быть меньше

![]() (в I-

м, 2- м и 3- м тактах). При использовании

кодов, не имеющих плотной упаковки, это

обстоятельство позволяет исправлять

часть ошибок кратности большей, чем

(d0-1)/2

, что является одним из существенных

достоинств мажоритарного декодирования.

(в I-

м, 2- м и 3- м тактах). При использовании

кодов, не имеющих плотной упаковки, это

обстоятельство позволяет исправлять

часть ошибок кратности большей, чем

(d0-1)/2

, что является одним из существенных

достоинств мажоритарного декодирования.

Характеристика исследуемого кода.

При выполнении лабораторной работы исследуется линейный циклический код (15,6) с кодовым расстоянием d0=6. Код порождается полиномом

g(t)= t9 + t8 + t5 + t4 + t3 + 1 (2.7)

и позволяет исправлять все однократные и двукратные ошибки и одновременно обнаруживать все трехкратные ошибки. Порождающая матрица кода имеет вид

1

0 0 0 0 0 1 1 0 0 1 1 1 0 0

1

0 0 0 0 0 1 1 0 0 1 1 1 0 0

0 1 0 0 0 0 0 1 1 0 0 1 1 1 0

G = 0 0 1 0 0 0 0 0 1 1 0 0 1 1 1 (2.8)

0 0 0 1 0 0 1 1 0 1 0 1 1 1 1

0 0 0 0 1 0 1 0 1 0 0 1 0 1 1

0 0 0 0 0 1 1 0 0 1 1 1 0 0 1

а избыточные символы связаны с информационными следующими соотношениями:

b1

= a1![]() a4

a4![]() a5

a5![]() a6;

a6;

b2

= a1![]() a2

a2![]() a4;

a4;

b3

= a2![]() a3

a3![]() a5;

a5;

b4

= a3![]() a4

a4![]() a6;

a6;

b5

= a1![]() a6;

(2.9)

a6;

(2.9)

b6

= a1![]() a2

a2![]() a4

a4![]() a5

a5![]() a6;

a6;

b7

= a1![]() a2

a2![]() a3

a3![]() a4;

a4;

b8

= a2![]() a3

a3![]() a4

a4![]() a5;

a5;

b8

= a3![]() a4

a4![]() a5

a5![]() a6.

a6.

Для кода существует 6 независимых оценок каждого символа:

a11 = a1’

a12

= a5’![]() b7’

b7’![]() b8’

b8’

a13

= b3’![]() b4’

b4’![]() b6’

(2.10)

b6’

(2.10)

a14

= a2’![]() a4’

a4’![]() b2’

b2’

a15

= a3’![]() b1’

b1’![]() b9’

b9’

a16

= a6’![]() b5’

,

b5’

,

позволяющих реализовать мажоритарное декодирование принятых комбинаций.

Параллельное кодирующее устройство для исследуемого кода может быть реализовано на основе выражений для избыточных символов и оказывается несколько сложнее циклического кодера (рис.2.8).

Работа циклического кодера для исследуемого кода отличается от работы кодера для кода (7,4) только тем, что процесс деления производится в течение 6 тактов, а в течение остальных 9 тактов остаток подается на выход за информационными символами. Параллельный декодер для кода (15,б) оказывается слишком громоздким, так как в данном случае в параллельном декодере надо организовать выработку 9 сигналов Sj , по которым дешифратор должен вырабатывать 29 = 512 сигналов исправления.

Циклический декодер в данном случае (рис.2.9) оказывается значительно проще параллельного.

Работает циклический декодер для исследуемого кода аналогично рассмотренному декодеру для кода (7,4). Однако исследуемый декодер имеет и некоторые особенности. Первая из них заключается в том, что для исправления двукратных ошибок дешифратор состояний регистра содержит не один выход (как для кода (7,4)), а 10 выходов, которые объединены схемой ИЛИ. Состояния регистра g(t), при которых сигнал исправления становится равным I, и номера выходов дешифратора, на которых появляются единичные сигналы исправления, приведены в табл. 2.6.

При однократной ошибке сигнал исправления всегда появляется при наличии I в триггере Т9 через первый выход дешифратора (как и в декодере для кода (7,4)). При двукратной ошибке сигнал исправления может появляться при наличии двух единиц в регистре g(t) .Вторая особенности рассматриваемого декодера заключается в том, что в общем случае процесс исправления производится не за n (15) , а за 2 (30) тактов. За 15 тактов исправляются все однократные ошибки. При наличии двух искаженных символов, разделенных не менее, чем девятью неискаженными, процесс исправления производится в течение 30 тактов.

Таблица 2.6

|

Состояние регистра g(t) |

Номер выхода дешифратора

|

||||||||

|

TI

|

Т2

|

T3

|

Т4

|

Т5

|

Тб

|

Т7

|

Т8

|

Т9

|

|

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

I

|

1

|

|

0

|

0

|

-0

|

0

|

0

|

0

|

0

|

I

|

I

|

3

|

|

0

|

0

|

0

|

0

|

0

|

0

|

I

|

0

|

I

|

5

|

|

0

|

0

|

0

|

0

|

0

|

I

|

0

|

0

|

I

|

9

|

|

0

|

0

|

0

|

0

|

I

|

0

|

0

|

0

|

I

|

17

|

|

0

|

0

|

0

|

I

|

0

|

0

|

0

|

0

|

I

|

33

|

|

0

|

0

|

I

|

0

|

0

|

0

|

0

|

0

|

I

|

65

|

|

0

|

I

|

0

|

0

|

0

|

0

|

0

|

0

|

I

|

129

|

|

I

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

I

|

157

|

Мажоритарный декодер для исследуемого кода (рис,2.10), вырабатывающий значения исправляемых символов по большинству оценок (2.8), содержит в отличие от рассмотренного выше, два пороговых элемента и триггер фиксации сигнала обнаружения ошибки. Пороговый элемент ПЭ1 вырабатывает исправленное значение символа, находящегося в триггер TI5 приемного регистра. На выходе ПЭ1 значение сигнала равно 1 только в том случае, когда значение 4-х или более оценок из 6 равно I.

Пороговый элемент ПЭ2 служит для обнаружения трехкратных ошибок, которые не могут быть исправлены. В тех случаях, когда 3 из 6 оценок искажены (значения 3-х оценок равны I, а трех -0), на выходе ПЭ2 значение сигнала равно I, а на выходе ПЭ1 - 0, эти сигналы через схему “Запрет.” устанавливают триггер обнаружения ошибки в состояние I. Наличие же единичного сигнала на выходе ПЭ1 запрещает запуск триггера обнаружения ошибки.

Следует отметить, что для исследуемого кода мажоритарный декодер позволяет исправлять часть трехкратных и даже четырехкратных ошибок. Исправление ошибок кратности выше двух происходит всегда, когда при выработке значения искаженного символа (находящегося в 15- и, разряде приемного регистра), остальные искаженные символы входят в одну оценку и компенсируют друг друга. При этом большинство оценок оказываются правильными и сразу происходит исправление одного из символов, так что к следующему такту кратность ошибки будет на единицу меньше.