Лабораторная работа 1

Тема: Учебно-отладочное устройство К580

Цели работы:

Ознакомиться со структурной схемой учебно-отладочного устройства

Ознакомиться со структурной схемой и принципом работы МП КР580 ВМ80

Система команд МП

Распределение памяти МПС

Программная оболочка учебно-отладочного устройства К580

1. Ознакомление со структурной схемой учебно-отладочного устройства

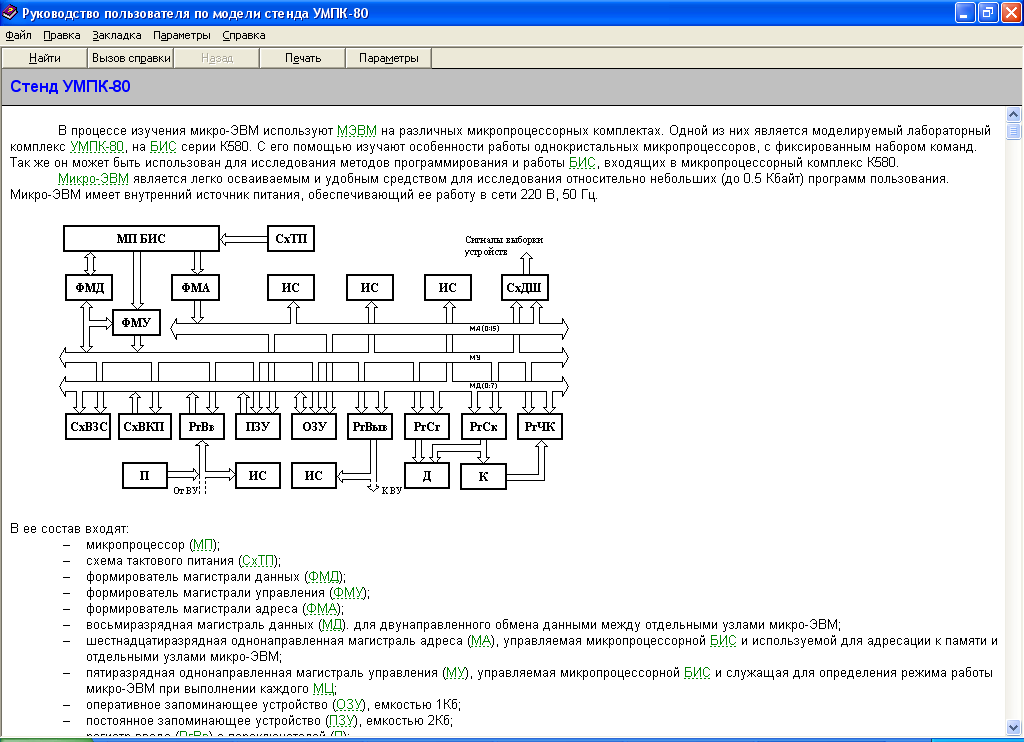

В процессе изучения микро-ЭВМ используют МЭВМ на различных микропроцессорных комплектах. Одной из них является моделируемый лабораторный комплекс УМПК-80, на БИС серии К580. С его помощью изучают особенности работы однокристальных микропроцессоров, с фиксированным набором команд. Так же он может быть использован для исследования методов программирования и работы БИС, входящих в микропроцессорный комплекс К580.

Микро-ЭВМ является легко осваиваемым и удобным средством для исследования относительно небольших (до 0.5 Кбайт) программ пользования. Микро-ЭВМ имеет внутренний источник питания, обеспечивающий ее работу в сети 220 B, 50 Гц.

Рисунок 1 – Структурная схема КР580

В ее состав входят:

– микропроцессор (МП);

– схема тактового питания (СхТП);

– формирователь магистрали данных (ФМД);

– формирователь магистрали управления (ФМУ);

– формирователь магистрали адреса (ФМА);

– восьмиразрядная магистраль данных (МД). для двунаправленного обмена данными между отдельными узлами микро-ЭВМ;

– шестнадцатиразрядная однонаправленная магистраль адреса (МА), управляемая микропроцессорной БИС и используемой для адресации к памяти и отдельными узлами микро-ЭВМ;

– пятиразрядная однонаправленная магистраль управления (МУ), управляемая микропроцессорной БИС и служащая для определения режима работы микро-ЭВМ при выполнении каждого МЦ;

– оперативное запоминающее устройство (ОЗУ), емкостью 1Кб;

– постоянное запоминающее устройство (ПЗУ), емкостью 2Кб;

– регистр ввода (РгВв) с переключателей (П);

– регистр вывода с индикацией состояний светодиодами (РгВыв);

– схема выдачи кода прерывания (СхВКПР);

– схема дешифрации адреса (СхДША);

– схема выдачи звукового сигнала (СхВЗС);

– клавиатура управления и ввода данных (К), состоящей из 9 клавиш управления, и 16 клавиш для введения шестнадцатеричных кодов чисел;

– регистр чтения клавиатуры (РгЧК);

– шестиразрядный восьмисегментный дисплей (Д), четыре разряда которого служат для отображения кода адреса в шестнадцатеричной системе исчисления, а два – для отображения данных;

– РгСК - регистр сканирования;

– РгСг - регистр сегментов дисплея;

– магистрали микро-ЭВМ, а также входной и выходной регистры имеют индикационные светодиоды (ИС), указывающие их состояние.

Открытая конструкция и наличие большого количества средств индикации позволяют наглядно исследовать процесс передачи и преобразования информации в микро-ЭВМ.

2. Ознакомление со структурной схемой и принципом работы мп кр580 вм80

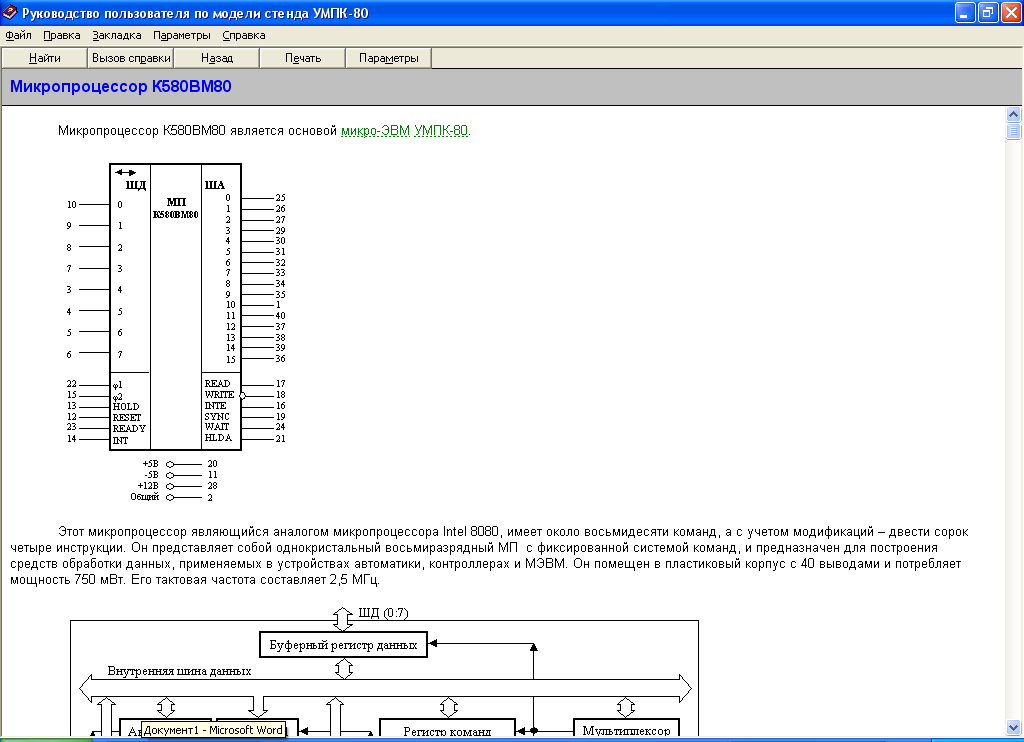

Микропроцессор К580ВМ80 является основой микро-ЭВМ УМПК-80.

Рисунок 2 - УГО микропроцессора

Этот микропроцессор являющийся аналогом микропроцессора Intel 8080, имеет около восьмидесяти команд, а с учетом модификаций – двести сорок четыре инструкции. Он представляет собой однокристальный восьмиразрядный МП с фиксированной системой команд, и предназначен для построения средств обработки данных, применяемых в устройствах автоматики, контроллерах и МЭВМ. Он помещен в пластиковый корпус с 40 выводами и потребляет мощность 750 мВт. Его тактовая частота составляет 2,5 МГц.

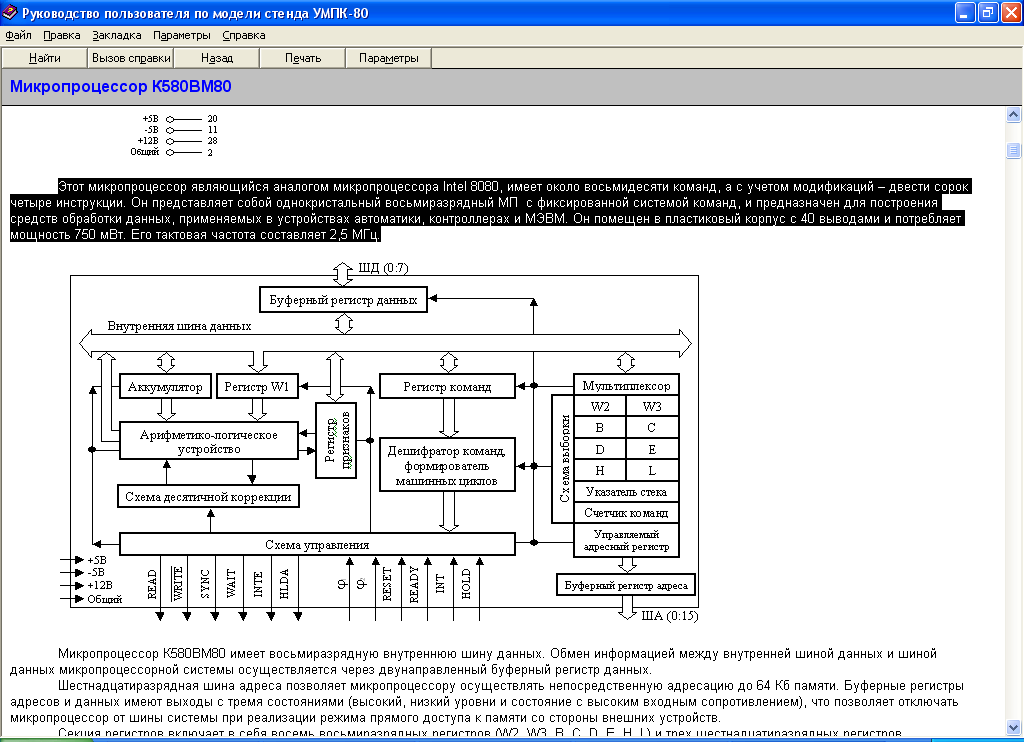

Рисунок 3 - Структурная схема микропроцессора

Микропроцессор К580ВМ80 имеет восьмиразрядную внутреннюю шину данных. Обмен информацией между внутренней шиной данных и шиной данных микропроцессорной системы осуществляется через двунаправленный буферный регистр данных.

Шестнадцатиразрядная шина адреса позволяет микропроцессору осуществлять непосредственную адресацию до 64 Кб памяти. Буферные регистры адресов и данных имеют выходы с тремя состояниями (высокий, низкий уровни и состояние с высоким входным сопротивлением), что позволяет отключать микропроцессор от шины системы при реализации режима прямого доступа к памяти со стороны внешних устройств.

Секция регистров включает в себя восемь восьмиразрядных регистров (W2, W3, B, C, D, E, H, L) и трех шестнадцатиразрядных регистров (программный счетчик, указатель стека, управляемый адресный регистр). Регистры B, C, D, E, H, L являются регистрами общего назначения (РОН), в зависимости от типа выполняемой команды могут использоваться либо как самостоятельные регистры, либо как шестнадцатиразрядные пары BC, DE, HL. Буферные регистры W2 и W3 не являются программно-доступными регистрами и используются для выполнения команд внутри БИС микропроцессора.

Программный счетчик (PC) содержит адрес памяти, по которому находится текущая команда. Содержимое счетчика автоматически изменяется в течение каждого цикла команды. Указатель стека (SP) содержит адрес памяти, начиная с которого ее можно применять для хранения и восстановления содержания программно-доступных регистров МП БИС.

Управляемый адресный регистр предназначен для приема информации из других регистров и передачи ее в буферный регистр адреса. В процессе передачи этот программно-недоступный регистр может увеличивать или уменьшать на единицу передаваемую информацию, что упрощает адресацию.

Арифметико-логический блок (АЛБ) выполняет арифметические и логические операции над данными, представленными в двоичной форме под воздействием схемы управления (СУ) микропроцессорной БИС. Он включает в себя восьмиразрядное арифметико-логическое устройство (АЛУ), схему десятичной коррекции (ДК), построенной на базе ПЗУ, восьмиразрядный регистр признаков аккумулятор и буферный регистр (W1). Арифметико-логический блок позволяет осуществить арифметические операции сложения и вычитания, а также основные логические операции (И, ИЛИ, исключающее ИЛИ) и сдвиг. При проведении операций одно число всегда берется из аккумулятора, а другое - из буферного регистра W1. Результат выполнения операции поступает на внутреннюю шину данных или записывается в регистр накопителя. Блок десятичной коррекции при необходимости осуществляет перевод содержимого регистра накопителя из двоичной в двоично-десятичную форму.

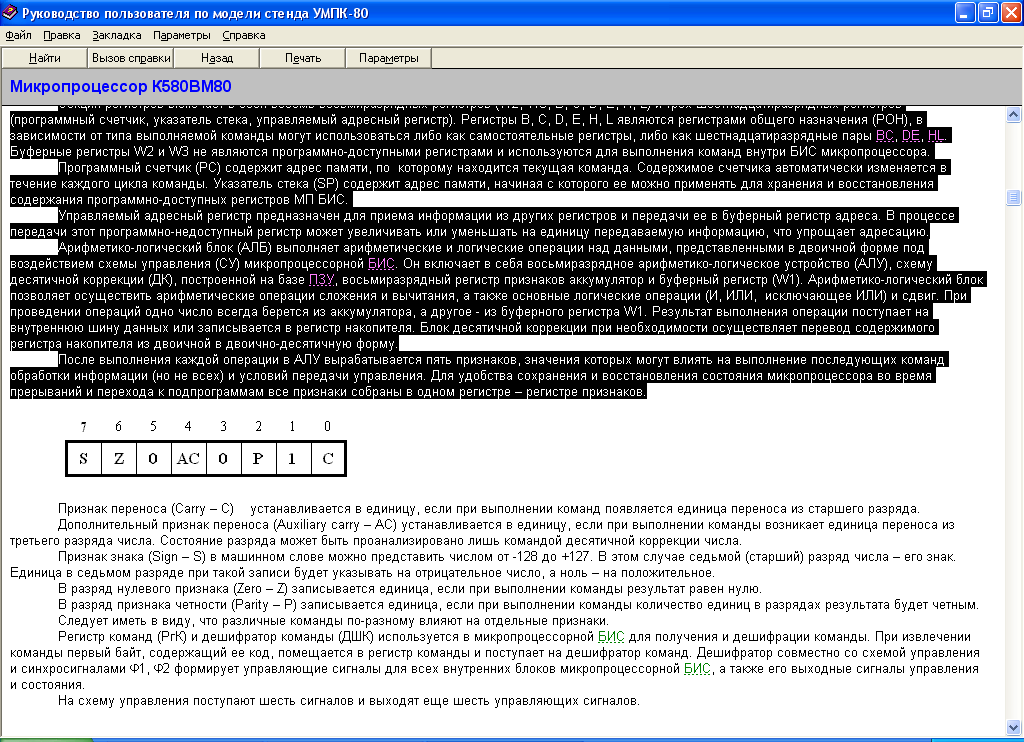

После выполнения каждой операции в АЛУ вырабатывается пять признаков, значения которых могут влиять на выполнение последующих команд обработки информации (но не всех) и условий передачи управления. Для удобства сохранения и восстановления состояния микропроцессора во время прерываний и перехода к подпрограммам все признаки собраны в одном регистре – регистре признаков.

Рисунок 4 – Регистр признаков

Признак переноса (Carry – C) устанавливается в единицу, если при выполнении команд появляется единица переноса из старшего разряда.

Дополнительный признак переноса (Auxiliary carry – AC) устанавливается в единицу, если при выполнении команды возникает единица переноса из третьего разряда числа. Состояние разряда может быть проанализировано лишь командой десятичной коррекции числа.

Признак знака (Sign – S) в машинном слове можно представить числом от -128 до +127. В этом случае седьмой (старший) разряд числа – его знак. Единица в седьмом разряде при такой записи будет указывать на отрицательное число, а ноль – на положительное.

В разряд нулевого признака (Zero – Z) записывается единица, если при выполнении команды результат равен нулю.

В разряд признака четности (Parity – P) записывается единица, если при выполнении команды количество единиц в разрядах результата будет четным.

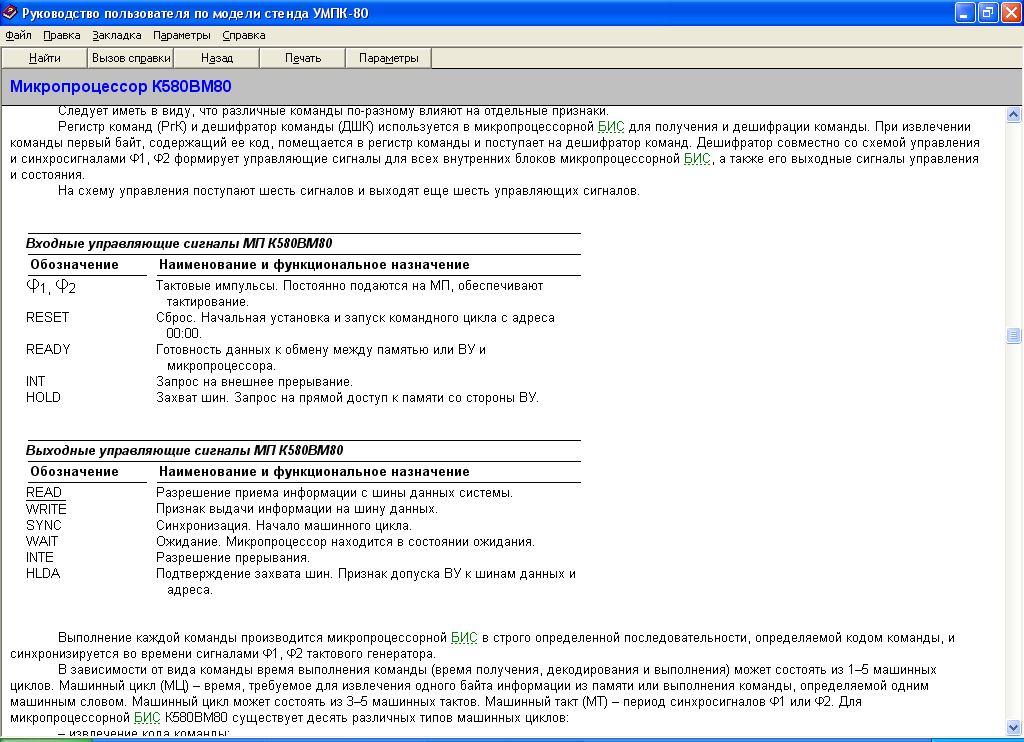

Следует иметь в виду, что различные команды по-разному влияют на отдельные признаки.

Регистр команд (РгК) и дешифратор команды (ДШК) используется в микропроцессорной БИС для получения и дешифрации команды. При извлечении команды первый байт, содержащий ее код, помещается в регистр команды и поступает на дешифратор команд. Дешифратор совместно со схемой управления и синхросигналами 1, 2 формирует управляющие сигналы для всех внутренних блоков микропроцессорной БИС, а также его выходные сигналы управления и состояния.

На схему управления поступают шесть сигналов и выходят еще шесть управляющих сигналов.