- •Кафедра спеціалізованих комп’ютерних систем

- •Пояснювальна записка до дипломної роботи

- •Загальна частина

- •Аналіз способів кодування інформації

- •1.2. Перевірка парності

- •1.3.1. Вимоги складності

- •1.3.2. Двійкова арифметика без урахування переносів

- •1.4 Код хеммінга

- •1 Біт перевіряє біти 1,3,5,7,9,11,13,15,17,19,21.

- •001011100000101101110 Вийде 001001100000101101110

- •1.5 Код Ріда - Соломона

- •2. Спеціальна частина

- •2.1 Розробка пристрою кодування інформації методом ХемМінга

- •2.2 Розробка пристрою декодування інформації методом Хемінга

- •2.3 Реалізація кодерА - декодера на базі імс к555вж1

- •2.3.1 Цоколевка імс к555вж1 (sn74ls630)

- •2.3.2 Розробка принципової схеми пристрою

- •2.3.3 Принцип роботи пристрою

- •3. Економічна частина

- •4 Охорона праці та техніки безпеки

- •4.1 Потенційно небезпечні та шкідливі виробничі фактори

- •4.2 Забезпечення електробезпеки

- •4.3 Забезпечення санітарно-гігієнічних вимог до приміщень навчальних лабораторій

- •4.4 Протипожежний захист

- •Висновок

- •Список використанної літератури

1.5 Код Ріда - Соломона

Код Ріда-Соломона дозволяє скорегувати одну помилку в одному блоці даних. При його використанні до кожного блоку інформації додаються додаткові два елементи X і Y, значення яких знаходяться виходячи з умов:

для трьох одиниць інформації (байт):

байт1 + байт2 + байт3 + X + Y = 0

байт1 + 2 * байт2 + 3 * байт3 + 4 * X + 5 * Y = 0

для розрахунку конкретних значень X і Y для кодування трьох байт:

Y = 3 * байт1 + 2 * байт2 + байт3Х = – 4 * байт1 – 3 * байт2 – 2 * байт3

Тепер для з'ясування помилки і її корекції застосовуємо такі розрахунки:

Значення_помилки = байт1 + байт2 + байт3 + X + Y

так як раніше (до виникнення помилки) ця сума дорівнювала 0, то тепер вона дорівнює безпосередньо значенням помилки, яке досить просто відняти з недоброякісного байта. У разі якщо блок прийнятий безпомилково, то Значення_помилки = 0. Тепер знайдемо байт який треба виправляти:

N = байт1 + 2 * байт2 + 3 * байт3 + 4 * X + 5 * Y

Номер_помилкового_байта = N / Значення_помилки

При реалізації цього в реальний алгоритм необхідно обов'язково здійснювати перевірку на те чи існує помилка в блоці чи ні, тобто Значення_помилки = 0 чи ні, інакше отримуємо ділення на нуль.

Якщо необхідно захистити кодом Ріда-Соломона блок даних більше 3х байт, то формули розрахунку коригувальних значень лише трохи змінюються (для 16 байт):

Y = 16 * байт1 + 15 * байт2 + 14 * байт3 + ... + байт16Х = – 17 * байт1 – 16 * *байт2 – 15 * байт3 – ... – 2 * байт16

Значення_помилки = байт1 + байт2 + байт3 + ... + X + YN = байт1 + 2 * байт2 + 3 * байт3 + ... + 16 * байт16 + 17 * X * Y + 18

Даним кодом незручно захищати блоки інформації менше 4 байт, так як довжина контрольних параметрів X і Y повинна бути як мінімум 4 байти, 2 байти (DW) для X та 2 байти Y, тобто виходить, що до блоку даних з 4 байт буде доданий коригувальний блок з 4 байт.

Але що робити, якщо виникло дві або більше помилок у блоці? Як одна з ознак виникнення двох помилок можна вважати отримання як номер_помилкового_байта дробного числа, наприклад якщо у блоці з нулів зустрінеться 2 одиниці (дві помилки), у третьому і четвертому байтах, то Номер_помилкового_байта = 3.5 але якщо 4 одиниці, відповідно до 3, 4 і 5 байтах то Номер_помилкового_байта = 4.

2. Спеціальна частина

Для візуалізації процесу завадостійкого кодування слід розробити пристрій, який допоможе зрозуміти принцип роботи методу Хеммінга. Кодер - декодер будемо розробляти на основі ІМС К555ВЖ1.

2.1 Розробка пристрою кодування інформації методом ХемМінга

Кодер, перетворює 32-х бітне слово в 38-ми розрядний код Хеммінга, після чого слово зберігається в пам'яті або передається через шини і т.д. В процесі передачі або зберігання в слові може статися помилка, тому декодер не просто декодує слово, але і виправляє деякі помилки. Процес кодування і декодування можна представити у вигляді блок-схеми наведеної нижче.

Рис. 2.1 — Блок-схема кодування-декодування

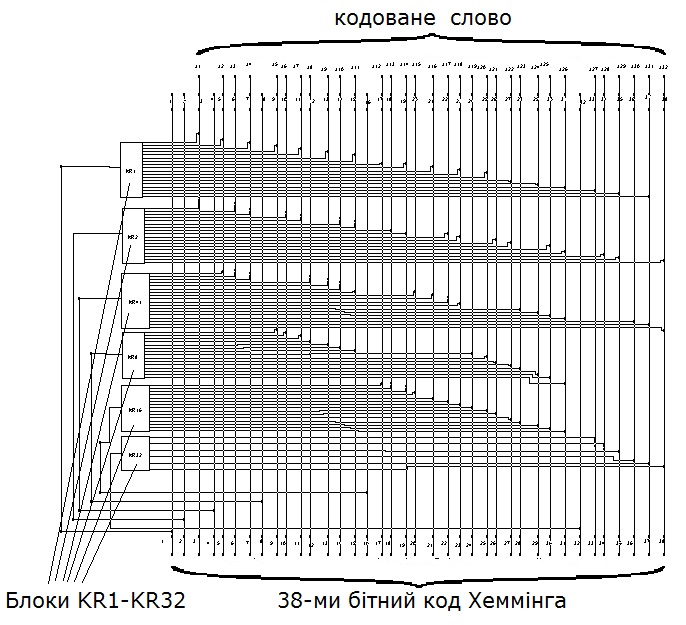

Рис.2.2 — Схема кодера

На входи а1, а2...а32 подається кодоване слово. Блоки KR1, KR2, KR4, KR8, KR16 і KR32 формують контрольні розряди (біти парності). Весь процес кодування зводиться до формування контрольних розрядів і зсуву наявних розрядів. Так, перший біт слова стає третім бітом коду, а 2-й – 5м, 1,2,4,8,16,32 біти - контрольні. Таким чином, в результаті кодування 32-х бітне слово стає 38-ми бітним.

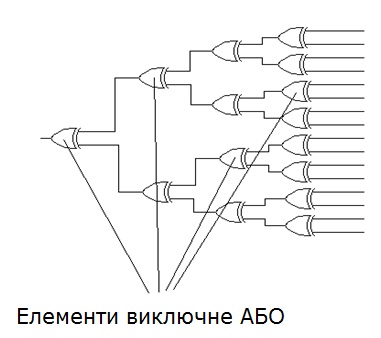

Блоки KR1, KR2, KR4, KR8, KR16 і KR32 зібрані на елементах виключне АБО. Отже, блок KR1 формує 1-й контрольний розряд підраховуючи парність 3,5,7,9,11,13,15,17,19,21,23,25,27,29,31,33,35 і 37 бітів, якщо кількість одиниць в цих розрядах парне, то контрольний біт дорівнює нулю, якщо непарне – одиниці.

Аналогічно блок KR2 формує 2-й контрольний розряд, підраховуючи парність 3,6,7,10,11,14,15,18,19,22,23,26,27,30,31,34,35 і 38 бітів, якщо кількість одиниць в цих розрядах парне, то контрольний біт дорівнює нулю, якщо непарне – одиниці.

Блок KR4 формує 4-й контрольний біт перевіряючи 5,6,7,12,13,14,15,20,21,22,23,28,29,30,31,36,37 і 38 біти.

Блок KR8 формує 8-й контрольний біт перевіряючи 9,10,11,12,13,14,15,24,25,26,27,28,29,30 і 31 біти.

Блок KR16 формує 16-й контрольний біт перевіряючи 17,18,19,20,21,22,23,24,25,26,27,28,29,30 і 31 біти.

Блок KR32 формує 32-й контрольний біт перевіряючи 33,34,35,36,37 і 38 біти.

Рис.2.3 — Схема блоків KR1-KR32

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

KR1 |

|

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

● |

|

KR2 |

|

|

● |

|

|

● |

● |

|

|

● |

● |

|

|

● |

● |

|

|

● |

● |

|

|

● |

● |

|

|

● |

● |

|

|

● |

● |

|

|

● |

● |

|

|

● |

KR4 |

|

|

|

|

● |

● |

● |

|

|

|

|

● |

● |

● |

● |

|

|

|

|

● |

● |

● |

● |

|

|

|

|

● |

● |

● |

● |

|

|

|

|

● |

● |

● |

KR8 |

|

|

|

|

|

|

|

|

● |

● |

● |

● |

● |

● |

● |

|

|

|

|

|

|

|

|

● |

● |

● |

● |

● |

● |

● |

● |

|

|

|

|

|

|

|

KR16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

● |

● |

● |

● |

● |

● |

● |

● |

● |

● |

● |

● |

● |

● |

● |

|

|

|

|

|

|

|

KR32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

● |

● |

● |

● |

● |

● |

Рис.2.4 — Контрольні розряди блоків KR1-KR32