- •Вычислительные машины, системы и сети

- •Тема 1. Введение в предмет

- •Умножение чисел в дополнительных кодах

- •Операция умножения над обратными кодами сомножителей

- •Выполнение операции сложения над числами с плавающей запятой

- •6. Стадии выполнения команды и способы адресации

- •Тема 2. Оcновные архитектурные понятия Лекция 4. Определение понятия "архитектура"

- •Архитектура системы команд. Классификация процессоров (cisc и risc)

- •Лекция 5. Методы адресации и типы данных Методы адресации

- •Типы команд

- •Команды управления потоком команд

- •Типы и размеры операндов

- •Тема 3. Функциональная структура и организация процессора

- •Структура конвейера процессора р6

- •Процессор Pentium Pro

- •Характеристики процессоров р6

- •Характеристики процессоров amd

- •Форматы чисел блоков sse

- •Лекция 12: Сравнительный анализ процессоров с различной архитектурой Особенности процессоров с архитектурой sparc компании Sun Microsystems

- •Процессоры pa-risc компании Hewlett-Packard

- •Процессор mc88110 компании Motorola

- •Особенности архитектуры Alpha компании dec

- •Особенности архитектуры power компании ibm и PowerPc компаний Motorola, Apple и ibm

- •Архитектура power

- •Эволюция архитектуры power в направлении архитектуры PowerPc

- •Тема 4. Структурные модели современных системных плат

- •Тема 5. Организация памяти в эвм

- •2. Постоянные и полупостоянные запоминающие устройства

- •3. Оперативные запоминающие устройства

- •4. Характеристики обмена и типы оперативной памяти

- •7. Сегментация памяти

- •8. Страничная организация памяти

- •Тема 6. Организация ввода-вывода

- •Системные и локальные шины

- •Устройства ввода/вывода Основные типы устройств ввода/вывода

- •2.1. Шины микропроцессорной системы

- •2.2. Циклы обмена информацией

- •2.3. Прохождение сигналов по магистрали

- •Тема 2. Оценка производительности вычислительных систем

- •Тема 5. Многопроцессорные системы Лекция 18: Классификация систем параллельной обработки данных

- •Многопроцессорные системы с общей памятью

- •Многопроцессорные системы с локальной памятью и многомашинные системы

- •Тема 9. Организация микроконтроллеров

- •4.1. Классификация и структура микроконтроллеров

- •4.2. Процессорное ядро микроконтроллера

- •Тема 10. Однокристальные микроконтроллеры серии pic

- •5.1. Основные особенности микроконтроллеров серии pic

- •5.2. Микроконтроллеры подгруппы pic16f8x

- •Тема 11. Проектирование устройств на микроконтроллерах

- •6.1. Разработка микропроцессорной системы на основе микроконтроллера

- •Тема 12. Системы высокой готовности и отказоустойчивые системы

- •Подсистемы внешней памяти высокой готовности

- •Требования, предъявляемые к системам высокой готовности

- •Конфигурации систем высокой готовности

- •Требования к системному программному обеспечению

- •Требования высокой готовности к прикладному программному обеспечению

- •Требования к сетевой организации и к коммуникациям

- •Базовая модель vax/vms кластеров

- •Критерии оценки кластеров Gartner Group

- •Кластеры Alpha/osf компании dec

- •Unix-кластеры компании ibm

- •Кластеры at&t gis

- •Кластеры Sequent Computer Systems

- •Системы высокой готовности Hewlett-Packard

- •Кластерные решения Sun Microsystems

- •Отказоустойчивые решения Data General

- •Список сокращений

Лекция 5. Методы адресации и типы данных Методы адресации

В машинах к регистрами общего назначения метод (или режим) адресации объектов, с которыми манипулирует команда, может задавать константу, регистр или ячейку памяти. Для обращения к ячейке памяти процессор прежде всего должен вычислить действительный или эффективный адрес памяти, который определяется заданным в команде методом адресации.

На рис. 3 представлены все основные методы адресации операндов, которые реализованы в компьютерах, рассмотренных в настоящем обзоре. Адресация непосредственных данных и литеральных констант обычно рассматривается как один из методов адресации памяти (хотя значения данных, к которым в этом случае производятся обращения, являются частью самой команды и обрабатываются в общем потоке команд). Адресация регистров, как правило, рассматривается отдельно. В данном разделе методы адресации, связанные со счетчиком команд (адресация относительно счетчика команд) рассматриваются отдельно. Этот вид адресации используется главным образом для определения программных адресов в командах передачи управления.

На рисунке на примере команды сложения (Add) приведены наиболее употребительные названия методов адресации, хотя при описании архитектуры в документации разные производители используют разные названия для этих методов. На этом рисунке знак "(" используется для обозначения оператора присваивания, а буква М обозначает память (Memory). Таким образом, M[R1] обозначает содержимое ячейки памяти, адрес которой определяется содержимым регистра R1.

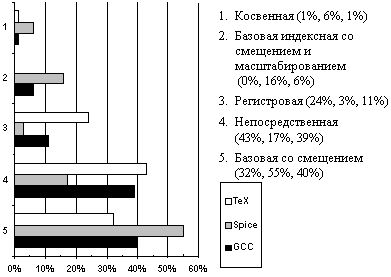

Использование сложных методов адресации позволяет существенно сократить количество команд в программе, но при этом значительно увеличивается сложность аппаратуры. Возникает вопрос, а как часто эти методы адресации используются в реальных программах? На рис. 4 представлены результаты измерений частоты использования различных методов адресации на примере трех популярных программ (компилятора с языка Си GCC, текстового редактора TeX и САПР Spice), выполненных на компьютере VAX.

Метод адресации |

Пример команды |

Смысл команды методаИспользование |

1 |

2 |

3 |

Регистровая |

Add R4,R3 |

R4(R4+R5Требуемое значение в регистре |

Непосредственная или литеральная |

Add R4,#3 |

R4(R4+3 Для задания констант |

Базовая со смещением |

Add R4,100(R1) |

R4(R4+M[100+R1]Для обращения к локальным переменным |

Косвенная регистровая |

Add R4,(R1) |

R4(R4+M[R1]Для обращения по указателю или вычисленному адресу |

Индексная |

Add R3,(R1+R2) |

R3(R3+M[R1+R2]Иногда полезна при работе с массивами: R1 - база, R3 - индекс |

Прямая или абсолютная |

Add R1,(1000) |

R1(R1+M[1000]Иногда полезна для обращения к статическим данным |

1 |

2 |

3 |

Косвенная |

Add R1,@(R3) |

R1(R1+M[M[R3]]Если R3-адрес указателя p, то выбирается значение по этому указателю |

Автоинкрементная |

Add R1,(R2)+ |

R1(R1+M[R2] R2(R2+dПолезна для прохода в цикле по массиву с шагом: R2 - начало массива В каждом цикле R2 получает приращение d |

Автодекрементная |

Add R1,(R2)- |

R2(R2-d R1(R1+M[R2]Аналогична предыдущей Обе могут использоваться для реализации стека |

Базовая индексная со смещением и масштабированием |

Add R1,100(R2)[R3] |

R1( R1+M[100]+R2+R3*dДля индексации массивов |

Рис. 3. Методы адресации

Рис. 4. Частота использования различных методов адресации на программах TeX, Spice, GCC

Из этого рисунка видно, что непосредственная адресация и базовая со смещением доминируют.

При этом основной вопрос, который возникает для метода базовой адресации со смещением, связан с длиной (разрядностью) смещения. Выбор длины смещения в конечном счете определяет длину команды. Результаты измерений показали, что в подавляющем большинстве случаев длина смещения не превышает 16 разрядов.

Этот же вопрос важен и для непосредственной адресации. Непосредственная адресация используется при выполнении арифметических операций, операций сравнения, а также для загрузки констант в регистры. Результаты анализа статистики показывают, что в подавляющем числе случаев 16 разрядов оказывается вполне достаточно (хотя для вычисления адресов намного реже используются и более длинные константы).

Важным вопросом построения любой системы команд является оптимальное кодирование команд. Оно определяется количеством регистров и применяемых методов адресации, а также сложностью аппаратуры, необходимой для декодирования. Именно поэтому в современных RISC-архитектурах используются достаточно простые методы адресации, позволяющие резко упростить декодирование команд. Более сложные и редко встречающиеся в реальных программах методы адресации реализуются с помощью дополнительных команд, что вообще говоря приводит к увеличению размера программного кода. Однако такое увеличение длины программы с лихвой окупается возможностью простого увеличения тактовой частоты RISC-процессоров. Этот процесс мы можем наблюдать сегодня, когда максимальные тактовые частоты практически всех RISC-процессоров (Alpha, R4400, Hyper SPARC и Power2) превышают тактовую частоту, достигнутую процессором Pentium.