Шпаргалки по МПС / MPS_shprots / Вопрос 17 (первые 2 страницы)

.pdf

1-1

1.ОБЗОР АРХИТЕКТУРЫ

1.1.ВВЕДЕНИЕ

Микроконтроллеры семейства MCS-96 - микроконтроллеры высокой интеграции с 16-битным центральным процессорным устройством (CPU) и, как минимум, с 230 - байтной внутренней оперативной памятью (RAM). Семейство MCS-96 легко управляет высокоскоростными процессами и быстродействующими устройствами ввода-вывода. Типичное применение МСS-96: замкнутые системы управления и цифровая обработка сигналов среднего уровня. Модемы, системы управления двигателями, принтеры, фотокопировальная техника, тормозные системы, системы управления кондиционерами, дисководы и медицинская аппаратура - все это области применения MCS-96.

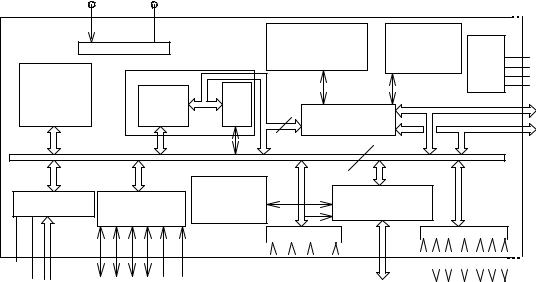

Все компоненты MCS-96 имеют общую систему команд и архитектуру. Однако CHMOS-компоненты способны обеспечить более высокую интеграцию при меньшей потребляемой мощности. Они имеют специализированные подсистемы ввода-вывода и 16битные арифметические операции, включая умножение и деление. В этом обзоре кратко описывается система команд MCS-96, архитектура и основные особенности 8X9XX и 80C196ХХ. На рисунке 1.1 приведена блок-схема микроконтроллеров семейства MCS-96.

XTAL1 |

XTAL2 |

|

|

|

|

|

|

|

Internal RAM |

On-chip |

|

|

|

Clock Generator |

ROM / |

|

|

|||

KR, KT, NQ, NT |

POWER |

Vcc |

||||

|

|

(optional) |

AND |

|||

|

|

|

|

Vss |

||

|

|

|

|

|

|

|

PERIPHERAL |

CPU |

|

|

|

GND |

Vss |

|

|

|

|

|

Vss |

|

TRANSACTION |

Register |

|

|

|

|

|

|

|

|

|

CONTROL |

||

SERVER |

File |

RALU |

|

|

|

|

Memory Controller |

|

|

SIGNALS |

|||

(PTS) |

16 |

|

|

|||

|

|

|

||||

|

|

|

|

|

||

|

|

|

w/Prefetch Queue |

|

|

ADDR/ |

|

|

|

16 |

|

|

DATA |

|

|

|

|

|

|

BUS |

|

|

Programmable |

EVENT PROCESSOR |

|

A/D Converter |

Serial I/O |

Interrupt |

||

ARRAY èëè HSIO |

||||

(10 bit) |

(UART & SSIO) |

Controller |

||

|

|

|||

|

|

TIMER 1 & 2 |

I/O PORTS |

Vref |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

SC0 SC1 SD0 SD1TXD RXD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T1CLK T2CLK |

|

EPA0-3 |

P0 |

P1P2 P3 P4 P5 P6 |

||||||||||||||

ANGND |

|

|

|

|

|

|

||||||||||||||

|

|

T1DIR T2DIR èëè HSIO |

||||||||||||||||||

|

|

SC0, SC1, SD0, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

PORT5 & PORT6 имеет только KR

SD1 имеет только KR

Рисунок 1.1. Блок-схема микроконтроллеров семейства MCS-196.

1.2.ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР (CPU)

Основные компоненты CPU MCS-96 - Регистровый Файл (Register File) и Регистровое Арифметико-Логическое Устройство (Register/Arithmetic Logic Unit - RALU).Регистровый файлэто адресуемое пространство регистров процессора. Ячейки от 00h до 17h - это управляющие регистры ввода-вывода или регистры cпециальных функций (Special Function Registers - SFR). Ячейки 18h и 19h содержат указатель стека, они могут использоваться как обычная RAM-память, когда не выполняются стековые операции. Остальные байты регистрового файла служат как обычная RAM-память, доступная как байт, слово или как двойное слово.

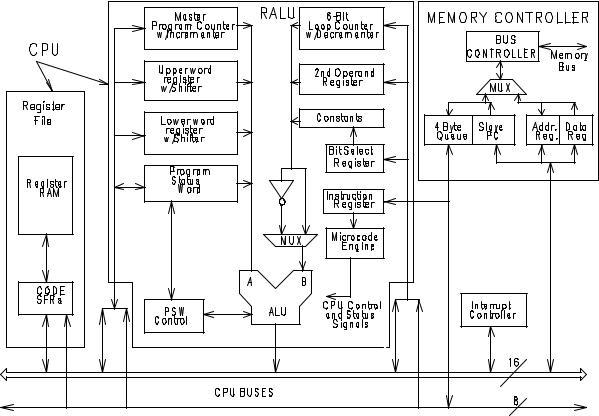

CPU выполняет вычисления в RALU. RALU, изображенное на рисунке1.2, содержит 17-битное арифметико-логическое устройство (ALU), слово состояния программы (PSW),

1-2

счетчик команд (PC), счетчик циклов и три временных регистра. RALU работает напрямую с регистровым файлом, таким образом устраняются пересылки через аккумулятор и обеспечивается прямое управление операциями ввода/вывода через SFR.

Рисунок 1.2. Блок-схема ядра семейства MCS-96 (CPU, RALU, |

контроллеры памяти и прерываний ). |

1.3.АРХИТЕКТУРА

MCS-96 содержит полный набор команд, включающий операции с битами, байтами, словами, двойными словами (беззнаковые 32 бит), длинные операции (32 бит со знаком), работу с флагами, а также переходы и вызовы подпрограмм. Все стандартные логические и арифметические команды работают как с байтами, так и со словами. Команды перехода по установке бита (Jump Bit Set) и очистке бита (Jump Bit Clear) могут работать с какимлибо регистром SFR или с другими байтами регистрового файла. Эти быстрые битовые операции позволяют ускорить функции ввода/вывода.

Операции над байтами и словами составляют основу системы команд. Ассемблер ASM-96 использует суффикс "В" в мнемонике для операций над байтами, иначе мнемоника относится к операциям над словами.

Длинные и двухсловные операции включают операции сдвигов, нормализацию, умножение и деление. В операции “Деление” делится 32-битное число на 16-битное число, что порождает 16-битное частное и 16-битный остаток. В операции “Умножение” умножается 16-битное на 16-битное число с образованием 32-битного результата. Обе операции могут выполняться с числами со знаком или без знака. Команды нормализации и соответствующий флаг обеспечивает аппаратную поддержку пакета программ для выполнения операций над числами с плавающей запятой (FPAL-96).

1-3

1.3.1.Способы Адресации

Система команд MCS-96 содержит следующие типы адресации: прямая регистровая (register - direct), косвенная (indirect), косвенная с автоувеличением (indirect with autoincrement) непосредственная (immediate), короткая индексная (short-indexed ) и длинная индексная (long-indexed). Эти типы адресации увеличивают гибкость и скорость выполнения команд устройствами MCS-96. Каждая команда использует по крайней мере один из способов адресации. Эти способы и их форматы представлены на рисунке 1.3.

Прямая регистровая адресация и непосредственная адресация выполняются наиболее быстро. Прямая регистровая адресация обеспечивает доступ к файлу регистров и SFR. Непосредственная адресация использует информацию, следующую за кодом команды, как операнд.

Оба режима косвенной адресации используют значение слова в регистре как адрес операнда. Косвенная адресация с автоинкрементом увеличивает адресное слово на единицу после операции с байтом, и на два после операции со словом. Этот способ адресации обеспечивает легкий доступ к справочным таблицам.

Длинная индексная адресация обеспечивает прямой доступ к любой ячейке 64К адресного пространства. Этот способ формирует адрес операнда добавлением 16-битного значения к регистровому слову. Индексирование с нулевым регистром позволяет иметь прямую адресацию к любой ячейке. Короткая индексная адресация формирует адрес операнда добавлением 8-битного значения к регистровому слову.

8XC196NT(NQ), 8XC196NP содержат 9 новых команд, выполняемых для поддержки адресации в расширенном адресном пространстве размером 1 Mбайт. Четыре команды расширенной загрузки и хранения, использующие косвенную адресацию, косвенную адресацию с автоинкрементом и расширенную индексную адресацию, могут быть использованы для адресации 1M адресного пространства. Имеются три команды для расширенного вызова подпрограммы, перехода по условию и передачи управления.

Кроме того имеются расширенные версии команд прерываемой и непрерываемой передачи блока. Множество способов адресации семейства MCS-96 делает легким программирование на языке ассемблера и обеспечивает отличную взаимосвязь с языками высокого уровня. Команды ассемблера, состоят из мнемоники, за которой следуют адрес или данные. Система команд для 8XC196KC/KD приведена в Приложении B.

1.4.ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 8Х9Х

Стандартные порты ввода/вывода (I/O). 8Х9Х имеют пять 8-битных I/O портов. Порт 0 - входной порт, а также порт аналоговых входов для A/D - преобразователя. Порт 1 - квазидвунаправленный. Порт 2 содержит три типа линий: квазидвунаправленные, входные и выходные. Большинство выводов Порта 2 8Х9Х используется для выполнения альтернативных функций. Порты 3 и 4 являются двунаправленными портами с открытым стоком, подключенными к шине адрес/данные.

Таймеры. 8Х9Х имеют два 16-битных таймера - Таймер 1 и Таймер 2. Внутренняя синхронизация увеличивает значение Таймера 1 и Таймера 2 каждый восьмой такт процессора, равный трем периодам тактовой частоты.Таймер 2 может иметь внешнюю синхронизацию. При внешей синхронизации значение Таймера 2 увеличивается при каждом положительном или отрицательном перепаде. Любой внешний или внутренний источник может сбросить Таймер 2. Таймер 1 и Таймер 2 могут сформировать прерывание при переходе границы 0FFFFh/0000h. 8Х9Х также позволяет использовать таймеры для задания скорости передачи информации последовательным портом и для управления работой сторожевого таймера (Watchdog timer). Это внутренний таймер для сброса системы в случае, если программное обеспечение не может нормально функционировать.

1-4

Устройства высокоскоростного ввода (HSI). HSI 8Х9Х могут записывать время внешних событий с разрешающей способностью в 9 тактов процессора. Они могут следить за четырьмя независимыми линиями HSI и фиксировать значение Таймера 1, когда происходят события. Четыре типа событий могут инициализировать захват: нарастающий фронт, спад сигнала, оба фронта или каждый восьмой нарастающий фронт. Устройства HSI могут сохранять до 8 значений Таймера 1. Чтение регистра хранения HSI не стирает ранее загруженные значения, расположенные в FIFO. Устройство HSI может сформировать прерывание, когда фиксируется событие в HSI-регистре хранения или происходит шестая запись в буфер FIFO.

Устройства высокоскоростного вывода (HSO) могут инициализировать события в определенные моменты, базирующиеся на показаниях Таймера 1 или Таймера 2. Эти программируемые события заключаются в запуске A/D-преобразователя, сбросе Таймера 2, формировании до четырех программных временных задержек и в установке или очистке одной из шести выходных линий HSO. HSO хранит ожидаемые события и соответствующее время в файле памяти Content Addressable Memory (CAM). Этот файл хранит до восьми команд. Каждая команда определяет время действия, "природу" действия, имеет ли место прерывание, идет ли ссылка на Таймер 1 или Таймер 2. Каждый 8 тактHSO сравнивает значение в ячейке CAM-файла со значением времени. HSOустройство инициализирует определенные события при совпадении значений. Команда стирается из CAM-файла после выполнения или может быть зафиксирована для постоянного выполнения.

Последовательный порт. Последовательный порт имеет один синхронный режим (Mode0) и три асинхронных (1, 2 и 3). Асинхронные режимы полностью дуплексные, т.е. они могут передавать и принимать данные одновременно. Приемник 8Х9Х имеет буфер данных, что позволяет вести прием второго байта до считывания первого. Наиболее общее использование синхронного Режима0 - расширение возможностей устройств ввода-вывода ( I/O) у 8Х9Х, использующих сдвиговые регистры. Режим 1 - стандартный асинхронный режим, используемый для нормальных последовательных коммуникаций. Данные для обмена в режиме 1 содержат 10 бит: стартовый бит, 8 бит данных (младший значащий бит (LSB) - первый) и стоповый бит. Eсли передача бита четности разрешена (PEN=1), бит дополнения до четности посылается вместо восьмого бита данных. Режимы 2 и 3 - девятибитные режимы общего пользования. Данные для обмена, используемые в этих режимах, содержат 11 бит: стартовый бит, девять информационных (LSB первый) и стоповый бит. Устройства, работающие в режиме 2, будут вырабатывать прерывание при приеме только тогда, когда девятый информационный бит будет установлен. Устройства, работающие в режиме 3, всегда будут вырабатывать прерывание при приеме. Режим 3 позволяет передавать 8 информационных бит плюс бит дополнения до четности.

Широтно-импульсный модулятор (PWM). Cкважность импульса на выходе PWM является переменной величиной, импульсы повторяются каждые 256 тактов. PWM 8Х9Х может использоваться в различных применениях. Используя выход PWM, можно выполнять цифро-аналоговoe преобразование и управлять различными типами двигателей, которые требуют PWM для более эффективной работы.

A/D-преобразователь - преобразует аналоговый входной сигнал в 10-битный цифровой код. Основные компоненты преобразователя: 8 аналоговых входов, мультиплексор 8 к одному, фиксирующий и хранящий конденсатор и резисторная матрица. Преобразователь может начать преобразование немедленно, или HSO может запустить преобразование в заранее запрограммированное время. Преобразователь выполняет преобразование за 88 тактов. По завершении каждого преобразования может вырабатываться прерывание A/D Conversion Complete. 8Х9Х имеет отдельные выводы питания Vref и ANGND для изоляции от помех на Vccили Vssлиниях.

Прерывания. В 8Х9Х имеется 21 источник прерываний и 8 векторов прерываний. Когда контроллер прерываний обнаруживает одно из восьми прерываний, он устанавливает соответствующий бит в регистре ожидания прерывания. Индивидуальные прерывания разрешаются или запрещаются установкой или очисткой бита в регистре маски прерываний. Когда контроллер прерывания решает произвести прерывание, он делает вызов программы обслуживания прерываний (ISR). Соответствующий вектор прерывания

1-5

содержит адрес ISR. Затем контроллер прерывания очищает соответствующий бит ожидания прерывания.

1.5.ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 8ХС196КВ

Стандартные I/O порты. 8ХС196КВ имеет пять 8-битных I/O портов. Порт 0 - входной, он же порт аналоговых входов для A/D-преобразователя. Порт 1 - квазидвунаправленный. Порт 2 содержит три типа выводов - квазидвунаправленные, входные и выходные. Большинство выводов Порта 2 8Х9Х используется для выполнения альтернативных функций. Порты 3 и 4 являются двунаправленными портами с открытым стоком, они могут использоваться как шина адрес/данные.

Таймеры. 8ХС196КВ имеет два 16-битных таймера: Таймер1 и Таймер2. При внутренней синхронизации значение Таймера1 увеличивается каждые 8 тактов процессора (такт - два периода тактового генератора ). При внешней синхронизации значение Таймера2 наращивается или уменьшается при каждом положительном или отрицательном перепаде. Любой внутренний или внешний источник может сбросить Таймер2. Таймер1 может сформировать прерывание при переходе границы 0FFFFh/0000h. Таймер2 может сформировать прерывание при переходе границ 0FFFFh/0000h или 7FFFh/8000h. 8ХС196КВ также использует таймеры для задания скорости передачи информации и временного контроля WDT (watchdog timer). WDT - это отдельный внутренний таймер для сброса системы в случае, если программное обеспечение не сможет нормально функционировать.

Устройство высокоскоростного ввода (HSI). HSI 8ХС196КВ может записывать

время внешних событий с разрешающей способностью в 9 тактов. HSI может следить за четырьмя независимыми линиями HSI и определять значение Таймера1, когда происходят события. Четыре типа событий могут инициализировать захват: нарастающий фронт, спад сигнала, нарастание и спад или каждый восьмой нарастающий фронт. HSI может хранить 8 элементов (значения Таймера1), 7 в 7-уровневой очереди FIFO и 1 в регистре хранения

HSI. Чтение регистра хранения HSI не |

перегружает значения, размещенные в FIFO |

ранее. Устройства HSI могут сформировать прерывание при загрузке регистра хранения |

|

HSI, или когда загружаемое значение |

является четвертым или шестым элементом FIFO. |

Высокоскоростное устройство вывода (HSO). HSO 8ХС196КВ может инициализировать события в определенные моменты, базирующиеся на показаниях Таймера1 или Таймера2. Эти программируемые события заключаются в запуске A/D- преобразования, сбросе Таймера2, формировании до четырех программных временных задержек и установке или очистке одной или нескольких линий из шести выходных линий HSO. HSO хранит ожидаемые события и соответствующее время в файле памяти Content Addressable Memory (CAM). Этот файл хранит до восьми команд. Каждая команда определяет время действия, "природу" действия, имеет ли место прерывание, идет ссылка на Таймер1 или Таймер2. Каждый 8 такт HSO сравнивает значение ячеек CAM на совпадение с текущим временем. HSO инициализирует определенные события при совпадении времени. Команда стирается из CAM после выполнения или остается в CAM как запомненная точка входа CAM, тогда команда будет постоянно выполняться при совпадении значения времени для этой точки со значением текущего времени в соответствующем Таймере. Запомненнная точка входа полезна в применениях, требующих периодических или повторяющихся событий, таких как повторяющаяся ШИМ последоватнльность.

Последовательный порт имеет один синхронный режим (Mode0) и три асинхронных (1, 2 и 3). Асинхронные режимы полностью дуплексные, т.е. они могут передавать и принимать данные одновременно. Приемник на 196KB буферизован так, что прием второго байта может начаться до считывания первого. Передатчик также дважды буферизован. Наиболее общее использование синхронного Режима0 - расширение возможностей устройств ввода-вывода 8ХC196KB, использующих регистры сдвигов. Режим 1 - стандартный асинхронный режим, используемый для нормальных последовательных коммуникаций. Структура данных для режима 1 состоит из 10 бит: стартовый, 8 бит данных (LSB первый) и стоповый бит. Если передача бита четности разрешена (PEN=1), бит дополнения до четности посылается вместо восьмого бита данных.

1-6

Режимы 2 и 3 - девятибитные режимы общего пользования для межпроцессорных коммуникаций. Структура данных, используемых в этих режимах, состоит из 11 бит: стартовый, 9 бит данных (LSB первый) и стоповый бит. Устройства, работающие в режиме 2, будут вырабатывать прерывание при приеме только тогда, когда девятый информационный бит будет установлен. Устройства, работающие в режиме 3, всегда будут вырабатывать прерывание при приеме. Режим 3 позволяет передавать 8 информационных бит плюс бит дополнения до четности.

Широтно-импульсный модулятор (PWM) подготавливает полезные сигналы для множества применений. Используя выход PWM, можно выполнять цифро-аналоговое преобразование и управлять различными типами моторов, которые требуют для более эффективной работы PWM-формирователя импульсов. Скважность импульса на выходе формирователя является переменной, импульсы повторяются каждые 256 или 512 тактов.

A/D-преобразователь конвертирует аналоговый вход в 10-битный цифровой эквивалент. Основные компоненты A/D-преобразователя: 8 аналоговых входов, мультиплексор 8 к одному, фиксирующий и хранящий конденсатор и резисторная матрица. Преобразователь может начать конвертацию немедленно, или HSO может инициализировать преобразование в запрограммированное время. Преобразователь может выполнять конвертацию каждые 91 тактов для низкочастотных кристаллов и 158 - для высокочастотных кристаллов. При завершении каждого преобразования вырабатывается прерывание. 8ХC196KB имеет отдельные выводы питания Vref и ANGND, что исключает влияние помех по Vccили Vss-линиям на A/D преобразование.

Прерывания. Устройство имеет 28 источников прерывания и 16 векторов прерывания, а также 2 дополнительных вектора прерывания для Software Trap (Пошагового выполнения программ) и Unimplemented Opcodes (Неопознанных кодов операций). Когда контроллер прерывания определит одно из шестнадцати прерываний, он устанавливает соответствующий бит в один из двух регистров ожидания прерывания. Отдельные прерывания разрешаются либо запрещаются установкой или очисткой битов в регистре маски прерываний. Когда контроллер прерывания решает обработать прерывание, он делает вызов программы обслуживания прерываний (ISR). Соответствующий вектор прерывания содержит адрес ISR. Затем контроллер прерывания очищает соответствующий бит ожидания прерывания.

1.6.ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 8XC196KC И 8XC196KD

Стандартные I/O порты. 8ХС196КC/KD имеют пять 8-битных I/O портов. Порт 0 - входной, он же порт аналоговых входов для A/D-преобразователя. Порт 1 - квазидвунаправленный, он разделяет выводы с двумя выходами PWM. Порт 2 содержит три типа линий - квазидвунаправленные, входные и выходные. Другие функции 8ХС196КC/KD используют входные и выходные линии совместно с Портом 2. Порты 3 и 4 являются двунаправленными портами с открытым стоком, они могут использоваться как шина адрес/данные.

Таймеры. 8ХС196КС/KD имеет два 16-битных таймера: Таймер1 и Таймер2. При внутренней синхронизации значение Таймера1 увеличивается каждые 8 тактов процессора (такт - два периода тактового генератора ). При внутренней синхронизации Таймер2 может наращиваться на каждом 1 или 8 такте. При внешней синхронизации значение Таймера2 наращивается или уменьшается при каждом положительном или отрицательном перепаде. Любой внутренний или внешний источник может сбросить Таймер2. Таймер1 может сформировать прерывание при переходе границы 0FFFFh/0000h. Таймер2 может сформировать прерывание при переходе границ 0FFFFh/0000h или 7FFFh/8000h. 8ХС196КC/KD также позволяет использовать таймеры для задания скорости передачи информации и временного контроля WDT (watchdog timer). WDT - это отдельный внутренний таймер для сброса системы в случае, если программное обеспечение не сможет нормально функционировать.

Устройства высокоскоростного ввода (HSI). HSI 8ХС196КC/KD может записывать время внешних событий с разрешающей способностью в 9 тактов. HSI может следить за четырьмя независимыми линиями HSI и определять значение Таймера1, когда произойдет

1-7

событие. Четыре типа событий могут инициализировать захват: нарастающий фронт, спад

сигнала, нарастание и спад или каждый восьмой нарастающий фронт. HSI может хранить 8 элементов (значений Таймера1), 7 в 7-уровневой очереди FIFO и 1 в регистре хранения

HSI. Чтение регистра хранения HSI не |

перегружает значения, размещенные в FIFO |

ранее. Устройства HSI могут сформировать прерывание при загрузке регистра хранения |

|

HSI, или когда загружаемое значение |

является четвертым или шестым элементом FIFO. |

Высокоскоростное устройство вывода (HSO). HSO 8ХС196КC/KD может инициализировать события в определенные моменты, базирующиеся на значениях Таймера1 или Таймера2. Эти программируемые события заключаются в запуске A/D- преобразования, сбросе Таймера2, формировании до четырех программных временных задержек и установке или очистке одной или нескольких линий из шести выходных линий HSO. HSO хранит ожидаемые события и соответствующее время в файле памяти Content Addressable Memory (CAM). Этот файл хранит до восьми команд. Каждая команда определяет время действия, "природу" действия, имеет ли место прерывание, идет ссылка на Таймер1 или Таймер2. Каждый 8 такт HSO сравнивает значение ячеек CAM на совпадение с текущим временем. HSO инициализирует определенные события при совпадении времени. Команда стирается из CAM после выполнения или остается в CAM как запомненная точка входа CAM, тогда команда будет постоянно выполняться при совпадении значения времени для этой точки со значением текущего времени в соответствующем Таймере. Запомненнная точка входа полезна в применениях, требующих периодических или повторяющихся событий, таких как повторяющаяся ШИМ последоватнльность.

Последовательный порт имеет один синхронный режим (Mode0) и три асинхронных (1, 2 и 3). Асинхронные режимы полностью дуплексные, т.е. они могут передавать и принимать данные одновременно. Приемник на 196KС/KD буферизован так, что прием второго байта может начаться до считывания первого. Передатчик также дважды буферизован. Наиболее общее использование синхронного Режима0 - расширение возможностей устройств ввода-вывода 8ХC196KC/KD, использующих регистры сдвигов. Режим 1 - стандартный асинхронный режим, используемый для нормальных последовательных коммуникаций. Структура данных для режима 1 состоит из 10 бит: стартовый, 8 бит данных (LSB первый) и стоповый бит. Если передача бита четности разрешена (PEN=1), бит дополнения до четности посылается вместо восьмого бита данных. Режимы 2 и 3 - девятибитные режимы общего пользования для межпроцессорных коммуникаций. Структура данных, используемых в этих режимах, состоит из 11 бит: стартовый, 9 бит данных (LSB первый) и стоповый бит. Устройства, работающие в режиме 2, будут вырабатывать прерывание при приеме только тогда, когда девятый информационный бит будет установлен. Устройства, работающие в режиме 3, всегда будут вырабатывать прерывание при приеме. Режим 3 позволяет передавать 8 информационных бит плюс бит дополнения до четности.

Широтно-импульсный модулятор (PWM) устройства 8XC196KC/KD имеет три выхода PWM. Скважность импульса на выходе формирователя является переменной, импульсы повторяются каждые 256 или 512 тактов. Различные типы моторов требуют PWM - формирователя импульсов для наиболее эффективной работы. Кроме того, фильтрация этой ШИМ последовательности будет создавать постоянный уровень, который измененяется с изменением скважности.

A/D-преобразователь конвертирует аналоговый вход в цифровой эквивалент. Разрешающая способность 8 или 10 бит с программируемыми временами фиксации и преобразования. Основные компоненты A/D-преобразователя: фиксирующий и хранящий конденсатор, 8-ка-нальный мультиплексор и 8- или 10-битный аналогово/цифровой преобразователь поразрядного взвешивания. Преобразователь может начать преобразование немедленно, или HSO может инициализировать преобразование в запрограммированное время. При завершении каждой конверсии преобразователь вырабатывает прерывание. 8XC196KC/KD имеет отдельные выводы питания Vref и ANGND, что исключает влияние помех по Vccили Vss - линиям на A/D преобразование.

Прерывания. Здесь 28 источников прерывания и 16 векторов прерывания, а также 2 дополнительных вектора прерывания Software Trap (Пошаговое выполнение программ) и Unimplemented Opcodes (Неопознанные коды операций), используемых в

1-8

системах отладки фирмы Intel или платах-прототипах. Когда контроллер прерывания определит одно из шестнадцати прерываний, он устанавливает соответствующий бит в один из двух регистров ожидания прерываний. Отдельные прерывания разрешаются либо запрещаются установкой или очисткой бит в регистре маски прерываний. Когда контроллер прерывания производит обработку прерывания, он делает вызов программы обслуживания прерываний (ISR). Соответствующий вектор прерывания содержит адрес ISR. Затем контроллер прерывания очищает соответствующий бит ожидания.

Сервер периферийного обмена (PTS) - микропрограммный процессор аппаратной обработки прерывания. Он реагирует на прерывание фиксированной последовательностью действий. Эти действия состоят из передачи данных, запуска A/D-преобразования, чтения HSI FIFO и загрузки событий HSO. PTS выполняет эти задачи намного быстрее, чем это произойдет при использовании программ, обслуживающих прерывание. PTS может обслуживать все прерывания, исключая NMI, пошаговое прерывание и прерывания по неопознанным кодам операций. Каждое прерывание, управляемое PTS, требует блока данных, называемого управляющим блоком PTS (PTSCB). Kаждый PTSCB требует 8 байт данных в регистре RAM. PTSCB определяет: тип PTS, номер отклика PTS (если необходимо), источник для данных и приемник (если необходимо). Циклы PTS имеют более высокий приоритет, нежели прерывания и могут временно приостанавливать программы обслуживания прерываний.

1.7.ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 8XC196KХ

Âсостав семейства 8ХС196КХ входят микроконтроллеры 8Х196КТ(KS), 8X196KR(KQ), 8ХJR(JQ), 8X196CA. Основные характеристики членов этого семейства приведены в таблице 1.1. Периферийные устройства микроконтроллеров 8Х196КТ(KS), 8X196KR(KQ), 8X196JR(JQ) отличаются только количеством выводов в портах I/O, числом входов A/D преобразователя и каналов устройства обработки событий ЕРА. 8Х196СА поддерживет интерфейс CAN спецификация 2.0, но не имеет порта межпроцессорной связи (slave port).

Стандартные I/O порты. 8XC196KR/KT имеют шесть 8- битных I/O портов. Каждый вывод может быть назначен на ввод или вывод. Большинство выводов имеют также альтернатив-ные функции. В KR/KT не использован вывод квазидвунаправленных портов, имеющиеся в предыдущих приборах MCS-96. Если вывод работает как вход, он имеет высокое сопротивление. Большинство портов (Порты 1, 2, 5 и 6) имеют регистры направления (Px_DIR), регистры режима (Px_MODE), регистры ввода данных (Px_PIN), регистры вывода данных (Px_REG). Это позволяет пользователю формировать каждый вывод порта как вход, выход, выход с открытым стоком или альтернативную функцию. Порты 3 и 4 имеют регистры Px_PIN и Px_REG. Как стандартные выходы, эти выводы могут функционировать только в режиме открытого стока и нуждаются во внешней нагрузке. Порты 3 и 4 также могут использоваться как мультиплексированная шина адрес/данные. При формировании адреса внутренняя нагрузка активна и нет необходимости во внешних резисторах. Порт 0 в аналоговом режиме имеет только Px_PINрегистр, так как отсутствуют драйверы выхода. Как цифровой порт, Порт 0 может функционировать только на ввод.

Устройство обработки событий (EPA) - выполняет захват событий и вывод событий, сформированных функциями, использующими Таймер1 и Таймер2. Он состоит из 10 модулей захват/сравнение, двух модулей только сравнения и двух таймеров. В режиме захвата, при появлении внешнего события, EPA сохраняет значение таймера, вырабатывает прерывание или выполняет и то и другое. Нарастающий, спадающий фронт или любой из них может инициировать захват.Все захваты дважды буферизованы. В режиме сравнения, когда значение таймера сравнится со значением в регистре сравнения, EPA изменяет состояние выходного вывода, формирует прерывание, или делает и то и другое. EPA устанавливает, сбрасывает или переключает вывод, когда происходит сравнение. Таймер может вести прямой или обратный счет времени. Источники синхронизации таймеров могут быть внутренними или внешними. При счете времени также используется предделитель. Предделитель делит частоту колебаний в пределах отношения 1 к 64. EPA также

1-9

позволяет двум каналам управлять одним выходом, что полезно для высокоскоростной PWM-генерации.

Последовательный I/O порт (SIO) - (также известный как UART) поддерживает 8- или 9-битную структуру данных в одном синхронном режиме и трех асинхронных. Синхронный режим передает или принимает 8 бит данных без стартового и стопового бита и генерирует импульсы сдвига. Все остальные устройства должны синхронизироваться с этим импульсом сдвига. Асинхронная посылка содержит стартовый и стоповый биты и может быть длиной в 10 или 11 бит. 11-битная структура позволяет реализовать специализированный межпроцессорный коммуникационный интерфейс. Два из асинхронных режимов поддерживают обнаружение ошибки четности. Все три асинхронных режима поддерживают полный дуплекс или полудуплекс. SIO содержит генератор скорости передачи информации. SIO 8XC196KR/KT совместимы со всеми последовательными портами семейств MCS-96 и MCS-51.

Синхронный последовательный I/O порт (SSIO) - включает в себя два последовательных I/O коммуникационных порта с раздельными выводами данных и синхронизации. Формат данных - только 8 информационных бит. Выводы синхронизации и данных могут быть входами или выходами. SSIO поддерживает различные стандарты синхронных последовательных протоколов. Режим установления и синхронизации связи (handshake) позволяет двум последовательным каналам передавать данные без требования дополнительных линий для передачи статуса канала. Этот режим также позволяет обслуживать SSIO средствами PTS. Последовательный канал включает в себя генератор скорости передачи информации. Каждый канал имеет единственный буфер байта. При внешней синхронизации оба канала могут работать на различных частотах. Максимальная скорость передачи информации - 1/8 частоты осциллятора. Передача или прием байта устанавливают флаг ожидания прерывания.

A/D-преобразователь конвертирует аналоговый вход в цифровой эквивалент. Разрешающая способность: 8 или 10 бит с программируемым временем фиксации и преобразования.Основные компоненты A/D-преобразователя: 8 аналоговых входов, мультиплексор 8 к одному, фиксирующий и хранящий конденсатор и резисторная матрица. Другая функция, реализованная A/D-преобразователем - обнаружение порогового значения. Преобразователь вырабатывает прерывание, когда аналоговый вход больше или меньше, чем запрограммированное цифровое значение. 8XC196KХ имеет отдельные выводы питания Vref и ANGND, что исключает влияние помех по Vccили Vss - линиям на A/D преобразование.

Прерывания. В 8XC196KR/KT 37 источников прерывания и 18 векторов прерывания. Так как источников прерывания больше, нежели векторов, KR/KT реализуют косвенные прерывания. 17 прерываний - прямые; это значит, что каждое прерывание имеет один источник и адрес вектора прерывания. Остальные 20 источников прерывания - косвенные (indirect). Используется термин "косвенный", потому что несколько источников совместно используют один вектор прерывания и регистр, определяющий источник прерывания. Регистр EPAIPV содержит текущее прерывание самого высокого приоритета. EPAIPV читается для определения прерывания, требующего обслуживания. TIJMPкоманда с EPAIPV упрощает обслуживание косвенных прерываний. В прямые прерывания входят: NMI, пошаговое прерывание, внешнее прерывание, прерывание по неопознанному коду операций, прерывания SIO, SSIO, Slave-порта, A/D-преобразователя и четырех нижних каналов EPA. Косвенными прерываниями являются: верхние 6 каналов EPA, 2 канала сравнения, все 10 выходов за пределы в EPA и оба переполнения таймера.

Сервер периферийного обмена (PTS) - микропрограммный процессор аппаратной обработки прерывания. Он реагирует на прерывание фиксированной последовательностью действий. Эти действия состоят из передачи данных, запуска A/D-преобразования, генерации PWM - последовательностей. PTS выполняет эти задачи намного быстрее, чем это произойдет при использовании программ, обслуживающих прерывание. PTS может обслуживать все прерывания, исключая NMI, пошаговое прерывание и прерывание по неопознанным кодам операций. Регистр PTSSEL выбирает прерывания, обрабатываемые PTS. Каждое прерывание, управляемое PTS, требует блока данных, называемого управляющим блоком PTS (PTSCB). Kаждый PTSCB требует 8 байт данных в регистре RAM. PTSCB определяет: тип PTS, номер отклика PTS (если необходимо), источник для

1-10

данных и приемник (если необходимо). Циклы PTS имеют более высокий приоритет, нежели обычные прерывания, и могут временно приостанавливать программы обслуживания прерываний.

Slave-ïîðò - это интерфейс связи между KR/KT и другим микропроцессором. KR/KT находится на шине адрес/данные микропроцессора и доступен как периферийное устройство, адресуемое как память (Memory Mapped). Slave-порт включает в себя: вход выбора кристалла, 8-битную двунаправленную шину данных, линию ввода адреса, вход ALE (для фиксации адреса), WR# и RD# - входы для I/O данных и выход прерывания. Адресная линия и RD# илиWR# определяют доступность регистров на вывод данных, вывод состояния, ввод данных или ввод команды. Различные управляющие сигналы и структура порта позволяют KR/KT и другому процессору связываться друг с другом без необходимости быть синхронизированными.

1.8.ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 8XC196NХ

Âсостав семейства 8ХС196NХ входят микроконтроллеры 8Х196NТ(NQ), 8X196NP. Основные характеристики членов этого семейства приведены в таблице 1.1.

Расширенный адресный порт (EPORT). 80C196NX - представители семейства MCS96, имеющие адресацию, превышающую 64 Кбайта. 80C196NХ имеют 1М прямоадресуемого пространства, реализованного четырьмя адресными линиями, добавленными в EPORT.

Линии EPORT назначаются индивидуально на работу в качестве адреса или ввода/вывода (I/O). При назначении I/O они функционируют как стандартный I/O порт. Как вход, вывод имеет высокий импеданс без "подтягивания" к единице или нулю. Как выход, вывод является выводом с третьим состоянием или с открытым стоком. При назначении адресом выходы EPORT адресуют А16-А19. Адрес точно соответствует полному циклу шины, нужда в фиксации адреса устраняется.

Стандартные I/O порты. 8XC196NT(NQ) имеет семь 8-битных I/O портов. Каждый вывод предназначен для входа или выхода. Большинство выводов имеют также альтернативные функции. NT(NQ) не использует квазидвунаправленный порт выводов, имеющийся в предыдущих приборах MCS-96. Как вход, вывод имеет высокое активное сопротивление. Большинство портов (Порты 1, 2, 5 и 6) имеют регистры направления (Px_DIR), регистры режима (Px_MODE), регистры ввода данных (Px_PIN), регистры вывода данных (Px_REG). Это позволяет пользователю задавать каждый вывод порта как вход, выход, выход с открытым стоком или альтернативную функцию. Порты 3 и 4 имеют регистры Px_PIN и Px_REG. Как стандартные выходы, эти выводы могут функционировать только в режиме открытого стока и нуждаются во внешней нагрузке. Порты 3 и 4 также мультиплексированная шина адрес/данные. При формировании адреса внутренняя нагрузка прибора активна и нет необходимости во внешних резисторах. Порт 0 как аналоговый входной порт имеет только Px_PIN-регистр, так как отсутствуют драйверы выхода. Как цифровой Порт 0 может функционировать только как входной порт. 8X196NP имеет пять I/O портов (PORT1 - 4,EPORT). PORT1 - 4 являются стандартными двунаправленными портами.

Устройство обработки событий (EPA) - выполняет захват событий и вывод событий, сформированных функциями, использующими Таймер1 и Таймер2. Он состоит из 10 модулей захват/сравнение, двух модулей только сравнения и двух таймеров. В режиме захвата, при появлении внешнего события, EPA сохраняет значение таймера, вырабатывает прерывание или выполняет и то и другое. Нарастающий, спадающий фронт или любой из них может инициировать захват. Все захваты дважды буферизованы. В режиме сравнения, когда значение таймера совпадет со значением в регистре сравнения, EPA изменяет состояние выходного вывода, формирует прерывание или делает и то и другое. EPA устанавливает, сбрасывает или переключает вывод, когда происходит совпадение. Таймер может вести прямой или обратный счет времени. Источники синхронизации таймеров могут быть внутренними или внешними. При счете времени также используется предделитель. Предделитель делит частоту колебаний в пределах отношения 1 к 64. EPA также позволяет двум каналам управлять одним выходом, что полезно для высокоскоростной PWM-генерации.