Шпаргалки по МПС / MPS_shprots / Вопрос 27

.DOC

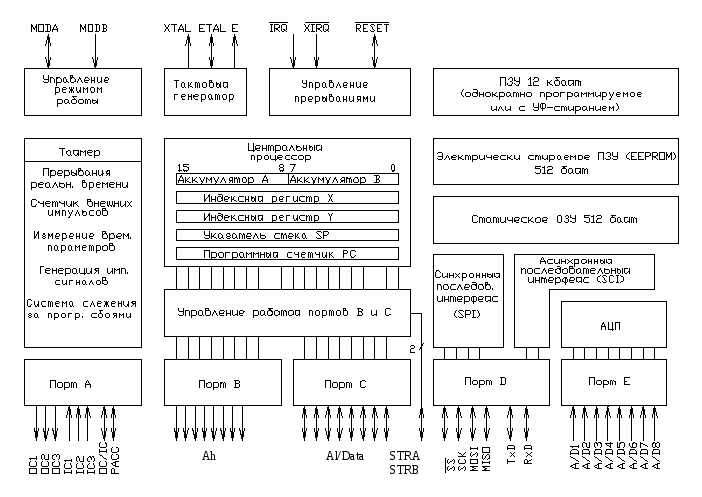

Архитектура MC68HC11E

Основные характеристики:

Cистема команд является надмножеством системы команд микропроцессоров M6800/M6801

8-разрядное процессорное ядро

6 методов адресации

ПЗУ - 0К, 4К - 48К

ПЗУ с электрическим стиранием 0, 0.5К, 2К

ОЗУ - 0, 192 - 1024 байт

Возможность обращения к внешней памяти с адресным пространством до 64К.

Таймер с 3-4 каналами IC и 4-5 каналами OC (Input Capture, Output Compare) - всего 8 каналов

COP Watchdog (Computer Operate Properly) таймер

SPI - Serial Peripheral Interface - синхронный последовательный канал связи

SCI - Serial Communication Interface - асинхронный последовательный канал связи

АЦП - до 8 каналов, 8 бит, 10 бит

ШИМ - (PWM - Pulse Width Modulation) управление громкостью звука, яркостью изображения, управление электродвигателями

Математический сопроцессор

Котроллер жидкокристаллического индикатора

21 источник прерывания

СТРУКТУРА MC68HC11E9

Режимы:

Микроконтроллер может работать в четырех режимах: однокристальный, расширенный, режим загрузки и тестовый режим. Выбор режима осуществляется во время системного сброса по состоянию входов MODB, MODA. Текущий режим работы определяется содержимым регистра HPRIO, структура которого показана ниже (этот регистр определяет также прерывание с наивысшим приоритетом).

|

|

MODB |

MODA |

Выбираемый режим |

|

|

1 |

0 |

Однокристальный режим |

|

|

1 |

1 |

Расширенный режим |

|

|

0 |

0 |

Режим загрузки |

|

|

0 |

1 |

Режим теста – используется изготовителем |

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$103C |

RBOOT |

SMOD |

MDA |

IRV |

PSEL3 |

PSEL2 |

PSEL1 |

PSEL0 |

HPRIO |

|

RESET |

- |

- |

- |

- |

0 |

1 |

0 |

1 |

|

Назначение отдельных битов регистра следующее:

- RBOOT - при установке в 1 разрешает чтение ROM загрузчика, иначе обращения по адресам программы загрузчика интерпретируются как обращения к внешней памяти. Этот бит имеет значение только в специальных режимах загрузки или теста, в остальных режимах бит RBOOT сброшен и не может быть изменен программно.

- SMOD - указывает на выбор одного из специальных режимов. Этот бит устанавливается, если во время сброса на входе MODB задан низкий уровень, в противном случае сбрасывается. Бит SMOD при работе в специальных режимах может быть сброшен программно, что позволяет изменить текущий режим работы. Программная установка бита SMOD невозможна.

- MDA - отображает состояние входа MODA во время сброса. В специальных режимах этот бит может быть изменен программно, позволяя изменить текущий режим работы, в нормальных режимах бит MDA доступен только для чтения.

- IRV - разрешает отображение процессов чтения из внутренней памяти на внешней шине данных (IRV=1). В специальных режимах этот бит может быть изменен в любой момент, в нормальных режимах - только один раз после сброса.

- PSEL3, PSEL2, PSEL1 и PSEL0 - задают маскируемое прерывание с наивысшим приоритетом.

Обращения к внутренним ROM (EPROM) и EEPROM можно запретить посредством регистра CONFIG.

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$103F |

0 |

0 |

0 |

0 |

NOSEC |

NOCOP |

ROMON |

EEON |

CONFIG |

При нулевом бите EEON запрещены обращения к EEPROM, при нулевом бите ROMON запрещены обращения к ROM (в однокристальном режиме ROM доступна независимо от значения ROMON). Кроме того, данный регистр позволяет отключать Watchdog-таймер (установкой NOCOP=1) и режим обеспечения безопасности (установкой NOSEC=1).

Четыре старших бита А15-12 начала адресов RAM и регистров задаются в регистре INIT

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$103D |

RAM3 |

RAM2 |

RAM1 |

RAM0 |

REG3 |

REG2 |

REG1 |

REG0 |

INIT |

|

RESET |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

Регистры

|

|

15 8 |

7 0 |

|

|

||||||||

|

B |

|

|

A - 8-разрядный |

|

||||||||

|

|

|

или D 16-разрядный Аккумулятор |

|

|||||||||

|

|

|

X - Индексный регистр |

|

|||||||||

|

|

|

Y - Индексный регистр |

|

|||||||||

|

|

|

SP растет вниз, на свободную ячейку |

|

|||||||||

|

|

$FFFE по Reset |

PC |

|

|||||||||

|

|

|

S |

X |

H |

I |

N |

Z |

V |

C |

CCR |

||

Способы адресации:

1. Подразумеваемая (INH):

OP

|

|

7 0 |

|

|

|

OP |

Операнд(ы) (A, B, X, Y) кодируется в OP |

TBA; (A) <- (B)

2. Непосредственная (IMM):

OP #d

|

|

OP |

d8 |

Операнд в команде |

|

|

|

OP |

d16h |

d16l |

Со старшего байта |

один или два байта в зависимости от разрядности регистра, участвующего в команде

ADDA #d8; (A)<-(A)+ d8

LDX #d16; (X) <- d16

3. Прямая (DIR):

OP ad8

|

|

OP |

ad8 |

Старший байт 00 |

область RAM - наиболее часто используемые данные

сокращение на 1 цикл времени

ADDA ad8; (A) <- (A)+ad8

(ad8):(ad8+1) - 16-разряядная адресация:

LDX ad8; (X) <- (ad8):(ad8+1)

STX ad8; (ad8):(ad8+1) <- (X)

4. Расширенная (EXT):

OP ad16

|

|

OP |

adh |

adl |

|

Ассемблер сам определяет ad8 либо ad16

ADDA ad16; (A)<-(A)+(ad16)

JMP ad16; (PC) <- ad16

LDX ad16; (X) <- (ad16):(ad16+1)

STX ad16; (ad16):(ad16+1) <- (X)

5. Индексная с 8-битным смещением (IX, IY):

OP of8,X

|

|

OP |

of8 |

Без знака |

- of8+(X) - исполнительный адрес

выделение к-ого элемента в таблице; к - в (X) или (Y)

ADDA of8,X; (A)<-(A)+(of8+(X))

JMP of8,X; (PC) <- of8+(X)

OP of8,Y

|

|

Префикс |

OP |

of8 |

|

- of8+(Y) - исполнительный адрес

выделение к-ого элемента в таблице; к - в (X) или (Y)

ADDA of8,Y; (A)<-(A)+(of8+(Y))

JMP of8,Y; (PC) <- of8+(Y)

6. Относительная - в командах условного перехода (REL):

OP cad

|

|

OP |

rel |

Со знаком [-128, +127] |

rel+(PC) - исполнительный адрес

ассемблер сам вычисляет rel

BCS cad; Если (C)=1, (PC)<-(PC)+rel

СИСТЕМА КОМАНД

-

Команды пересылки.

-

Команды логической обработки (ANDA, ANDB, CLR и т.д.).

-

Команды арифметической обработки (ABA, ADDA, INC, DECA, MUL и т.д.).

Команды перехода: безусловного перехода, вызова подпрограмм и обслуживания прерываний, условных переходов, по признакам при сравнении чисел без знака, при сравнении чисел со знаком, по значению битов.

4. Команды управления (STOP, WAIT).