- •10. Архитектура мк48

- •Арифметико-логическое устройство

- •Устройство управления микроконтроллера

- •Организация ввода/вывода информации

- •Память микроконтроллера

- •11. Однокристальные микроконтроллеры iMcs48 система команд

- •2. Команды логических операций

- •3. Команды передачи управления

- •12. Архитектура мк51

- •Арифметическо-логическое устройство

- •Устройство управления и синхронизации

- •13. Организация памяти в мк51

- •Сегменты памяти

- •Наращивание памяти

- •14. Организация подсистемы ввода/вывода в мк51

- •15. Организация таймеров и системы прерываний в мк51

- •Организация системы прерываний

- •16. Система команд мк51

- •Группа команд логических операций

- •Группа команд операций с битами

- •Группа команд передачи управления

- •17. Архитектура iMcs96

- •Почему iMcs96 быстрее, чем 8051?

- •20. Организация процессорного порта в iMcs96

- •21. Организация последовательного порта в iMcs96

- •Преобразование параллельного кода в последовательный

- •Протокол обмена

- •22. Система прерываний в iMcs96

- •24. Система команд iMcs96

- •25. Архитектура mc68hc05

- •Регистровая модель

- •Карта памяти для mc68hc705c8

- •Способы адресации

- •26. Архитектура mc68hc08

- •Регистровая модель

- •Способы адресации

- •Структура mc68hc11e9

- •Регистры

- •Способы адресации:

- •1. Подразумеваемая (inh):

- •2. Непосредственная (imm):

- •3. Прямая (dir):

- •5. Индексная с 8-битным смещением (IX, iy):

- •6. Относительная - в командах условного перехода (rel):

- •Система команд

Почему iMcs96 быстрее, чем 8051?

Все 232 внутренних регистра iMCS96 имеют статус " аккумуляторов " - к ним можно непосредственно применять все необходимые арифметические и логические операции. У 8051 для достижения тех же результатов зачастую необходимо выполнять дополнительные пересылки в аккумулятор и из него.

У iMCS96 можно использовать 16-разрядную внешнюю шину. Кроме того, цикл шины iMCS96 в 3-4 раза короче, чем у 8051. В результате, iMCS96 в 6-8 раз быстрее работает с внешней памятью. Отметим, что, для того, чтобы снизить стоимость изделий, можно вводить в шину циклы ожидания и сократить ее ширину до 8-ми бит; но даже в этом случае iMCS96 будет иметь преимущество в 2-3 раза.

В задачах, требующих 16- и 32-разрядных вычислений, iMCS96 примерно на порядок быстрее, поскольку имеет полноценный набор 16-разрядных арифметических инструкций.

20. Организация процессорного порта в iMcs96

Организуется на основе последовательного порта (который имеет 3 режима работы: режим 1, режим 2 и режим 3. См. билет про последовательный порт).

Многопроцессорная связь реализуется следующим образом: главный процессор находится в режиме 3, подчиненные в режиме 2.

Алгоритм передачи данных следующий:

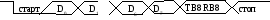

1) главный ЦП выдает адрес, при этом ТВ8 = 1.

2) следствием этого является прерывание всех подчиненных процессоров

- анализ адреса.

- перевод адресованного подчиненного процессора в режим 3

3) передача данных, ТВ8 = 0 (прерывается только адресованного подчиненного процессора)

Частота обмена в режимах 1, 2, 3:

Флаги:

TxE = 1 (TxEmpty) TSR выдан и не поступила информация в SBUF_TX – режим ожидания.

OE = 1 передача RSR → SBUF_RX затирает еще не прочитанную информацию.

FE = 1 – (Framing Error) – ошибка кадра – возникает, когда при приеме отсутствует стоп бит в ожидаемом месте. При возникновении ошибок OE или FE всю информацию необходимо передавать снова.

21. Организация последовательного порта в iMcs96

Последовательный порт реализует синхронный обмен и асинхронный обмен информации последовательным кодом. Асинхронный обмен выполнен по стандарту UART (Unversal Asynchronous Receiver / Transmitter). Аналогичен 51-ой серии; в дополнении реализован контроль четности / нечетности при передаче информации и блок генерации частоты обмена не использует общие таймеры Т1 и Т2, позволяя воспроизводить частоту более точно.

* (BH, KB, KC)

Преобразование параллельного кода в последовательный

Информация передается на вывод TxD (Transmitt Data), принимается соответственно - на входе RxD (Receive Data)

SBUF_TX – при записи,

SBUF_RX – при чтении два разных регистра.

Полнодуплексный режим – запись и чтение могут происходить параллельно

SP_CON

SP_STAT

SP_BAVD – регистр частоты

15 бит содержит константу В, 16 старший содержит clock select

Протокол обмена

Режим «0» – синхронный обмен

Р2.0 – синхронизация, выдает тактовую частоту обмена

Р2.1 – мы имеем данные (входные – выходные; прием – передача)

Данные считаются действительными на фронте тактового сигнала

Передача:

Флаг REN = 0. передача начинается, когда записан байт в регистр SBUF_TX → TSR → P2.1 → → TI = 1 записан байт в регистр SBUF_TX – информация.

Прием:

Флаг REN = 1 и RI = 0 → RSR → SBUF_RX → RI = 1– параллельный прием в последовательном коде.

В режиме 1-3 порт функционирует как асинхронный приемо-передатчик UART.

TxD – передача; RxD – прием могут происходить одновременно. Пока на выводе 1 то, ничего не происходит; передача началась, когда происходит перепад из 1 в 0.

Режим «1»

Кадр 10 битный.

Режим «2» (11-битный кадр)

Режим «3» (11- битный кадр)

У 9го бита еще больше функций

Передача данных

SBUF_TX → TSR → P2.0 → TI = 1

Прием данных

Только если PEN = 1

RSR

→SBUF_RX→RI= 1, прерывание, если