- •10. Архитектура мк48

- •Арифметико-логическое устройство

- •Устройство управления микроконтроллера

- •Организация ввода/вывода информации

- •Память микроконтроллера

- •11. Однокристальные микроконтроллеры iMcs48 система команд

- •2. Команды логических операций

- •3. Команды передачи управления

- •12. Архитектура мк51

- •Арифметическо-логическое устройство

- •Устройство управления и синхронизации

- •13. Организация памяти в мк51

- •Сегменты памяти

- •Наращивание памяти

- •14. Организация подсистемы ввода/вывода в мк51

- •15. Организация таймеров и системы прерываний в мк51

- •Организация системы прерываний

- •16. Система команд мк51

- •Группа команд логических операций

- •Группа команд операций с битами

- •Группа команд передачи управления

- •17. Архитектура iMcs96

- •Почему iMcs96 быстрее, чем 8051?

- •20. Организация процессорного порта в iMcs96

- •21. Организация последовательного порта в iMcs96

- •Преобразование параллельного кода в последовательный

- •Протокол обмена

- •22. Система прерываний в iMcs96

- •24. Система команд iMcs96

- •25. Архитектура mc68hc05

- •Регистровая модель

- •Карта памяти для mc68hc705c8

- •Способы адресации

- •26. Архитектура mc68hc08

- •Регистровая модель

- •Способы адресации

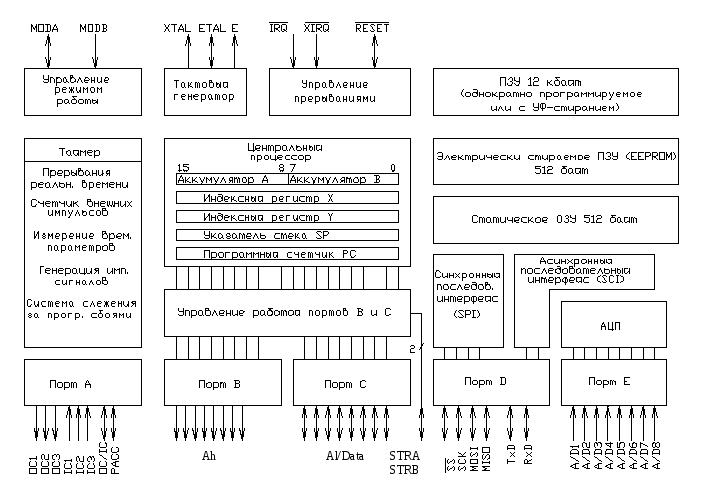

- •Структура mc68hc11e9

- •Регистры

- •Способы адресации:

- •1. Подразумеваемая (inh):

- •2. Непосредственная (imm):

- •3. Прямая (dir):

- •5. Индексная с 8-битным смещением (IX, iy):

- •6. Относительная - в командах условного перехода (rel):

- •Система команд

Структура mc68hc11e9

Режимы:

Микроконтроллер может работать в четырех режимах: однокристальный, расширенный, режим загрузки и тестовый режим. Выбор режима осуществляется во время системного сброса по состоянию входов MODB, MODA. Текущий режим работы определяется содержимым регистра HPRIO, структура которого показана ниже (этот регистр определяет также прерывание с наивысшим приоритетом).

|

|

MODB |

MODA |

Выбираемый режим |

|

|

1 |

0 |

Однокристальный режим |

|

|

1 |

1 |

Расширенный режим |

|

|

0 |

0 |

Режим загрузки |

|

|

0 |

1 |

Режим теста – используется изготовителем |

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$103C |

RBOOT |

SMOD |

MDA |

IRV |

PSEL3 |

PSEL2 |

PSEL1 |

PSEL0 |

HPRIO |

|

RESET |

- |

- |

- |

- |

0 |

1 |

0 |

1 |

|

Назначение отдельных битов регистра следующее:

- RBOOT - при установке в 1 разрешает чтение ROM загрузчика, иначе обращения по адресам программы загрузчика интерпретируются как обращения к внешней памяти. Этот бит имеет значение только в специальных режимах загрузки или теста, в остальных режимах бит RBOOT сброшен и не может быть изменен программно.

- SMOD - указывает на выбор одного из специальных режимов. Этот бит устанавливается, если во время сброса на входе MODB задан низкий уровень, в противном случае сбрасывается. Бит SMOD при работе в специальных режимах может быть сброшен программно, что позволяет изменить текущий режим работы. Программная установка бита SMOD невозможна.

- MDA - отображает состояние входа MODA во время сброса. В специальных режимах этот бит может быть изменен программно, позволяя изменить текущий режим работы, в нормальных режимах бит MDA доступен только для чтения.

- IRV - разрешает отображение процессов чтения из внутренней памяти на внешней шине данных (IRV=1). В специальных режимах этот бит может быть изменен в любой момент, в нормальных режимах - только один раз после сброса.

- PSEL3, PSEL2, PSEL1 и PSEL0 - задают маскируемое прерывание с наивысшим приоритетом.

Обращения к внутренним ROM (EPROM) и EEPROM можно запретить посредством регистра CONFIG.

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$103F |

0 |

0 |

0 |

0 |

NOSEC |

NOCOP |

ROMON |

EEON |

CONFIG |

При нулевом бите EEON запрещены обращения к EEPROM, при нулевом бите ROMON запрещены обращения к ROM (в однокристальном режиме ROM доступна независимо от значения ROMON). Кроме того, данный регистр позволяет отключать Watchdog-таймер (установкой NOCOP=1) и режим обеспечения безопасности (установкой NOSEC=1).

Четыре старших бита А15-12 начала адресов RAM и регистров задаются в регистре INIT

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$103D |

RAM3 |

RAM2 |

RAM1 |

RAM0 |

REG3 |

REG2 |

REG1 |

REG0 |

INIT |

|

RESET |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

Регистры

|

|

15 8 |

7 0 |

|

| ||||||||

|

B |

|

|

A - 8-разрядный |

| ||||||||

|

|

|

или D 16-разрядный Аккумулятор |

| |||||||||

|

|

|

X - Индексный регистр |

| |||||||||

|

|

|

Y - Индексный регистр |

| |||||||||

|

|

|

SP растет вниз, на свободную ячейку |

| |||||||||

|

|

$FFFE по Reset |

PC |

| |||||||||

|

|

|

S |

X |

H |

I |

N |

Z |

V |

C |

CCR | ||