Inverted - инвертированный

The CCU Timer Overflow interrupt flag is set when the counter changes direction at the top. For example, if TOR contains 01FFH,CCU Timer will count: …01FEH, 01FFH, 01FEH,… The flag is set in the counter cycle after the change from TOR to TOR-1.

Флаг прерывания по переполнению CCU таймера устанавливается, когда счетчик меняет направление счета в верхней точке. Например, если регистр TOR содержит 01FFH, CCU таймер будет считать: …01FEH, 01FFH, 01FEH… Флаг устанавливается в цикле счета после изменения с TOR на TOR-1.

When the timer changes direction at the bottom, in this example, it counts …,0001H, 0000H, 0001H,… The CCU Timer overflow interrupt flag is set in the counter CCUCLK cycle after the transition from 0001H to 0000H.

Когда таймер меняет направление в нижней точке, в приведенном примере, он считает … 0001Н, 0000Н, 0001Н, … Флаг прерывания по переполнению CCU таймер устанавливается в цикле счетчика CCUCLK после перехода с 0001Н на 0000Н.

The status of the TDIR2 bit in TCR20 reflects the current counting direction. Writing to this bit while operating in symmetrical mode has no effect.

Состояние бита TDIR2 в регистре TCR20 отражает текущее направление счета. Запись значения в этот бит в то время, пока идет работа в симметричном режиме, не имеет эффекта.

Alternating Output Mode

Переменный режим вывода

In asymmetrical mode, the user can program PWM channels A/B and C/D as alternating pairs for bridge drive control. By setting ALTAB or ALTCD bits in TCR20, the output of these PWM channels are alternately gated on every counter cycle. This is shown in the following figure:

В асимметричном режиме пользователь может программировать PWM каналы A/B и C/D как переменные пары для управления ….

Устанавливая биты ALTAB или ALTCD в регистре TCR20, выходы этих каналов поочередно управляются импульсами в каждом цикле счета. Это показано на следующем рисунке:

Figure 34: Alternate Output Mode

Рис.34: Переменный выходной режим

*Compare Value – величина сравнения

Timer Value – значение таймера

Table 12: Output Compare Pin Behavior

Таблица 12: Поведение выхода сравнения

|

ОСМх11 (CCCRx.1) |

ОСМх01 (CCCRx.0) |

Поведение выхода сравнения | ||

|

Основной режим таймера |

Асимметричный режим PWM |

Cимметричный режим PWM | ||

|

0 |

0 |

Выход сравнения не доступен. При включенном питании это значение по умолчанию, контакты настроены как входы | ||

|

0

|

1 |

Устанавливается, когда выполняется операция сравнения. Снимается при совпадении сравниваемых величин2. |

Неинвертированный PWM. Устанавливается при совпадении сравниваемых величин. Снимается при переполнении таймера2. |

Неинвертированный PWM. Снимается при совпадении сравниваемых величин. Устанавливается при совпадении сравниваемых величин в режиме обратного счета2. |

|

1 |

0 |

Инвертированный PWM. Снимается при совпадении сравниваемых величин. Устанавливается при переполнении таймера CCU2. |

Инвертированный PWM. При совпадении сравниваемых величин в режиме прямого счета – устанавливается, в режиме обратного счета – снимается2. | |

|

1 |

1 |

| ||

|

Примечания:

2. в цикле CCUCLK, следующем после того, как определенное событие (описанное в таблице) имело место | ||||

Synchronized PWM register update

Обновление синхронизированного PWM регистра

When the OCRx registers are written, a built in mechanism ensures that the value is not updated in the middle of a PWM pulse. This could result in an odd-length pulse. When the registers are written, the values are placed in two shadow registers, as is the case in basic timer operation mode. Writing to TCOU2 will cause the contents of the shadow registers to be updated on the next CCU Timer overflow. If OCRxH and/or OCRxL are read before the value is updated, the most currently written value is read.

При записи регистров OCRx, встроенный механизм обеспечивает то, что значение не будет изменено в середине импульса PWM. Это могло бы привести к импульсу нечетной длины. Когда записываются регистры, значения помещаются в регистры теневой памяти, как и в основном режиме работы таймера. Запись значения в TCOU2 вызовет то, что содержимое регистров теневой памяти будет изменено при следующем переполнении CСU таймера. Если регистры ОCRxH и/или ОCRxL читаются перед тем, как значения обновлены, то будет считано наиболее позднее записанное значение.

Halt

Остановка

Setting the HLTEN bit in TCR20 enables the PWM Halt Function. When halt function is enabled, a capture event as enabled for the Input Capture A pin will immediately stop all activity on the PWM pins and set them to a predetermined state defined by FCOx bit. In PWM Mode, the FCOx bits in the CCCRx register hold the value the pin is forced to during halt. The value of the setting can be read back. The capture function and the interrupt will still operate as normal even if it has this added functionality enabled. When the PWM unit is halted, the timer will still run as normal. The HLTRN bit in TCR20 will be set to indicate that a halt took place. In order to re-activate the PWM, the user must clear the HLTRN bit. The user can force the PWM unit into halt by writing a logical one to HLTRN bit.

Установка бита HTLEN в регистре TCR20 включает функцию остановки PWM. Когда эта функция разрешена, событие по вводу, разрешенное для входного контакта А, немедленно остановит любую деятельность на конатактах PWM и установит их в предопределенное состояние, определенное битом FCOx. В режиме PWM, биты FCOx и регистре CCCRx содержат значение контакта, записанные туда во время остановки. Установленное значение может быть считано. Функция ввода и прерывания все еще будут работать, как обычное событие, если эта добавочная функция разрешена. Когда остановится блок PWM, таймер будет все еще работать как обычно. Бит HLTRN в регистре TCR20 будет установлен, чтобы показать, что остановка имела место. Для того, чтобы возобновить работу PWM, пользователь должен установить бит HLTRN в ноль. Пользователь может вызвать остановку блока PWM путем записи логической единицы в бит HLTRN.

PLL operation

PLL операция

The PWM module features a Phase Locked Loop that can be used to generate a CCUCLK frequency between 16 MHz and 32 MHz. At this frequency the PWM module provides ultrasonic PWM frequency with 10-bit resolution provided that the crystal frequency is 1 MHz or higher (The PWM resolution is programmable up to 16 bits by writing to TOR2H:TOR2L). The PLL is fed an input signal of 0.5 - 1 MHz and generates an output signal of 32 times the input frequency. This signal is used to clock the timer. The user will have to set a divider that scales PCLK by a factor of 1-16. This divider is found in the SFR register TCR21. The PLL frequency can be expressed as follows:

PLL frequency = PCLK / (N+1)

Where: N is the value of PLLDV3:0.

Since N ranges in 0 - 15, the CCLK frequency can be in the range of PCLK to PCLK/16.

Модуль PWM напоминает PLL, который может быть использован, чтобы генерировать CCUCLK частотой от 16 МГц до 32 МГц. В этих частотах модуль PWM обеспечивает ультразвуковую PWM частоту с 10-разрядным разрешением, обеспечиваемым частотой кварцевого резонатора – 1 МГц и выше (разрешение PWM программируется вплоть до 16 бит записью в TOR2H:TOR2L). PLL питается от входного сигнала частотой 0,5-1 МГц и генерирует выходной сигнал частотой, большей входной в 32 раза. Этот сигнал используется для тактирования таймера. Пользователь должен будет установить делитель, который будет масштабировать (делить) PCLK на коэффициент от 1 до 16. Этот делитель основывается на SFR регистра TCR21. Частота PLL может быть выражена следующим образом:

Частота PLL = PCLK / (N+1)

Где N – значение PLLDV3:0

Т.к. N изменяется от 0 до 15, то частота CCLK может изменяться в пределах от PCLK до PCLK/16.

Figure 35: CCU Control register 1 Рис.35: Регистр управления CCU

*

|

Бит |

Символ |

Функция |

|

TCR21.7

TCR21.6-4

TCR21.3-0 |

TCOU2

-

PLLDV.3-0 |

В основном режиме работы таймера , запись ‘1’ в TCOU2 приведет к тому, что значения будут сохраняться сразу же, а значение TCOU2 всегда будет читаться как ‘0’. В режиме PWM запись ‘1’ в TCOU2 вызовет обновление содержимого регистров теневой памяти при следующем переполнении CCU таймера. Пока регистр-защелка будет находится в ожидании, TCOU2 будет читаться как ‘1’ и будет возвращать ‘0’, когда фиксация осуществиться. TCOU2 также контролирует фиксацию регистров выходного сравнения OCRAx, OCRBx и OCRCx.

Зарезервированы для дальнейшего использования. Не должны быть установлены в ‘1’ пользовательской программой.

Частотный делитель PLL |

Setting the PLLEN bit in TCR20 starts the PLL. When PLLEN is set, it will not read back a one until the PLL is in lock. At this time, the PWM unit is ready to operate and the timer can be enabled. The following start-up sequence is recommended.

1. Set up the PWM module without starting the timer.

2. Calculate the right division factor so that the PLL receives an input clock signal of 500 kHz - 1 MHz. Write this value to PLLDV.

3. Set PLLEN. Wait until the bit reads one.

4. Start the timer by writing a value to bits TMOD21, TMOD20.

When the timer runs from the PLL, the timer operates asynchronously to the rest of the microcontroller. Some restrictions apply:

• The user is discouraged from writing or reading the timer in asynchronous mode. The results may be unpredictable.

• Interrupts and flags are asynchronous. There will be delay as the event may not actually be recognized until some CCLK cycles later (for interrupts and reads).

Установка бита PLLEN в регистре TCR20 запускает PLL. Когда бит PLLEN установлен, он не возвращает единицу обратно до тех пор, пока PLL заблокирован. В это время блок PWM готов к работе и таймер может быть доступен. Рекомендуемая последовательность пуска следующая:

Установить модуль PWM без старта таймера.

Вычислить правильный коэффициент деления так, чтобы PLL получил входной тактовый сигнал в диапазоне частот от 500 КГц до 1 МГц. Записать это значение в PLLDV.

Установить PLLEN. Подождать, пока бит прочитается как единица.

Запустить таймер, записав значения в биты TMOD21, TMOD20.

Когда таймер работает от PLL, таймер действует асинхронно по отношению к микроконтроллеру. Применяются некоторые ограничения:

Пользователь не может записать или считать значение таймера в асинхронном режиме. Результаты могут быть непредсказуемыми.

Прерывания и флаги асинхронны. В случае, если событие не распознано, будет задержка на несколько циклов CCLK (для прерывания и флагов).

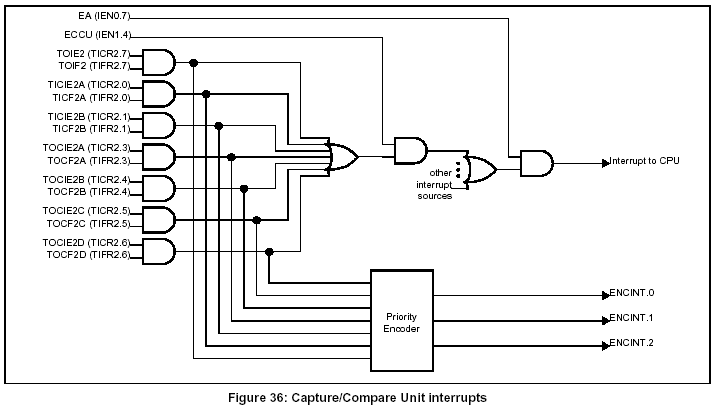

CCU interrupt structure

Схема прерывания CCU

There are seven independent sources of interrupts in the CCU: timer overflow, captured input events on Input Capture blocks A/B, and compare match events on Output Compare blocks A through D. One common interrupt vector is used for the CCU service routine and interrupts can occur simultaneously in system usage. To resolve this situation, a priority encode function of the seven interrupt bits in TIFR2 SFR is implemented (after each bit is AND-ed with the corresponding interrupt enable bit in the TICR2 register). The order of priority is fixed as follows, from highest to lowest:

TOIF2

TICF2A

TICF2B

TOCF2A

TOCF2B

TOCF2C

TOCF2D

В CCU имеется семь независимых источников прерываний: переполнение таймера, события по вводу на входных блоках A/B и события по сравнению на выходных блоках от A до D. Один общий вектор прерывания используется для обслуживающей программы CCU, и прерывания в системе могут возникнуть одновременно. Чтобы разрешить эту ситуацию, имеется функция кодирования приоритетов для семи битов прерываний в TIFR2 SFR (каждый бит объединяется по логическому И с соответствующим битом разрешения прерывания в регистре TICR2). Порядок приоритетов фиксированный, от самого высокого приоритета до самого низкого:

TOIF2 TICF2A TICF2B TOCF2A TOCF2B TOCF2C TOCF2D

When any of the interrupt flags are set in the TIFR2 register, the three bits of output of the priority encoder (see Figure 36) will be available in CCU Timer Interrupt Status Encode (TISE2) register. Note that in order to generate an interrupt, the interrupt enable for the specific source, the CCU global interrupt enable bit (ECCU), and the global interrupt enable bit (EA), all need to be set,

Когда какой-либо из флагов прерывания установлен в регистре TIFR2, три бита на выходе кодера приоритетов (см.рис.36) будут доступны в регистре кодирования состояния прерываний таймера CCU. Отметим, что для того, чтобы сгенерировать прерывание, разрешение прерывания от определенного источника, общий бит разрешения прерывания CCU и общий бит разрешения прерывания (EA) – все должны быть установлены.

An interrupt service routine for the CCU can be as follows:

1. Read the priority-encoded value from the TISE2 register to determine the interrupt source to be handled.

2. After the current (highest priority) event is serviced, write a ‘0’ to the corresponding interrupt flag bit in the TIFR2 register to clear the flag.

3. Read the TISE2 register. If the priority-encoded interrupt source is ‘000’, all CCU interrupts are serviced and a return from interrupt can occur. Otherwise, return to step 2 for the next interrupt.

Программа обслуживания прерывания для CCU может быть следующей:

Считать зашифрованное значение приоритета из регистра TISE2, чтобы определить, к какому источнику прерывания необходимо обратиться.

После того, как текущее (имеющее более высокий приоритет) событие выполнено, записать ‘0’ в соответствующий бит флага прерывания и регистре TIFR2, чтобы снять флаг.

Прочитать регистр TISE2. Если источник прерывания с закодированным приоритетом ‘000’, это значит, что все прерывания CCU обслужены и может произойти возвращения из прерывания. В другом случае, вернуться к шагу 2 для следующего прерывания.

Figure 36: Capture/Compare Unit interrupts

Рис. 36: Блок прерываний

*Other interrupt source – другие источники прерывания